#### A Multidrop Channel Access supporting MII Interface for 10BASE-T1S

#### Jan 17, 2018

#### Ahmad Chini, Mehmet Tazebay Broadcom Limited

#### Foreword

- IEEE *Draft* P802.3cg/D1.0, December 2017 provides for multidrop network capability. In Clause 148, PLCA is specified as an option to improve latency and throughput over CSMA/CD.

- PLCA implementation requires modification of reconciliation sublayer and relies on CSMA/CD signals to operate. PLCA is designed to avoid physical collisions associated with CSMA/CD.

- Original 10Mbps CSMA/CD was designed to operate over coaxial cables with noise levels not as severe as in automotive applications. While CSMA/CD may work well for some applications, it's performance under extreme noise levels (more than 100V/m over UTP cables) and low emission requirement of automotive environments is not established.

- CSMA/CD aggregate throughput is limited to 10Mbps when operating over 10Mbps MII interface, even if the PHY allows for aggregate throughput of 20Mbps to support near full duplex 10Mbps in P2P configuration.

### Foreword (cntd.)

- The existing automotive grade Ethernet switches with standard MII interface do not benefit from potential PLCA advantages.

- An alternative multidrop channel access mechanism is discussed in this presentation that provides for the followings;

- 1. PHY Interface is provided at standard MII with no modification to reconciliation sublayer

- 2. Channel access is scheduled relative to a Master preamble with strong EMC performance (does not rely on CSMA/CD)

- 3. Allows aggregated throughput of 20Mbps while running MII at 10Mbps

- 4. Provides for optional OAM field

- 5. Provides capability to tailor channel access to particular Bus designs and applications

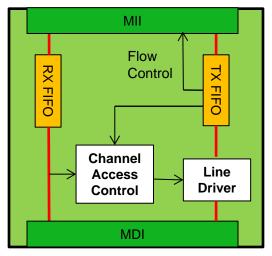

### PHY Block diagram and MAC interface

- Data is transmitted and received at the same time and at 10Mbps on MII regardless of activities on MDI.

- Line driver is activated for data transmission on MDI per channel access control mechanism.

- If traffic received through MII exceeds Bus capacity, TX FIFO is filled up and Flow Control instructs MAC to defer the traffic.

- Using FIFO, while MII runs at 10Mbps, MDI may run at higher rate of 20Mbps or more.

10Mbps (with flow control)

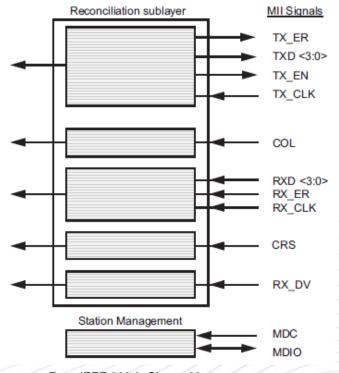

### Flow Control using CRS at MII

• From IEEE 802.3, Clause 22

Version 1.0

- To use as Flow Control, CRS may be set in the PHY to defer MAC transmission when TX FIFO in the PHY is near full and can not receive another full size packet.

- Given TX FIFO, CRS is not set based on copper side transmit or receive activity and/or availability. MAC may send and receive data to/from PHY at any time unless TX FIFO is full.

- When peak data traffic is within the Bus bandwidth, CRS may not be set.

- No modification to Reconciliation sublayer is required.

#### Other options for Flow Control

- Set interface to full duplex and generate PAUSE packets (see 802.3, Annex 31B) inside PHY for flow control.

- Set interface to full duplex and use larger interpacket gap (IPG) for nodes with known lower bandwidth (see IPG stretch in clause 4).

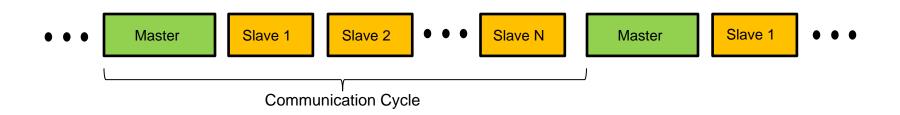

#### **Channel Access Control**

- For Multidrop networks, one node is set to Master and all other nodes to Slave.

- Communication cycles on MDI are synchronized to a Master transmitted preamble.

- Access time for each node is set by Master for each communication cycle.

- Using an OAM channel, Slaves may request more or less access time for the next communication cycle.

- Access time assignment policies are configurable through PHY management interface, providing options for low latency (short packets) and throughput requirements as per Bus design.

#### **Communication Cycle**

- Master has to transmit in every Communication Cycle but not all Slaves need to transmit

- Master sets transmit opportunities for individual Slaves.

- Slaves may or may not take the opportunity to transmit and may request more time.

#### **PHY Frame Format**

| Preamble | OAM | Data |

|----------|-----|------|

|----------|-----|------|

- Preamble is a sequence with good autocorrelation to help EMC

- OAM provides for Operation, Administration and Maintenance information

- Data is the content received from MAC

- A PHY may transmit OAM alone with no Data

- Master OAM field include transmit opportunities for Slaves

#### OAM Field

| Master | OAM Length | Info | T <sub>0</sub> | T <sub>1</sub> | $T_2$ | • • | • | Τ <sub>κ</sub> | Other OAM | FCS |

|--------|------------|------|----------------|----------------|-------|-----|---|----------------|-----------|-----|

| Slave  | OAM Length | Info | T <sub>n</sub> | Other OAM      |       | FC  | S |                |           |     |

OAM Length: 8-bit, total number of OAM bytes in a frame

**Info:** 8-bit, first bit Master/Slave indication, second bit indicates if frame carries data, next 5-bit indicates number of nodes with assigned Transmit Opportunity in current cycle **Tn:** 16-bit, first 5 bits indicate PHYAD, next 11 bits show Transmit Opportunity in Bytes

- In Master frame,  $T_0$  to  $T_k$  are the assigned Transmit Opportunity,  $T_0$  is for Master

- In Slave frame, T<sub>n</sub> is the requested Time for the next Communication Cycle

- Transmit Opportunity includes Inter Frame Gap of 12 Bytes

**Other OAM:** Optional (TBD) field used to communicate information like transmit delay for TSN, remote register read/write, recipient PHYAD, link quality, packet segmentation/aggregation, provision for packets shorter than 64B, partial networking, etc. **FCS:** 4-Byte Frame Check Sequence for OAM bits

### **Example Channel Access Configuration**

- The channel access is configurable in Master PHY for a particular Bus application.

- Assuming 20Mbps MDI data rate, clocked up 25% to allow for OAM, latency is less than 0.1ms when only one node has content to send.

- With random traffic not exceeding aggregate of 20Mbps, latency in ms range is expected.

- In sensor applications, if the Ethernet packets are kept short and fixed size, latency may be kept below 1ms.

- In applications with status reading and control, lower latency may be achieved giving more transmit opportunities to Master.

## Summary

- An alternative Channel Access mechanism presented for 10BASE-T1S multidrop with automotive applications in mind

- The suggested method allows interface with existing Ethernet switch products with MII interface (reduced pin interfaces other than MII are not precluded)

- Aggregate throughput more than 10Mbps and additional OAM is supported

- Access is scheduled to avoid collision and is configurable to meet particular applications

- Channel access is scheduled on a preamble with strong EMC performance to enable more reliable automotive applications

- The suggested method allows for up to 32 nodes as per IEEE PHYAD filed

- Compatible with partial networking, allows sleep Slave nodes

- Details including additional OAM use are subject to future work

# Thank You!