# A Proposed ADC-DSP Receiver Reference Model for COM (Update)

Yuchun Lu, Huawei Pengchao Zhao, Huawei Weiyu Wang, Huawei Yan Zhuang, Huawei Liyang Sun, Huawei

IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

#### **Table of Contents**

- Receiver Reference Models

- Mix-Signal Receiver (Annex 93A, without RX FFE)

- Mix-Signal-Like Receiver Model (under discussion in COM2.41)

- The ADC-DSP Receiver Model (Proposed)

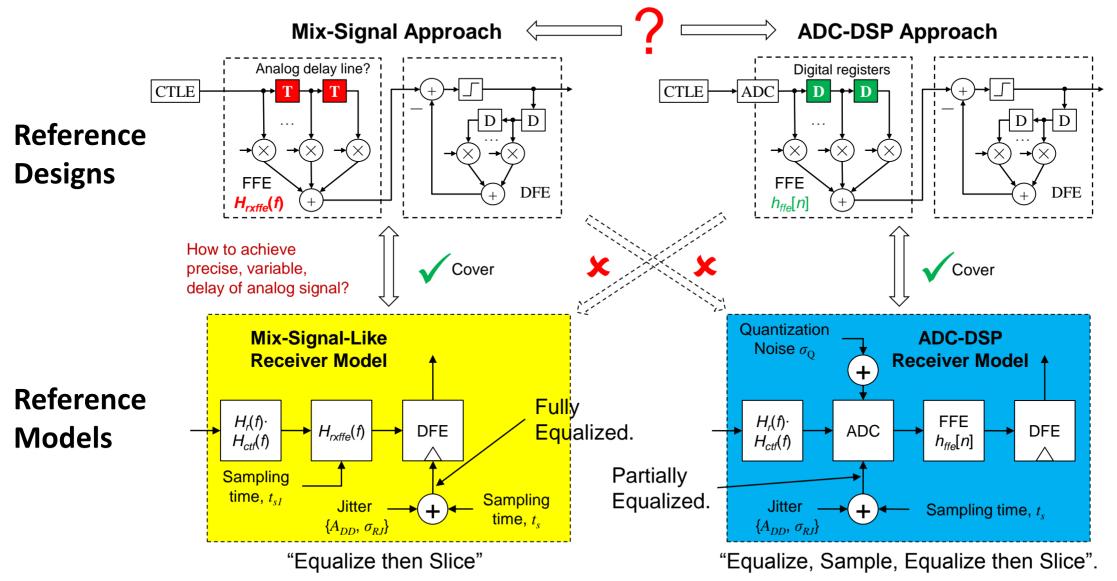

- Comparison of "Mix-Signal-Like" Model and "ADC DSP" Model

- "Parameters" and "Formulas" of the Proposed ADC-DSP Receiver Model

- Suggestions and Future Work

- Acknowledgement

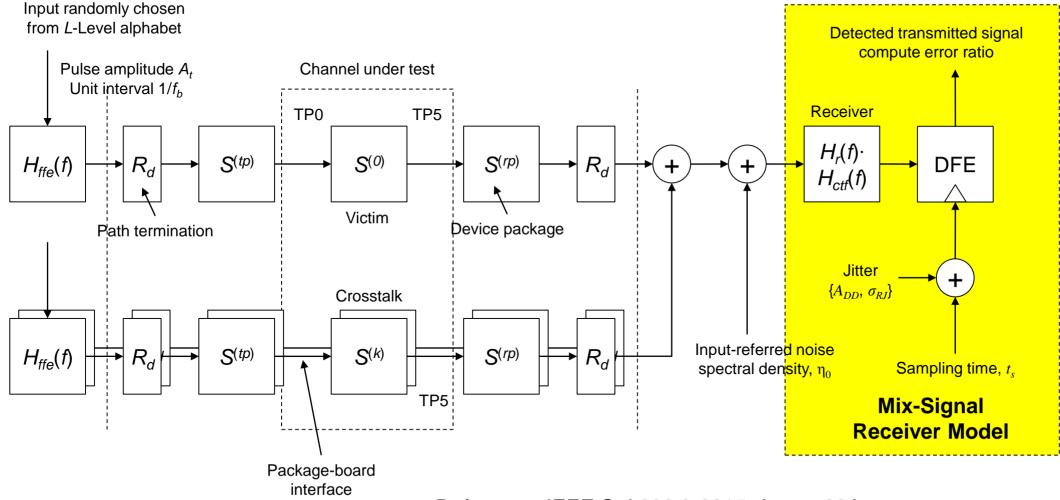

#### What do we have now?-- Mix-Signal Receiver Model

The model exactly match the reference design.

Reference: IEEE Std 802.3-2015, Annex 93A

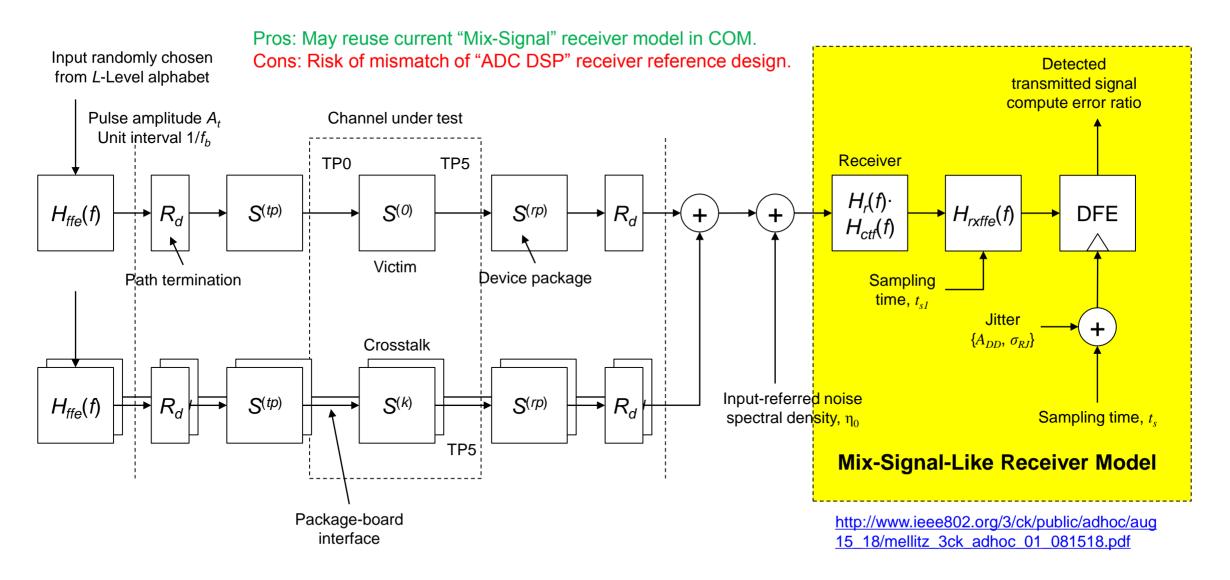

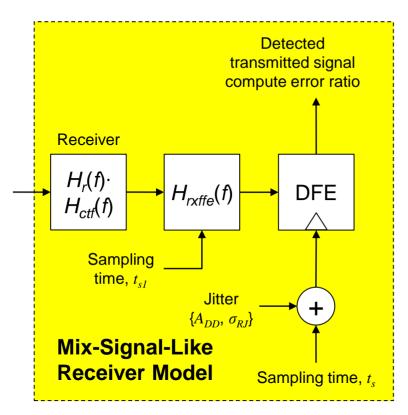

#### Model under discussion: Mix-Signal-Like Receiver Model (COM2.41)

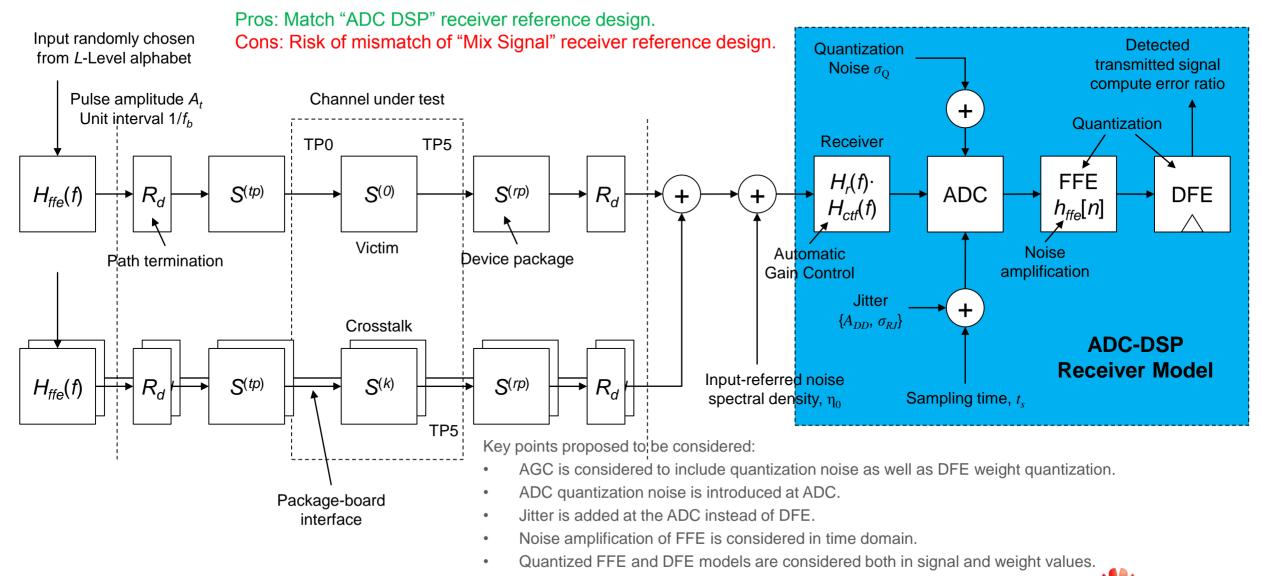

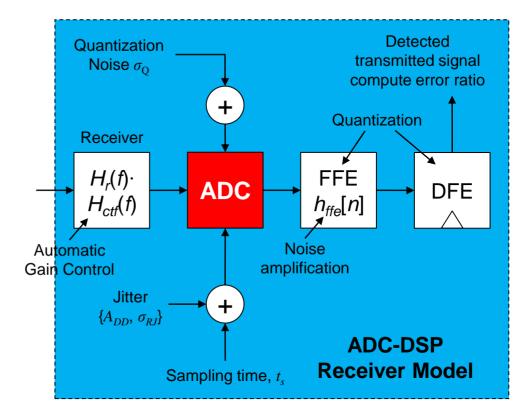

#### **Proposed ADC-DSP Receiver Model**

BUILDING A BETTER CONNECTED WORLD

5

HUAWE

#### Key points proposed to be considered

- ADC quantization noise is not considered.

- Automatic gain control is not explicitly considered.

- Quantization of FFE&DFE are considered in analog way.

- Jitter is added at DFE.

- RX FFE is modeled in continuous frequency domain.

- ADC quantization noise is considered.

- Automatic gain control is considered.

- Quantization of FFE&DFE are considered in digital way.

- Jitter is added at ADC instead of DFE.

- RX FFE is modeled in discrete time domain.

#### The proposed ADC DSP receiver model is not implementation-oriented, but considers a minimum set of parameters.

#### **Recommend Explicit Model: Symbols should have Specific Meanings**

#### **Parameters in Proposed ADC DSP Receiver Model**

| Parameter                                                                      | Symbol               | Units | Equivalent<br>COM2.41 parameters | Values | Units                             | Mapping to<br>ADC DSP model                                                                                  |

|--------------------------------------------------------------------------------|----------------------|-------|----------------------------------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------|

| ADC input amplitude                                                            | A <sub>adc</sub>     | mV    | Not considered                   | N.A.   | N.A.                              | Not defined in COM2.41                                                                                       |

| ADC resolution                                                                 | N <sub>adc</sub>     | bit   | Not Considered                   | N.A.   | N.A.                              | Not defined in COM2.41                                                                                       |

| FFE weight bit number                                                          | $N_{ m ffe}$         | bit   | ffe_tap_step_size                | 0.01   | Normalized to<br>main tap=1       | $N_{\rm ffe} = log2\left(rac{2}{0.01} ight) = 7.6$ bits<br>$N_{\rm ffe} = 7$ means $rac{1}{64}$ step size. |

| DFE weight bit number                                                          | N <sub>dfe</sub>     | bit   | N_b_step                         | 0.0115 | Normalized?<br>Equivalent to AGC? | $N_{\rm dfe} = log2\left(\frac{2}{0.0115}\right) = 7.4$ bits?                                                |

| FFE Post Tap Number*                                                           | $N_{\rm post_{ffe}}$ |       | ffe_post_tap_len                 | 32     |                                   | Same                                                                                                         |

| FFE Pre Tap Number                                                             | N <sub>pre_ffe</sub> |       | ffe_pre_tap_len                  | 3      |                                   | Same                                                                                                         |

| DFE Tap Number                                                                 | N <sub>b</sub>       | UI    | N <sub>b</sub>                   | 1      | UI                                | Same                                                                                                         |

| * The FFE Tap Number is changed to FFE Post Tap Number to align with COM 2.41. |                      |       |                                  |        |                                   |                                                                                                              |

• No new "parameters" are introduced, except for A<sub>adc</sub> and N<sub>adc</sub> which are related to "ADC quantization noise".

- ADC quantization noise should be considered in ADC DSP receiver. It is too optimistic to ignore ADC quantization noises.

- "The famous 3dB minimum was allowance for implementation 'penalties' " not for modeling "penalties".

- Modeling should be accurate. The "penalties" should be allocated to the variation of A<sub>adc</sub>, N<sub>adc</sub>, N<sub>ffe</sub>, N<sub>dfe</sub>, etc. for different ADC DSP receiver implementation.

- The FFE&DFE weight number  $N_{\rm ffe}$  &  $N_{\rm dfe}$  are equivalent to the "ffe\_tap\_step\_size" and "N\_b\_step".

- No difference in the difficulty of consensus building. But *N*<sub>ffe</sub> & *N*<sub>dfe</sub> are the natural language for ADC DSP receivers.

- N<sub>ffe</sub> & N<sub>dfe</sub> make a lot of sense to ADC DSP receivers. They are directly mapped to the receiver architecture.

- Even with "Mix-Signal-Like" model, It is hard to define "N\_b\_step" without defining automatic gain control (AGC).

٠

#### **Formulas for ADC-DSP Reference Receiver Model**

be added/amended to support ADC-DSP model, while all the others can be reused.

$h_J(n) = \frac{h(t_s + (n+1/M)T_b) - h(t_s + (n-1/M)T_b)}{2/M}$  $\sigma_X^2 = \frac{L^2 - 1}{2(L-1)^2}$  $\sigma_{in}^2 = \sigma_{TX}^2 + \sigma_{XT}^2 + \sigma_N^2$ , scaled by the AGC gain.  $\sigma_{TX}^2 = \left[h^{(0)}(t_s)\right]^2 \cdot 10^{-SNR_{TX}/10}$  $\sigma_0^2 = \frac{1}{2} \left( \frac{A_{\text{adc}}}{2N_{\text{adc}} - 1} \right)^2 \qquad \Box$  $\sigma_{ISI}^2 = \sigma_X^2 \cdot \sum_i h_{ISI}^2(i),$  $\sigma_I^2 = \left(A_{DD}^2 + \sigma_{RI}^2\right) \cdot \sigma_X^2 \cdot \sum_n h_I^2(n)$  $[\sigma_m^k]^2 = \sigma_X^2 \sum_n [h^{(k)} ((m/M + n)T_h)]^2$  $\sigma_{XT}^2 = \sum_{k=1}^{K-1} \left[ \sigma_i^k \right]^2$  $\alpha_{\rm FFE} = \sqrt{\sum_i h_{ffe} [i]^2}$  $\sigma_N^2 = \eta_0 \int_0^\infty \left| H_r(f) \cdot H_{ctf}(f) \right|^2 df$  $A_{ni}^2 = \alpha_{\text{FFF}}^2 \cdot \left(\sigma_{\text{in}}^2 + \sigma_0^2 + \sigma_l^2\right) + \sigma_{lSI}^2$  $FOM = 20 \cdot \log_{10} \left( \frac{A_s}{A_{mi}} \right)$

| ADC resolution                                                                      | 5    | 6    | 7    | 8    |  |  |

|-------------------------------------------------------------------------------------|------|------|------|------|--|--|

|                                                                                     |      |      |      |      |  |  |

| $\sigma_{ m Q}$ in mV<br>@ $A_{ m adc}$ =200mV                                      | 3.72 | 1.83 | 0.91 | 0.45 |  |  |

| Upper bound of $\sigma_N$ :                                                         |      |      |      |      |  |  |

| $\sqrt{8.2 \times 10^{-9} \text{V}^2/\text{GHz} \times 56\text{GHz}} \times 10^3 =$ |      |      |      |      |  |  |

| 0.6776mV                                                                            |      |      |      |      |  |  |

| Quantization noise cannot be neglected                                              |      |      |      |      |  |  |

All the formulas in "black" are from Annex 93A.

#### A Comparison List of "Mix-Signal-Like" Model and "ADC DSP" Model

|                                         | Mix-Signal-Like Model<br>(COM2.41)                   | ADC-DSP Model                                                |  |

|-----------------------------------------|------------------------------------------------------|--------------------------------------------------------------|--|

| Applicable receiver<br>architecture     | Mix-Signal Receiver                                  | ADC DSP Receiver                                             |  |

| ADC quantization                        | Not Considered                                       | Considered                                                   |  |

| Sampling phase and Jitter consideration | Sample & Add @ DFE<br>Match Mix-Signal Receiver      | Sample & Add @ ADC<br>Match ADC-DSP Receiver                 |  |

| Quantization of<br>FFE&DFE Weight       | Match the language of<br>Mix-Signal Design ('step')  | Match the language of DSP Design ('bit number')              |  |

| # of new parameters                     | 5<br>(without considering ADC<br>quantization noise) | 7<br>( $A_{adc}$ & $N_{adc}$ are for ADC quantization noise) |  |

| # of added/amended<br>formulas          | ?                                                    | 4                                                            |  |

| Implementation<br>Independent?          | Yes                                                  | Yes                                                          |  |

### Suggestions and Future Work

- What receiver types do we need? "Mix-Signal", "ADC-DSP" or both? Select the corresponding reference model for a specific architecture. Mix-up things will lead to confusion even though they may be close to each other in mathematics.

- "Mix-Signal Model" for "Mix-Signal Receiver"

- "ADC DSP Model" for "ADC DSP Receiver"

- For ADC-DSP Receiver model

- ADC Quantization noise should be considered.

- No "new" parameters are introduced, except for DSP language alignments.

- The problem will be simplified because the "language" is aligned.

- "number of bits" is common language for DSP designers.

- "step" will lead to fractional bit number which is very confusing.

- The workload of proposed ADC-DSP model is fair.

- Future Work

- Recommend to do consensus building on the type of receivers.

- Sensitive study of parameters extracted from the ADC-DSP Receiver Model.

- Comparative study of "ADC-DSP Receiver Model" and "Monte-Carlo IBIS/AMI model"

#### Acknowledgement

• We appreciate people reviewed and commented on this model and are looking forward to working together with the group to improve the COM model.

## JOIN US IN BUILDING A BETTER CONNECTED WORLD

# THANK YOU