# Backplane Discussion Direction Check

Beth Kochuparambil, Cisco

Supporters: Howard Heck, Intel Dave Chengson, Juniper Arturo Pachon, TE Brandon Gore, Samtec Kent Lusted, Intel

# Backplane Analysis – 3 Step Approach

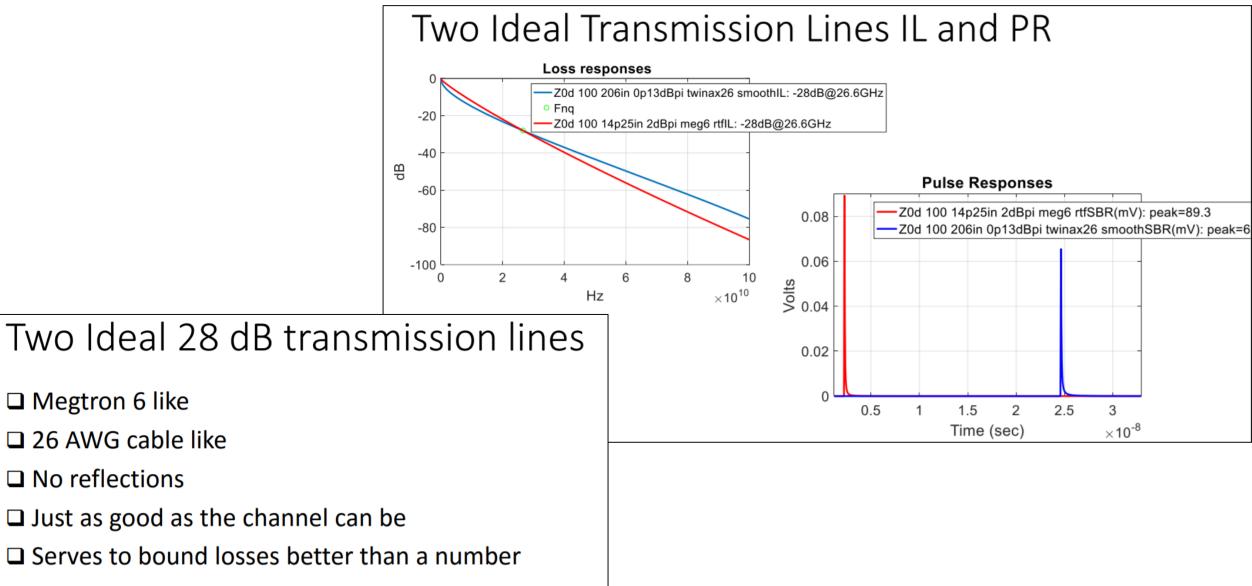

### 1. Ideal channels $\rightarrow$ High level sanity

"Are we in the ballpark?"

"Is the TX/RX architecture appropriate at this data rate?"

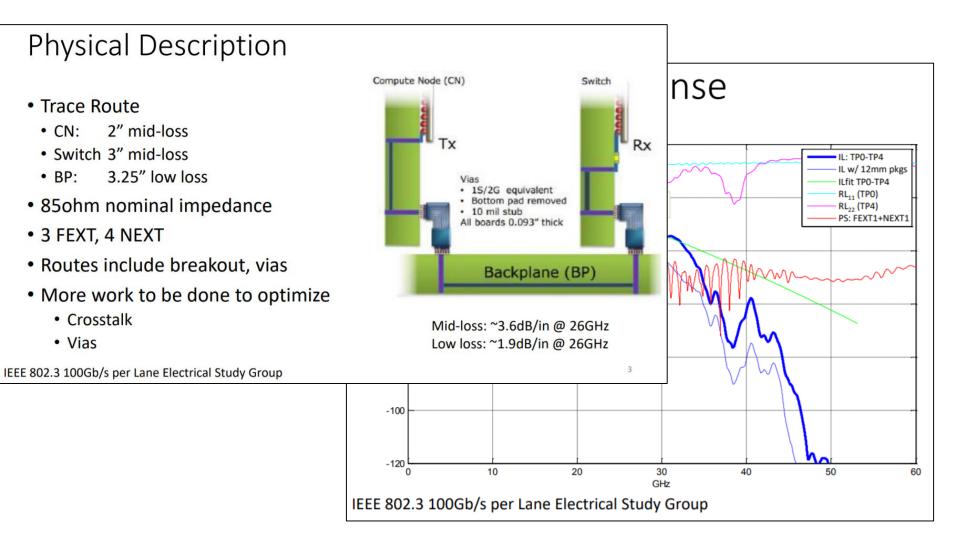

## 2. Reasonable channels $\rightarrow$ Coming into reality

"Does the architecture still hold?" "What are reasonable settings?" "Start holding some 'tools' still"

3. Many, many, many channels  $\rightarrow$  Fine tune and validation

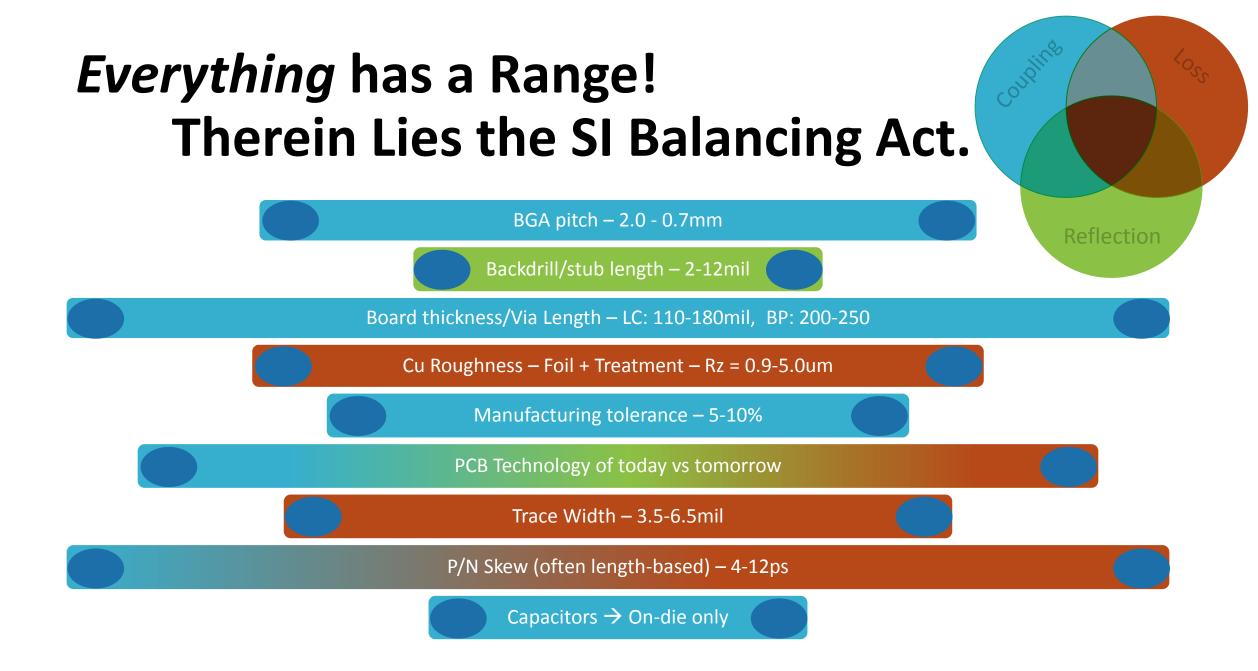

# **System Implementation**

- Loss only PART of the puzzle

- BGA breakout

- Connector footprint

- Manufacturing tolerance

### • Balancing act with *multiple* axis

- Architecture

- System Complexity

- Signal Integrity

- Design Cost

- Etc

## • MANY causes of Signal Integrity effects

# **Identifying Worst Case**

- Various application spaces rely on different constraints

- Likely not to have the worst of all metrics at once

- Margins are tight

- Various causes of signal integrity effects

- Concept of "Golden Channel" is unrealistic

#### • Working to select 3-5 channels that MUST work

- Similar to "Golden Channel" concept

- Test multiple boundaries

- Can include more, but if you're only doing a few...

# Call to Action

### 1. Ideal channels $\rightarrow$ High level sanity

"Are we in the ballpark?"

"Is the TX/RX architecture appropriate at this data rate?"

# 2. Reasonable channels $\rightarrow$ Coming into reality January - March

"Does the architecture still hold?" "What are reasonable settings?" "Start holding some 'tools' still"

3. Many, many, many channels  $\rightarrow$  Fine tune and validation Past & Present

**After Baselines**

# Questions?

# Backup

7 channels previously submitted Channels by Upen this meeting Channels by Howard this meeting

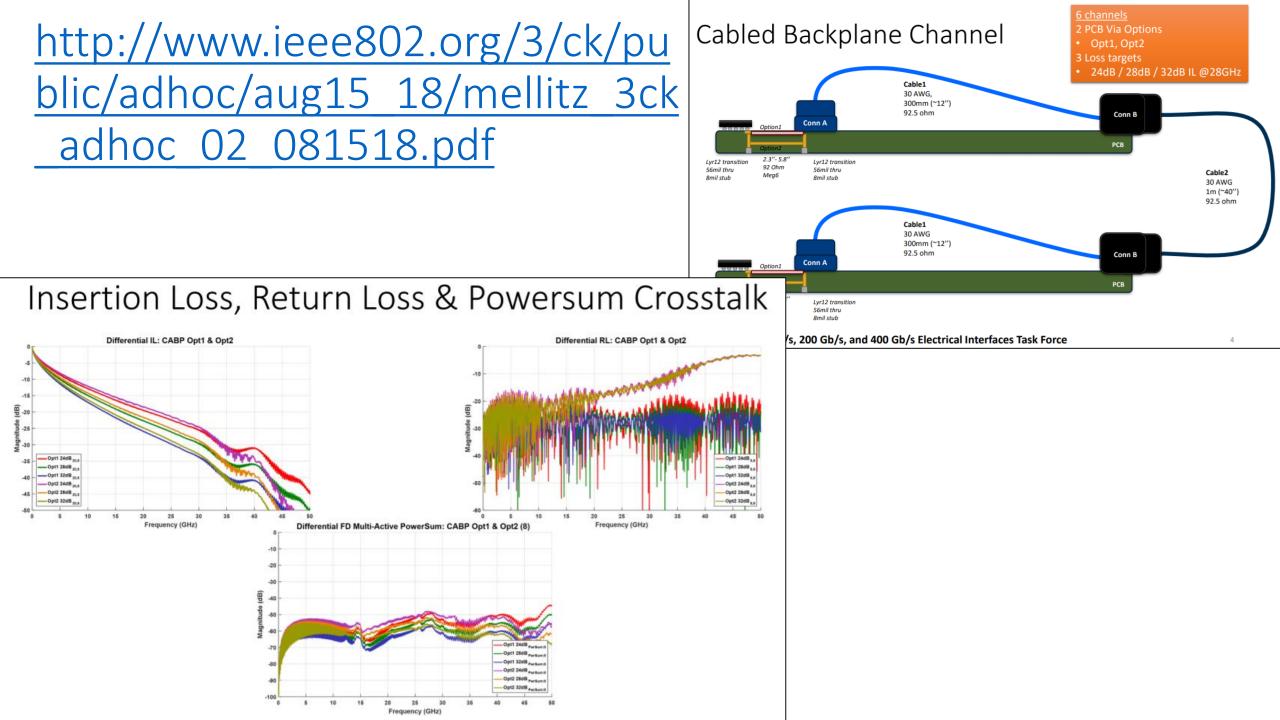

## http://www.ieee802.org/3/ck/public/adhoc/july25 18/ mellitz 3ck adhoc 02 072518.pdf

# http://www.ieee802.org/3/100GEL/public /18 03/zambell 100GEL 01a 0318.pdf

10" trace

# A connector was measured on to de-embedded to be used in this A 10" simulated trace was concathe de-embedded connector & for channel length of 20".

- Board material is Doosan DS74

- Dk = 3.25 & Dk = 0.0015

- Board thickness = 77 mils

- Trace width \ spacing = 9.6 \ 6.5 mils

- This is the material used in the test be traces.

- Touchstone files go from 10 MH steps

zambell\_100GEL\_01a\_0318 Page 3

**Details**

# <u>http://www.ieee802.org/3/100GEL/publi</u> <u>c/18 01/heck 100GEL 01 0118.pdf</u>

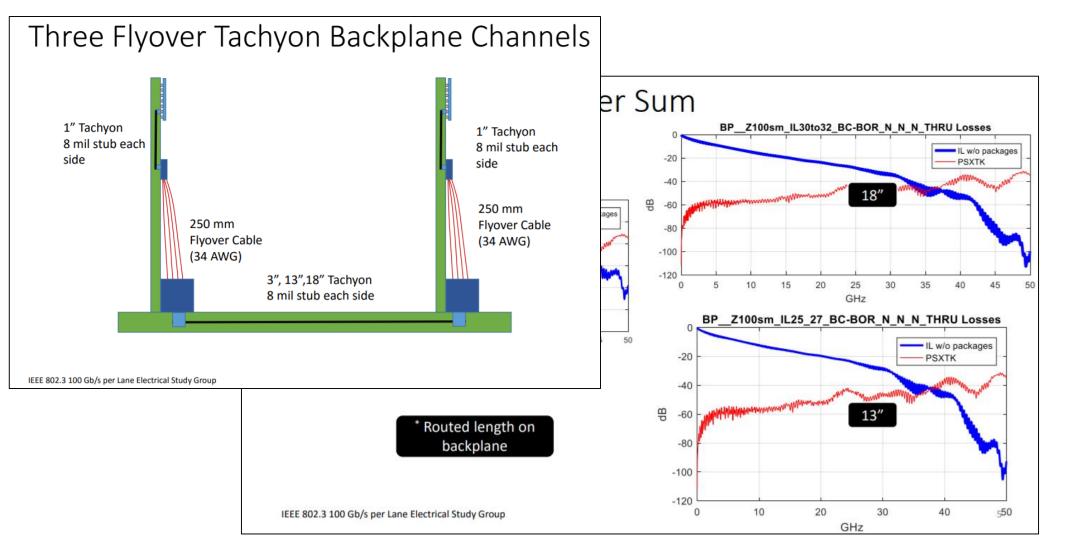

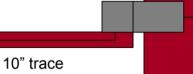

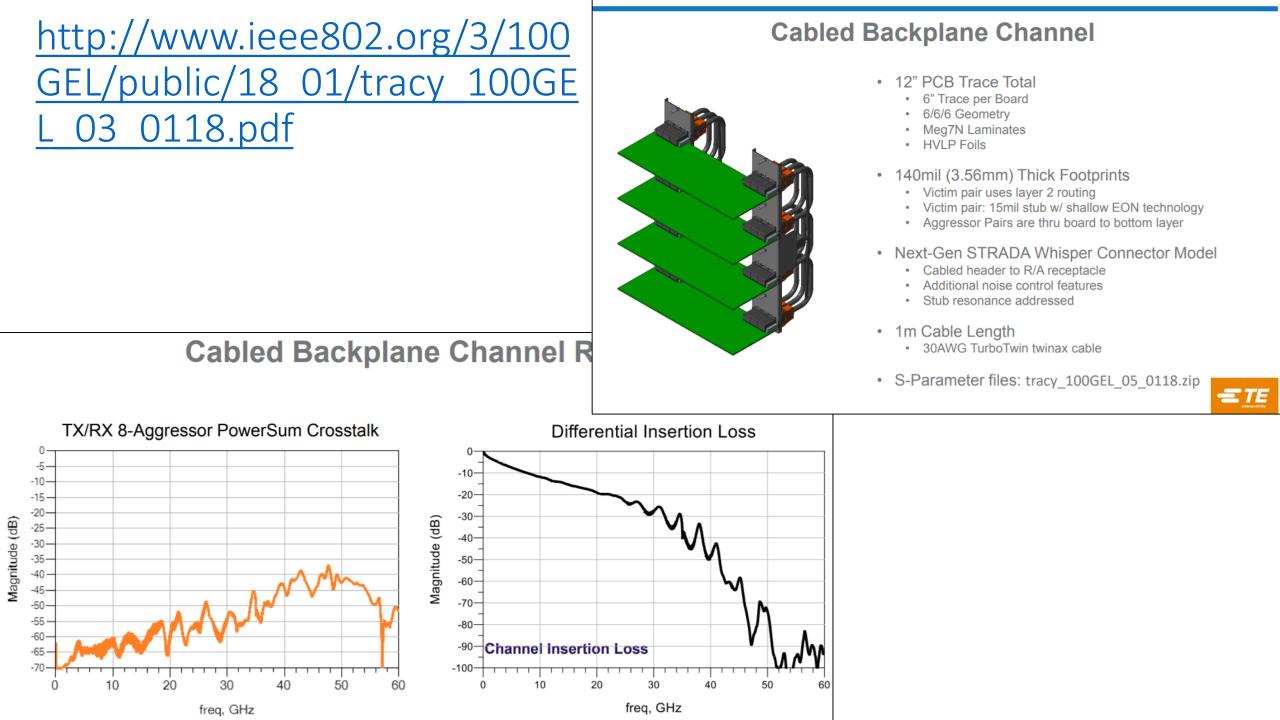

#### **Orthogonal Backplane Channel**

60

#### 18" PCB Trace Total

- 9" Trace per board .

- 6/6/6 trace geometry

- Meg7N Laminates

- HVLP Foils

- 140mil (3.56mm) Thick PCBs

- Victim pair uses layer 2 routing

- Victim pair: 15mil Stub w/ Shallow EON Technology

- · Aggressor Pairs are thru board to bottom layer

- Next-Gen STRADA Whisper Connector Model

- Direct-Plug Orthogonal

- · Stub resonance has been addressed

- Additional noise control features

- S-Parameter files: tracy 100GEL 04 0118.zip

= TE

TX/RX 8-Aggressor PowerSum Crosstalk Differential Insertion Loss 0. -5--10 -10--20 -15my -20 --30-Magnitude (dB) Magnitude (dB) -25 -40--30--35 --50--40 --60 -45--70--50 --55 --80 martin -60 --90 **Channel Insertion Loss** -65 --100 -70 20 30 50 10 20 30 40 50 10 freq, GHz freq, GHz

## http://www.ieee802.org/3/100GEL/public/adhoc/jan03 18/mellitz 100GEL adhoc 01 010318.pdf