# Discussion on Error Statistics

Phil Sun, Credo Semiconductor

IEEE 802.3ck Task Force February, 2019

### **Introduction**

- In Long Beach meeting, we had discussions whether burst errors exist besides DFE error propagation.

- <u>lyubomirsky\_3ck\_01a\_0119</u> proposed to solve burst error issue by constrain DFE tap weights or use SERDES "not prone to burst error problems" as no other burst sources found in a channel simulation.

- <u>he\_3ck\_01a\_0119</u> shows burst error problems for a long-FFE receiver with two light-weight DFE taps.

- As ideal simulations may not capture system behavior, this contribution analyzes reported FEC error statistics and calls attention to burst error penalty in link budget analysis.

IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

# Sources of Burst Errors

- Correlated noise.

- Slow loops in the receiver.

- Implementation imperfection.

- May be data pattern dependent.

- Burst errors exist regardless of SERDES architecture.

### **Reported FEC Statistics**

• FEC statistics is reported for 400GBASE-LR8 with 27km SMF <u>cole\_b10k\_01\_0718</u>. RAW BER is 8.71e-5.

| No. of Symbols | Count             | Percentage |

|----------------|-------------------|------------|

| 1              | 1,829,578,729,491 | 77.82708   |

| 2              | 437,987,258,685   | 18.63121   |

| 3              | 72,660,290,732    | 3.09084    |

| 4              | 9,452,501,111     | 0.40209    |

| 5              | 1,035,966,554     | 0.04406    |

| 6              | 100,548,342       | 0.00427    |

| 7              | 8,996,715         | 0.00038    |

| 8              | 768,593           | 0.00003    |

| 9              | 64,951            | 0.00000    |

| 10             | 5,574             | 0.00000    |

| 11             | 502               | 0.00000    |

| 12             | 49                | 0.00000    |

| 13             | 4                 | 0.00000    |

| 14             | 1                 | 0.0000     |

| 15             | 0                 |            |

IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

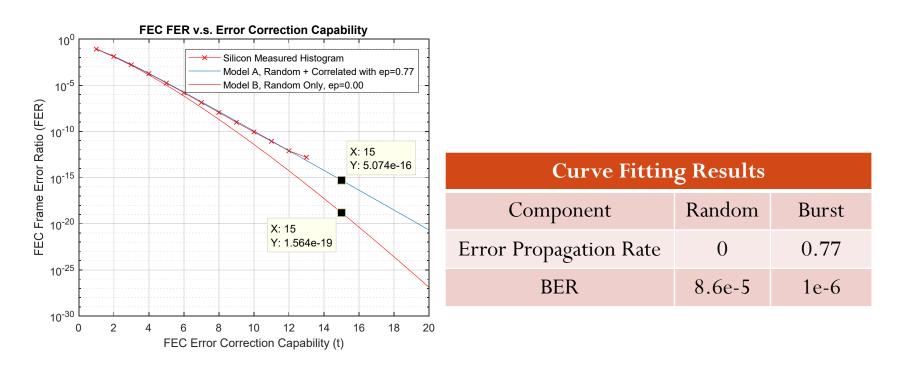

# **Error Histogram Analysis**

- If errors are random, post FEC BER is better by more than three orders.

- The measured error statistics can be fitted by random error + correlated error.

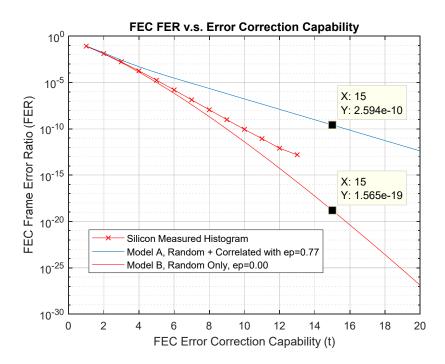

#### Performance of Non-interleaved FEC

• If non-interleaved FEC is used for this link, FER is predicted to be 2.59e-10 (BER after FEC is likely worse than 1e-12).

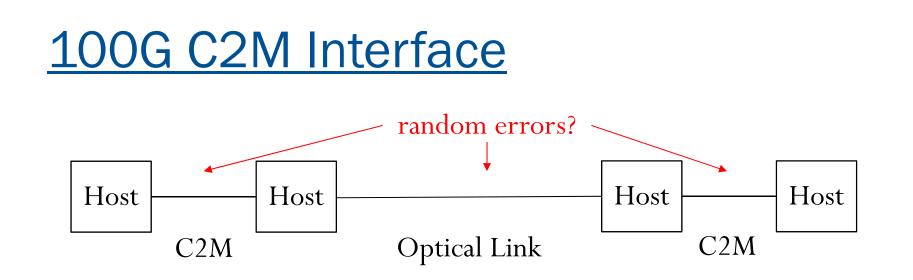

- 100G C2M may have 22dB insertion loss, severe reflections, and bad XTK.

Challenging to C2M receivers which has tight power constraints.

- 100G C2M link budget is currently studied in 802.3ck project by assuming optical link errors are random, and burst errors exist in C2M interface if DFE is used.

- Correlated errors exist regardless whether there is DFE. Burst errors caused by DFE tail acts as a proxy of other burst errors. Extra burst error model is needed if C2M reference receiver has no DFE tails.

- Ignoring burst error penalty may result in low-quality C2M link which will consume link budget of optical segment in the field.

IEEE 802.3 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

# **Discussion on Interleaved FEC**

- o gustlin\_3ck\_01\_0119 proposes:

- 2-way Interleaved FEC for 200GbE and 400GbE

- 2-way Interleaved FEC for 100GbE KR and CR

- Non-interleaved FEC for 100GbE C2M and C2C

- Extra latency for 2-way interleaving is 50ns for 100GbE.

- Interleaving can be defined as optional

- Low latency FEC modes can be defined

- Optional Interleaved FEC for 100G C2M and C2C?

- Non-interleaved FEC is needed for backward compatibility, e.g. 100GBASE-DR.

- Optional interleaved FEC relaxes budget of C2M and optical link when both ends are new host devices.

- New PMD can define interleaved FEC mode for better performance without much cost.

- 50ns extra latency is negligible for optical links.

## **Conclusions and Suggestions**

- Correlated errors are observed in PAM4 optical links.

- Proper modeling of correlated errors helps to optimize link budget and control link quality.

- Call for FEC statistics data for further study:

- FEC histogram as on page #3.

- DFE on/off status. DFE weight if it is ON.

- Total test time.

- Better to have data with both 100G and 400G FEC.

- Any PAM4 link measurement is OK.

- Possible actions if burst errors generally exist:

- Include burst error effect in modeling. Recently long DFE model is being used for burst error analysis. It might be a good proxy for other sources to avoid being too optimistic about error randomness.

- Stronger FEC schemes. Interleaved FEC relaxes link budget for C2M, optics, and KR/CR. It can be specified as optional for backward compatibility or low latency.

- Allocate link budget for burst errors.