# TRANSMIT EQUALIZER STEP SIZE SPECIFICATIONS (COMMENTS #62, #63, #74, #10249)

Adee Ran, Intel

March 2020

#### Background

- Tx equalization maximum step size specification was 5% in 50G electrical PMDs (clauses 136, 137, also annex 120D)

- c(-2) was specified as 2.5%.

- In 802.3ck:

- Following <u>hidaka\_3ck\_adhoc\_01\_120518</u> and <u>sun\_3ck\_adhoc\_01a\_120518</u> all analysis assumed a 2% step size for c(-3) through c(0), and this value was included in the baseline proposal <u>heck\_3ck\_03b\_0319</u>.

- 5% for c(+1)

- The 2% step size can create an additional burden on DAC-based transmitters. Power impact estimated as ~0.5 pJ/bit.

- In <u>ran\_3ck\_adhoc\_01\_021920</u> we have shown that step size has small and very irregular effect on COM results.

- Comments #62, #63, #74, #10249 against D1.1 address Tx equalization step sizes.

#### Goals of this presentation

- In <u>ran\_3ck\_adhoc\_01\_021920</u> it was stated that "Moving from 2.5% to 2% requires an additional DAC bit, otherwise some steps will have no measurable effect."

- Feedback received suggested that the additional bit may be required only in digital calculations, and not necessarily in the DAC, by rounding the calculated FFE output to 7 bits.

- The claim about "no measurable effect" was indeed incorrect.

- Rounding will be discussed below (spoiler: possible, but with increased Tx noise).

- Other comments suggest that having a 5% step size for c(+1) alone does not benefit Tx design and can create unexpected complexity for optimization algorithms.

- This will be explained.

### Possible designs choices

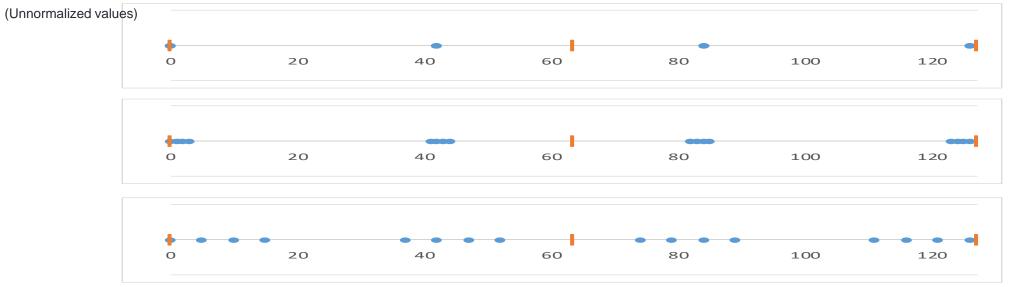

To meet a 2.5% step size specification

- 7-bit integer 2-tap FFE calculation can work as follows:

- Input is {-3, -1, +1, +3}

- Multipliers are 0:0.5:21 (42 values) for c(0), and -5:0.5:0 (11 values) for c(-1)

- Normalized step size is 1/42 = 2.38%

- Output range is 21\*3 21\*(-3)=126

- Output is shifted to an unsigned range of 0 to 126 (so the value 63 corresponds to zero differential output)

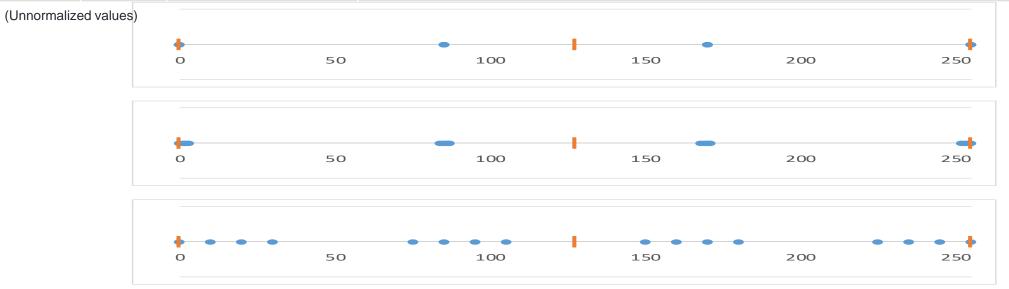

To meet a 2% step size specification

- 8-bit integer FFE calculation is required:

- Input is {-3, -1, +1, +3}

- Multipliers are 0:0.5:42.5 (85 values) for c(0), and -10:0.5:0 (21 values) for c(-1)

- Normalized step size is 1/85 = 1.18%

- Output range is 42.5\*3 42.5\*(-3)=255

- Output is shifted to an unsigned range of 0 to 255 (so the value 127.5 corresponds to zero differential output)

#### Results of 7-bit design

#### • Outputs for different coefficient combinations:

| c(-1) | c(0) | NRZ outputs                   | PAM4 outputs                                                     |

|-------|------|-------------------------------|------------------------------------------------------------------|

| 0     | 21   | <mark>0</mark> ; 126          | <mark>0</mark> ; 42; 84; 126                                     |

| -0.5  | 20.5 | <mark>0, 3</mark> ; 123, 126  | 0, 1, 2, 3; 41, 42, 43, 44; 82, 83, 84, 85; 123, 124, 125, 126   |

| -2.5  | 18.5 | <mark>0, 15</mark> ; 111, 126 | 0, 5, 10, 15; 37, 42, 47, 52; 74, 79, 84, 89; 111, 116, 121, 126 |

#### 6

#### Results of 8-bit design

#### • Outputs for different coefficient combinations:

| c(-1) | c(0) | NRZ outputs                   | PAM4 outputs                                                           |

|-------|------|-------------------------------|------------------------------------------------------------------------|

| 0     | 42.5 | <mark>0</mark> ; 255          | <mark>0</mark> ; 85; 170; 255                                          |

| -0.5  | 42   | <mark>0, 3</mark> ; 252, 255  | 0, 1, 2, 3; 84, 85, 86, 87; 168, 169, 170, 171; 252, 253, 254, 255     |

| -5    | 37.5 | <mark>0, 30</mark> ; 225, 255 | 0, 10, 20, 30; 75, 85, 95, 105; 150, 160, 170, 180; 225, 235, 245, 255 |

# What if output DAC is 7 bits?

#### With 7-bit calculation

- FFE calculation is fed directly to DAC

- Pure linear system, no additive noise

- Equalization control is more coarse than with 8 bits

- But, as we have shown, with the Rx adaptive equalization the result may actually be better

#### With 8-bit calculation

- Outputs have to be divided by 2

- Problem: some outputs are even, some are odd

- Truncation error is either 0 or 1 LSB depending on input sequence → additive quantization noise

- With RMS= $\frac{1}{\sqrt{2}}$  LSB, effect on SNDR is small but this quantization noise can't be mitigated by the Rx

- More refined equalization control is not necessarily beneficial

- More expensive digital calculations

### What about c(+1)?

- If the max step size is >2x larger than the rest, implementations may actually apply double steps

- This creates complications for receivers trying to optimize Tx equalization.

- Suppose the receiver wants to sweep possible values of c(+1) starting from preset 1:

- Prior to decrementing c(1), c(0) must be decremented, to prevent getting an "equalization limit" response

- In the Tx (unlike COM calculation) c(0) is not automatically determined from other coefficients

- If step sizes are the same, one decrement of c(+1) requires one decrement of c(0)

- If c(1) has 2x step size, one decrement of c(+1) requires two decrements of c(0).

### The problem with unequal step sizes

- The Rx has no way to tell what step sizes the Tx has.

- Uncertainty exists regardless of the "search" algorithm chosen.

- Step sizes can vary even more...

- Planning for all possible combinations is difficult; validation is a nightmare.

- There is no real design benefit for having unequal step sizes.

- This ambiguity also exists with uniform step size limits...

- It was not realized until we had different limits in 802.3cd.

- We should add a recommendation to have nominally equal step sizes for all coefficients, to enable simple "step counting" logic.

### Summary

- Current max step size spec of 2% is too aggressive

- For a digital implementation, requires at least 8-bit calculations, if not 8-bit DAC

- Changing to max 2.5% would enable full 7-bit design with negligible impact (if any) on Rx

- Finer steps have no real benefit, and cost power

- COM grid is not necessarily related, but run time can be reduced by changing 2% to 2.5%

- Allowing c(+1) to have larger steps creates unexpected complexity in Rx optimization

- COM grid is not related; can stay with a larger step to reduce run time

- Recommended changes in D1.1 $\rightarrow$ D1.2:

- In transmitter characteristics

- Use uniform step size specs for all taps, with absolute step min: 0.005 and max: 0.025. Apply in subclause text and Tx summary table.

- Add a recommendation in the subclause text: "The step sizes of all coefficients should be nominally equal, to enable efficient scanning of the coefficient space."

- With editorial license

- In COM

- Change search step to 2.5% for all precursor taps.

- Apply the above for clause 162, clause 163, and annex 120G.

## BACKUP

From <u>ran\_3ck\_adhoc\_01\_021920</u>

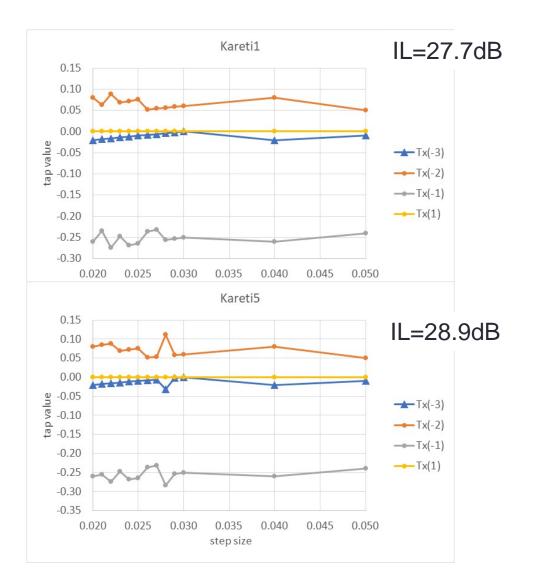

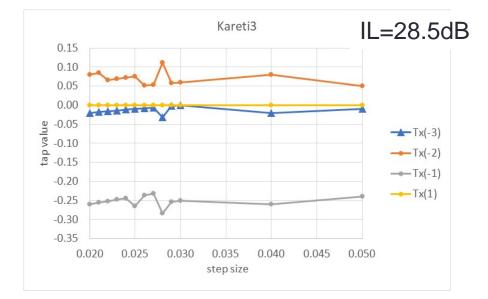

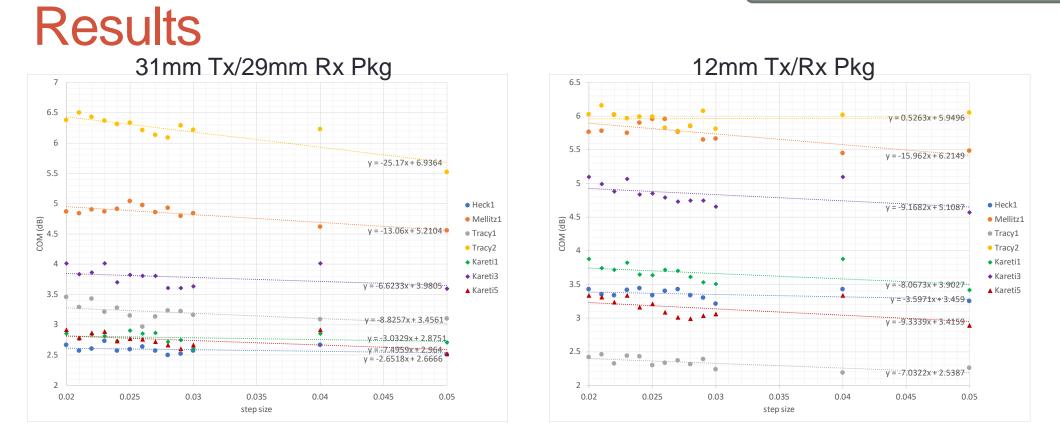

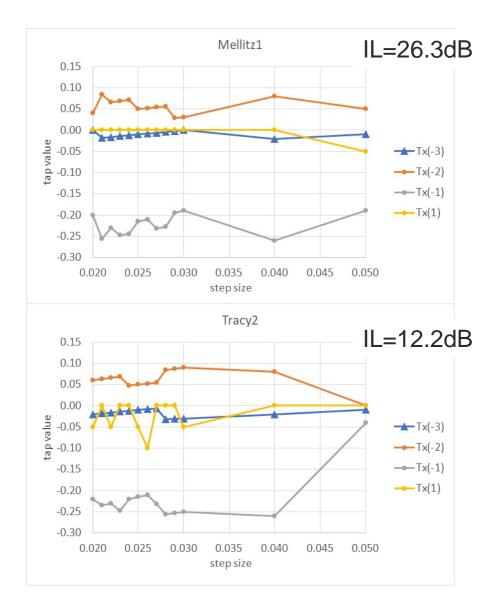

In both cases, COM vs. step size trend is very small in all channels

Effect of 2% to 2.5% is between ~0.05 dB (for low COM channels) and 0.13 dB (for the high COM channel)

Results are very "noisy" and inconclusive even at relatively large steps (R<sup>2</sup> maximum value was only ~0.75; most were much worse)

From ran\_3ck\_adhoc\_01\_021920

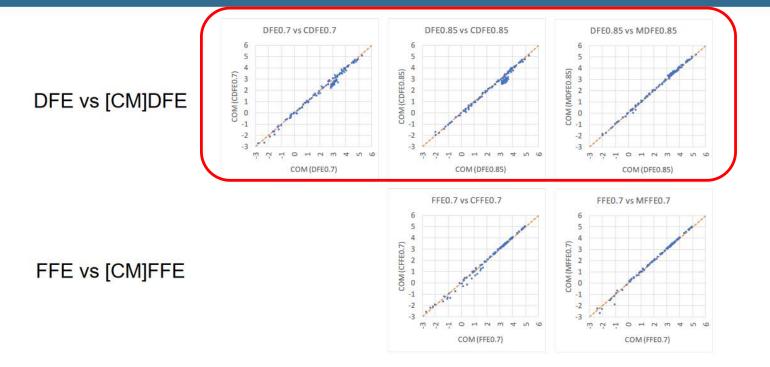

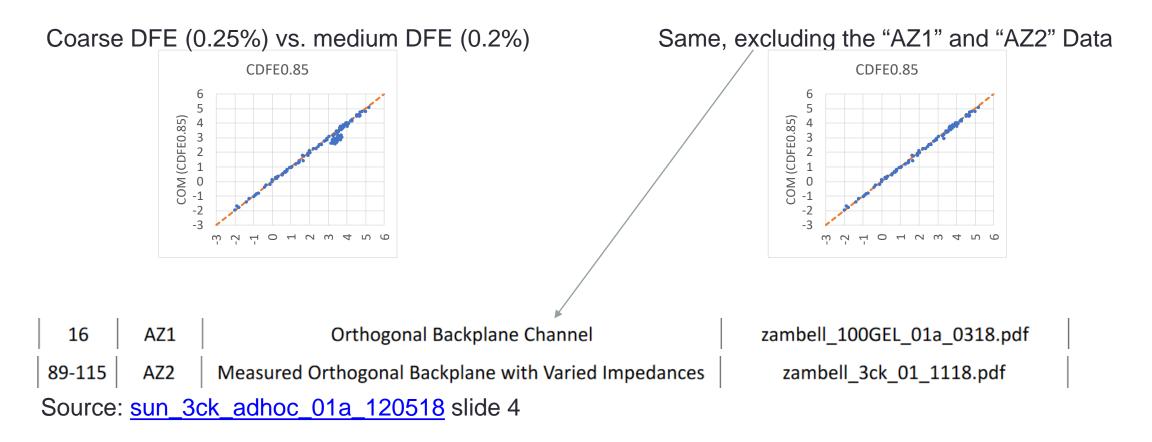

### What was the 2% recommendation based on?

#### **TX Resolution Impact**

Source: <u>sun\_3ck\_adhoc\_01a\_120518</u> Slide 8

2.5% (CDFE and CFFE) are often much worse than 1.5% (DFE and FFE)

2.0% (MDFE and MFFE) are close to 1.5% (DFE and FFE)

CredŐ

From ran\_3ck\_adhoc\_01\_021920

### Digging into the data

Full data set provided in <u>hidaka\_3ck\_adhoc\_02\_120518</u> to enable further analysis

From ran\_3ck\_adhoc\_01\_021920

#### **Eventually we chose a subset of channels for analysis** The Highlighted Channels

| Contribution                | Channel                                                      |               |

|-----------------------------|--------------------------------------------------------------|---------------|

| back 2ck 01 1119            | 28dB Cabled Backplane/Cable_BKP_28dB_0p575m_more_isi         | "AZ" channels |

| <u>heck 3ck 01 1118</u>     | <u>16dB Cabled Backplane</u> /Cable_BKP_16dB_0p575m_more_isi | in the list   |

| mellitz 3ck adhoc 02 081518 | 24,28,30dB including BGA Via/CaBP_BGAVia_Opt2_28dB           |               |

| tracy 3ck 01 0119           | Traditional Backplane Channels/Std_BP_12inch_Meg7            |               |

| TACY SCK OF OF ST           | Orthogonal Backplane Channels/DPO_IL_12dB                    |               |

|                             | Measured Orthogonal Backplane Channels/OAch4                 |               |

| karati 2ak 01a 1119         | Measured Orthogonal Backplane Channels/Och4                  |               |

| <u>kareti 3ck 01a 1118</u>  | Measured Cabled Backplane Channels/CAch3_b2                  |               |

|                             | Measured Traditional Backplane Channels/Bch2_a7p5_7          |               |

Source: kochuparambil\_3ck\_01c\_0119 slide 5

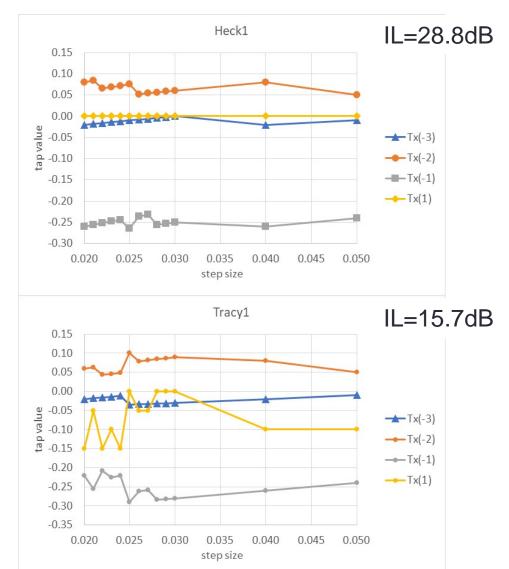

## Tap Values By Channel

#### From ran\_3ck\_adhoc\_01\_021920

31/29mm Tx/Rx Package

### **Tap Values By Channel**

From <u>ran\_3ck\_adhoc\_01\_021920</u>

31/29mm Tx/Rx Package