## Clarify EEE Quiet Signaling

Contribution to IEEE 802.3cy

Ragnar Jonsson and Alireza Razavi Majomard

Marvell

May 3, 2022

## Introduction

- Our previous contribution

jonsson majomard 3cy 01 04 05 22 discusses

some design considerations for EEE,

including

- the importance of allowing both transmitter and receiver to take full advantage of Low Power Mode

- to minimize constraints on transmitter and receiver while ensuring interoperability

- This presentation proposes simple changes to the excising EEE text to help with bot these issues

#### Transition to and from EEE Mode

#### Transition to Data Mode

- Some applications may require specific limits on the latency in transitioning from EEE mode to data mode

- Transition to data mode can not cause link drop if the other transmit direction is already in data mode

- There may be requirements on superframe alignment when transitioning to data mode

#### Transition to Low Power Mode

- The transition should be done in such a way that both transmitter and receiver can take full advantage of power savings in low power mode

- While in low power mode the requirements on the transmitter and receiver should be such that both sides can minimize power consumption

The EEE transitions should minimize constraints on transmitter and receiver, while ensuring reliable interaction between the transmitter and receiver

#### From:

https://www.ieee802.org/3/cy/public/adhoc/jonsson\_majomard\_3cy\_01\_04\_05\_22.pdf

# 802.3ch QR State Transition Requirements

- The 802.3ch EEE description implies that the Tx should not transmit any signal during the Quiet Period (this may not be explicitly stated in the standard)

- This implies that the Tx needs to avoid any glitches or transitory signals once it enters Quiet Period

- This restrictions brings no value to the EEE interoperability, but it can make it harder for the Tx to transition to low power mode

#### 149.3.6.2 Quiet period signaling

During the quiet period the PCS transmitter shall pass zeros to the PMA via the PMA\_UNITDATA.request primitive.

#### 149.3.6 LPI signaling

PHYs with EEE capability have transmit and receive functions that can enter and leave the LPI mode independently. The PHY can transition to the LPI mode when the PHY has successfully completed training and pcs\_data\_mode is TRUE. The transmit function of the PHY initiates a transition to the LPI transmit mode by generating the sleep signal comprised of eight RS-FEC frames composed entirely of LPI control characters, as described in 149.3.2.2.2.2. When the transmitter begins to send the sleep signal, it asserts tx lpi active and the transmit function enters the LPI transmit mode.

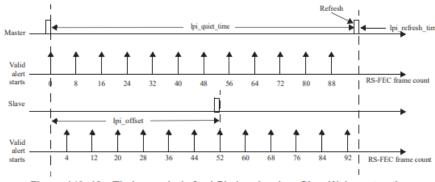

Within the LPI mode, PHYs use a repeating quiet-refresh cycle (see Figure 149–13 and Figure 149–14). The LPI timing parameters are shown in Table 149–5. The first part of this cycle is known as the quiet period and lasts for a time lpi\_quiet\_time. The quiet period is defined in 149.3.6.2. The second part of this cycle is known as the refresh period and lasts for a time lpi\_refresh\_time. The refresh period is defined in 149.3.6.3. A cycle composed of one quiet period and one refresh period is known as an LPI cycle and lasts for a time lpi\_qr\_time.

The parameters lpi\_offset, lpi\_quiet\_time, lpi\_refresh\_time, and lpi\_qr\_time are timing parameters that are integer multiples of the RS-FEC frame period. lpi\_offset is a fixed value equal to lpi\_qr\_time / 2 + 4 (52 RS-FEC frame periods).

The end of LPI mode occurs at the transmission of the alert signal indicating the end of quiet-refresh cycle.

Figure 149–13—Timing periods for LPI signals when Slow Wake not active

## Problem Statement and Motivation

### The149.3.6.2 text has two problems:

- It is ambiguous about what shall be transmitted on MDI, because 802.3ch does not define mapping to "zero voltage", so PCS outputting zeros does not necessarily imply "zero voltage" on the MDI

- It does not state anything about transition period from "normal transmission" to quiet period

## Why clarify the text:

- When transitioning to lower internal power state, the transmitter may introduce minor "glitches" on the line

- When transitioning to lower internal power state, the receiver may have some "glitches" in its internal signals

- Allowing for clearly specified transition period can benefit both transmitter and receiver, and help interoperability

## Proposed Updates for the 802.3cy EEE Text

## In 802.3cy, the text from 149.3.6.2 should be changed to

When entering quiet mode, the receiver shall ignore the first 330 ns (one RS-frame). During this time, the transmitter may output any signal within the bounds of PMA electrical limitations described 165.5.3. After this transition, the PCS transmitter shall pass all zeros to the PMA and the PMA shall transmit silence on the MDI.

### 149.3.6.2 Quiet period signaling

During the quiet period the PCS transmitter shall pass zeros to the PMA via the PMA\_UNITDATA.request primitive.

Essential technology, done right™