#### PLCA Corner-case Fixes Feb, 23<sup>rd</sup> 2022

- Since 802.3cg was approved, a number of rare (unwanted) corner-case behaviors were found in the PLCA state diagrams

- These are really unwanted behaviors that are not covered by the PLCA state diagrams model defined in Clause 148

- Reasonable implementations already worked around these flaws/limitations

- Still, I think the model should be updated to cover all cases and be consistent

- This presentation shows what these corner cases are and suggests fixes

In no case these changes break interoperability with what is currently defined in Clause 148

# #1: Data corruption when dynamically switching from plain CSMA/CD to PLCA

### #1: problem

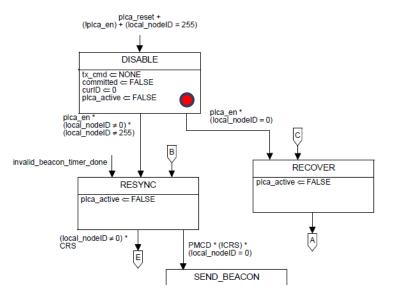

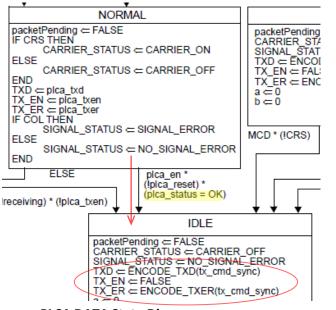

#### PLCA Control State Diagram, part a

**PLCA DATA State Diagram**

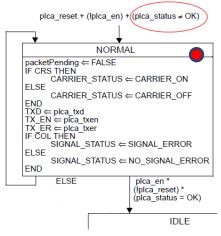

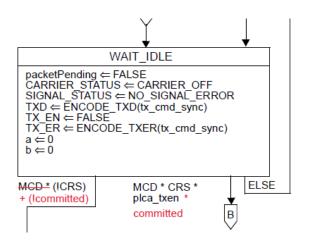

- Assuming the coordinator node (local\_nodeID = 0) has PLCA enabled (plca\_en = TRUE) but no BEACON has been sent so far (plca\_status = FAIL)

- This may happen when enabling PLCA on-the-fly

- Because of plca\_status being FAIL, the PLCA DATA State Diagram is stuck in NORMAL state

- That is, "plain" CSMA/CD behavior

### #1: problem

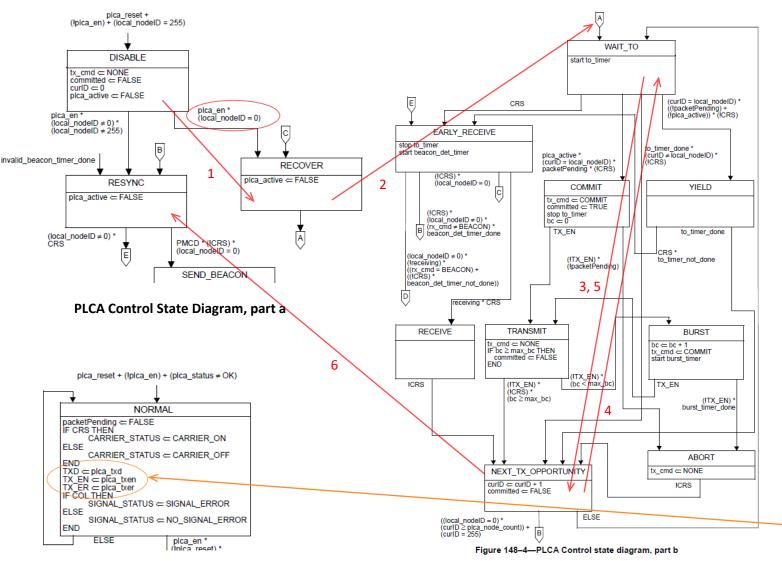

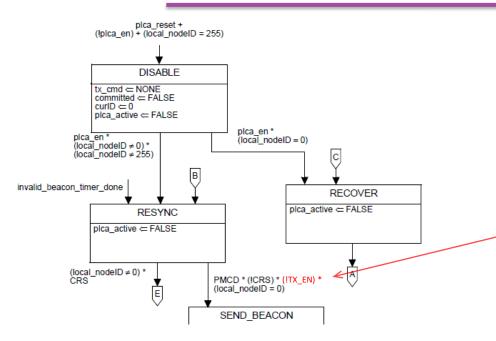

- The PLCA Control State Diagram moves through RECOVER and WAIT\_TO states (1, 2) then waits for one cycle of TOs (repeat 3, 4) before entering RESYNC state (5, 6)

- Note that during this time, plca\_active = FALSE, hence plca\_status = FAIL

- If the MAC initiates a frame transmission at this time, it would be sent immediately (provided that CRS allows it)

PLCA DATA State Diagram

### #1: problem

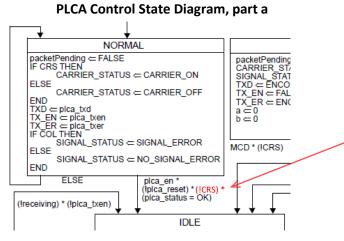

PLCA Control State Diagram, part a

**PLCA DATA State Diagram**

Carnovatech

The Art of Sílícon Sculptíng

- The problem shows up if the aforementioned frame is sent a few bit times before the PLCA Control state diagram enters the RESYNC state

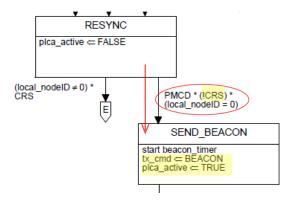

- In such a case, the CRS would not yet be asserted due to the MII and PHY latencies, therefore letting the PLCA Control state diagram go to SEND\_BEACON state

- This makes the PLCA Data state diagram move to IDLE state (because plca\_active = TRUE, plca\_status = OK)

- In IDLE state, the frame data coming from the MAC is overwritten by tx\_cmd being set to BEACON

- The frame gets corrupted at the MII (!)

- A simple solution to prevent this race condition is to inhibit the PLCA Control State Diagram from entering the SEND\_BEACON state while the DATA

State Diagram is in the process of sending a frame.

- Additionally, the transition from NORMAL to IDLE in the PLCA DATA State Diagram should be conditioned by CRS being low

#### PLCA DATA State Diagram, part a

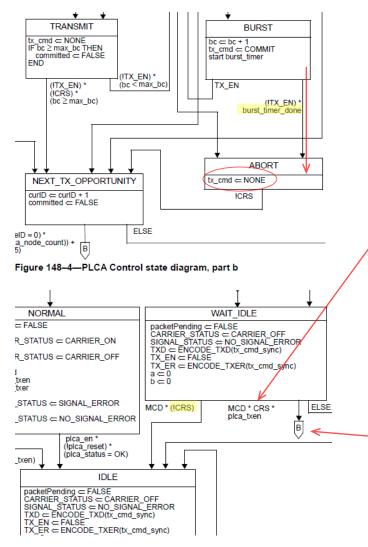

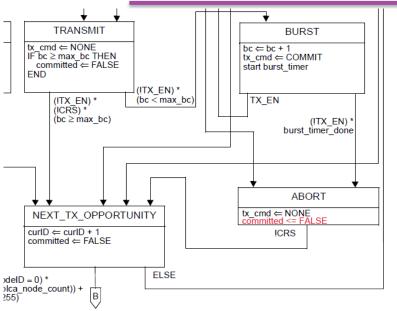

### #2: Data corruption at the end of an aborted PLCA burst

- When PLCA burst mode is activated (max\_bc > 0), the PLCA RS waits the MAC to send a new frame for the duration of "burst\_timer" before moving to the next transmit opportunity.

- During this time, a COMMIT is conveyed to the PHY to "keep" the current TO by extending the carrier (CRS = TRUE).

- If the MAC conveys a new frame while the burst\_timer is active, the burst succeeds and the PLCA RS forwards the frame to the PHY via MII (appended to the COMMIT)

- else (i.e. the MAC has no further frames to send), the PLCA RS aborts the burst and moves to the next TO

- If the MAC initiates a frame transmission (plca\_txen = TRUE) concurrently with the burst\_timer expiration, the PLCA RS is supposed to just act as normal, delaying the frame until the next TO...

- BUT there's a race condition in the state diagrams!

### #2: problem

PLCA DATA State Diagram, part a

Carovatech

The Art of Sílícon Sculptíng

- When the burst\_timer expires, the PLCA Control State Diagram goes from BURST to ABORT state.

- Meanwhile, the PLCA Data state diagram is waiting in WAIT\_IDLE state for the MAC to send a new frame (plca\_txen = TRUE) or the burst to be aborted (CRS going low due to tx\_cmd being set to NONE)

- However, if the MAC starts conveying a frame a few bit times after the burst was aborted (before MCD), the PLCA Data state diagram would take the path of the successful burst "B" while the PLCA Control state diagram already aborted the burst (!)

- This may lead to the frame being corrupted and to unwanted collision on the line

Figure 148-4-PLCA Control state diagram, part b

PLCA DATA State Diagram, part a

CANDVATECH

The Art of Silicon Sculpting

- The fix is to avoid the race condition by removing the synchronization on the MII clock (MCD) which is not required in that state anyway.

- Then, we can synchronize on the "committed" variable, instead.

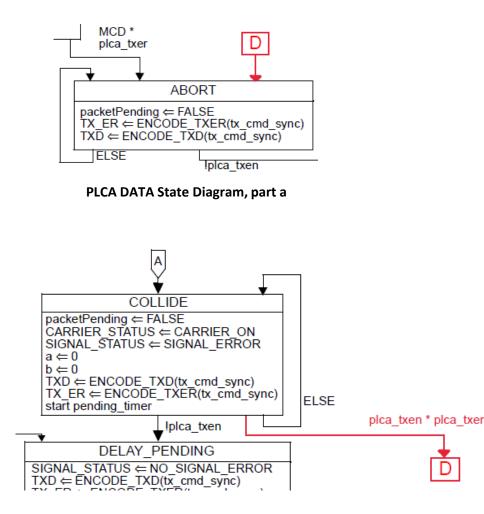

### #3: frame aborted by the upper layers (plca\_txer = 1)

- The PLCA RS detects collisions by both monitoring the COL signal from the PHY and checking transmissions vs transmit opportunities

- In the latter case, the PLCA RS relies on the MAC to backoff and make a new attempt at sending the frame after the carrier indication goes off

- If the upper layers aborted the frame concurrently with the PLCA RS detecting a collision (very rare race), the next transmit opportunity may be skipped, leading to wasted bandwidth and/or multiple collisions

#### #3: solution

PLCA DATA State Diagram, part b

Carovatech

The Art of Sílícon Sculptíng

- A simple fix is to check the already existing plca\_txer variable while the PLCA Data State Diagram is in the COLLIDE state.

- If plca\_txer is set, just go into ABORT state, letting the PLCA RS serve the next TO without setting packetPending to TRUE

# CONCLUSIONS

- The current definition of the PLCA state diagrams hides unwanted (rare) race conditions leading to corrupted frames and/or performance loss

- This presentation shows simple fixes that don't break interoperability with systems implementing what's currently specified in Clause 148.

- I suggest 802.3da to adopt these fixes as enhancements over 802.3cg

## THANK YOU