| 8802-3/802.3 REVISION REQUEST 1167 |                                                                                                    |

|------------------------------------|----------------------------------------------------------------------------------------------------|

| ATE:                               | 30th March, 2005                                                                                   |

| AIE:                               | Yair Darshan                                                                                       |

| AME:<br>OMPANY/AFFILIATION:        |                                                                                                    |

|                                    |                                                                                                    |

| -MAIL:                             | yaird@powerdsine.com                                                                               |

| EQUESTED REVISION:                 |                                                                                                    |

| STANDARD:                          | IEEE Std. 802.3af-2003                                                                             |

| CLAUSE NUMBER:                     |                                                                                                    |

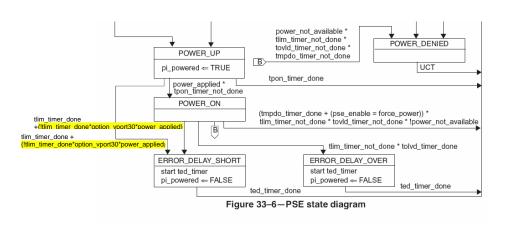

| CLAUSE TITLE:                      | PSE State diagram                                                                                  |

| ROPOSED REVISION TE                | XT:                                                                                                |

|                                    |                                                                                                    |

| dd now wariahla ant                | ion tmort30 to 33 2 3 4. It will be an entional                                                    |

|                                    | ion_vport30 to 33.2.3.4. It will be an optional te diagram (figure 33-6) per the attached drawing. |

| arrabic. Change sta                | ce aragram (rigure 33 of per the accached drawing.                                                 |

| ption_vport30                      |                                                                                                    |

|                                    | icating PSE port voltage.                                                                          |

| lues:                              | reacting IDE porc vorcage.                                                                         |

| lse: Vport is abov                 | 2077                                                                                               |

| rue: Vport is below                |                                                                                                    |

| im minimum may be                  |                                                                                                    |

| In militmum may be                 | SHOLCEH CO IMS.                                                                                    |

|                                    | OM .                                                                                               |

| ATIONALE FOR REVISI                | OIN:                                                                                               |

| ne state diagram all               | ows a scenario that violates the minimum requirement                                               |

|                                    | in table 33-5 item 21 when PSE-PD motor-boating or                                                 |

|                                    | peak power during short circuit condition.                                                         |

| 9                                  |                                                                                                    |

| he proposed revision               | n allows the option of preventing such scenarios.                                                  |

|                                    |                                                                                                    |

| roblem description:                |                                                                                                    |

|                                    |                                                                                                    |

| uring short circuit                | condition, PD input voltage is dropping below                                                      |

| off=30V (table 33-1                | 2 item 8) the PD enters to its OFF mode and the PD                                                 |

|                                    | ischarged partially or completely pending the short                                                |

| ircuit condition du                | ration.                                                                                            |

| the grownest !                     | own love so the DCE realtons in mains high south                                                   |

|                                    | ery low so the PSE voltage is going high again and                                                 |

|                                    | Von value (30V to 42) it charge the PD capacitor                                                   |

| ain by drawing Iin                 | rusn.                                                                                              |

| DOE 1701+000 17:11                 | drop again holow Woff of the DD (2011) and the                                                     |

|                                    | drop again below Voff of the PD (30V) and the                                                      |

| rocess will be repe                | ated until TLIM is done.                                                                           |

| he results of this                 | conario are:                                                                                       |

| TE LEBUILS OF CHIES                | scenario are.                                                                                      |

| The time between                   | the first startup to the 2nd is much below Ted=750ms                                               |

|                                    |                                                                                                    |

which violates spec requirements of keeping cool off time between

consecutive startups.

53

54

It should be noted that while PSE is in POWER\_APPLIED status, the PD is in OFF or Startup state that's why Ted can not be controlled (From system point of view, there is no synchronization between PSE state and PD state).

2.6

Effectively the PSE may faces multiple inrush time duration which is 50ms minimum. According to the state diagram, Tlim starts counting once I>Iinrush and nothing can stop the counter until 50ms to 75ms time is reached. This scenario may generate excessive heat which should have been prevented by Ted minimum value 750mS as explained above.

- 2. Until TLIM timer done, the PSE and PD will pass few consecutive cycles of startups which as function of the short circuit time duration and the status of the PD during short will cause PSE-PD motor boating at high peak power, may generating noise and in some cases will cause PSE-PD stability issues due to the fact that the PSE during short circuit is a current source with high impedance that drives negative input impedance of the PD DC/DC if PD is ON and PSE still in current limit.

- 3. In addition, to prevent shutting down the port for short transients, it is recommended to set 1ms minimum value for Tlim.

In order to handle this scenario, we need to allow to shut the PSE port if Vport is below a value that cause PD to be at OFF.

Such Vport value exist in the spec, the 30V border line in the PD spec which is Voff per table 33-12 item 8 .

Using this optional variable in the state diagram will fix the problem by changing the inputs to ERROR\_DELAY\_SHORT state from: tlim\_timer\_done to: Tlim\_timer\_done + !tlim\_timer\_done\*option\_vport30\*power\_applied

## IMPACT ON EXISTING NETWORKS:

None if the new variable is optional as proposed.

+----+