### DTE power over MDI DTE Discovery Process Proposal

**Robert Muir**

November, 1999

**IEEE Kauai**

## Agenda

- General MDI link description.

- Level One discovery process proposal

- Discovery process alternatives review

- Conclusions

- Q and A

# **MDI Link Description**

- Certain assumption have been made about various components of the link based upon both customer and vendor feedback.

- Link using CAT3 or CAT5 cable will have loop impedance of up to 30 Ohms.

- Power requirement at the DTE will be 8-9 Watts thus requiring us to provide 11-12 Watts from the switch or other supplying device.

- Voltage should be a maximum of 45V d.c. (40V +/- 10% typical)

- Current will be injected via the center taps using a Phantom Power method on the TX and RX pairs.

- Magnetics will increase in height to accommodate the increase in current carrying capability.

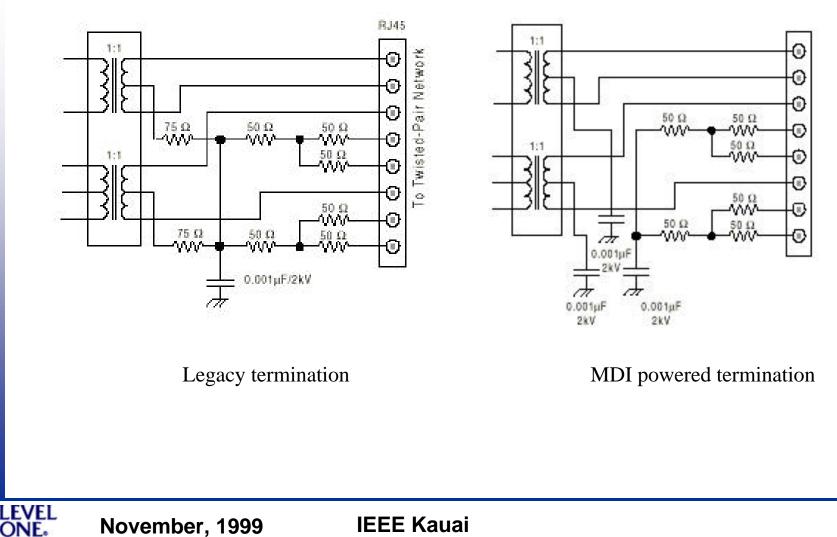

- The Bob Smith Termination will be changed to remove the d.c. path between Magnetics center taps.

- Discovery process will be resident in the PHY device.

- Note that there is no change required to the PHY or the MAC in the Client DTE

EVEL

### **Bob Smith Terminations**

**MDI** Link Description DTE power over MDI

# **MDI Link Description**

- Certain assumption have been made about various components of the link based upon both customer and vendor feedback.

- Link using CAT3 or CAT5 cable will have loop impedance of up to 30 Ohms.

- Power requirement at the DTE will be 8-9 Watts thus requiring us to provide 11-12 Watts from the switch or other supplying device.

- Voltage should be a maximum of 45V d.c. (40V +/- 10% typical)

- Current will be injected via the center taps using a Phantom Power method on the TX and RX pairs.

- Magnetics will increase in height to accommodate the increase in current carrying capability.

- The Bob Smith Termination will be changed to remove the d.c. path between Magnetics center taps.

- Discovery process will be resident in the PHY device.

- Note that there is no change required to the PHY or the MAC in the Client DTE

EVEL

### Level One PHY Discovery Process

IEEE Kauai

an Intel company

.EVEL

November, 1999

### Level One PHY Discovery process

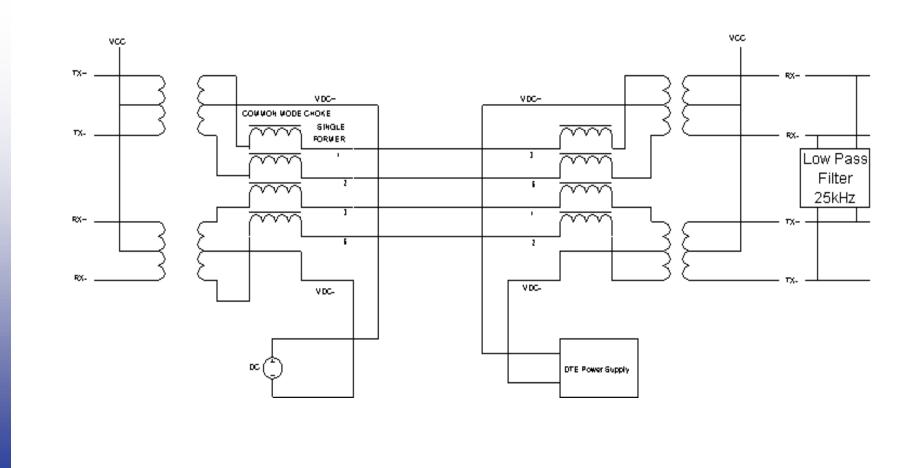

- The schematic on previous page shows the circuit for this implementation.

- As can be seen from the previous page this proposal uses a loop back between the TX and RX pairs.

- There is a Low Pass Filter with a 25kHz pole placed in the loop back path in the DTE.

- This filter will completely kill all data and link pulses.

- There is no requirement for a relay as the filter will be a high impedance to data under normal operating conditions.

- Low frequency pulses are sent across the link which will pass through the filter during the discovery process.

- The amplitude of these recovered pulses allows us determine the DTE type and make a decision on applying power or not.

C LEVEL ONE.

#### Discovery Determination

- When a pulse is sent out the amplitude of the returned signal will vary as follows;

- In the case of a loop back cable (Type 1) or patch panel test plug. There is no attenuation of the transmitted pulse so a HIGH level pulse is returned.

- In the case of a DTE requiring power the LPF will attenuate the pulse giving a MID level pulse on the return path.

- In the case of a DTE not requiring power there would be no pulse returned as there is no loop back.

- In the case of a DTE requiring power being connected to a legacy switch the normal data and link pulses would be attenuated by the LPF. No Link or data would be seen.

- Preliminary lab testing shows that we would be able to determine, with some margin, the type of DTE device on the link over the entire length of the link.

CONE.

#### Improving the Robustness of the Discovery Process

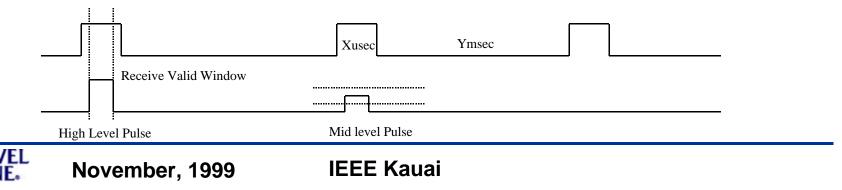

- Each pulse would be Xusecs wide

- The pulse would be sent a number of times, say 10.

- Each of these pulses would be spaced Ymsec apart.

- Each of these 10 pulses would have to give the same result consecutively at the receiver in order to produce a valid result.

- Further each pulse would have to be received within specific window during the transmission time. This would allow us to be sure that the result is a consequence of our test stimulus.

- This bounding of the occurrence of the pulse will allow us to eliminate NLPs, FLPs, 10/100 data or idle from being mistaken as a DTE requiring power.

#### **MAC Control Interface Requirements**

- The MAC would control the discovery process via the MDIO/MDC interface. A total of 3 register bits would be required to control this function.

- Enable Discovery Process This register bit would enable or disable the discovery process.

- Start/Restart Discovery Process This register bit would begin the actual process. This bit should be auto-cleared when the process is complete.

- DTE Discovered This register bit is set when a DTE requiring power has been discovered. This bit should be auto-cleared when the Start/Restart Discovery Process bit is set.

- This combination of bits will allow the MAC complete control over how many times it wishes to run the discovery process. Once satisfied that the result is consistent the MAC can apply power to the DTE.

• The Discovery process is a separate process carried out prior to Auto Negotiate or Parallel Detect.

Level One PHY proposal

DTE power over MDI

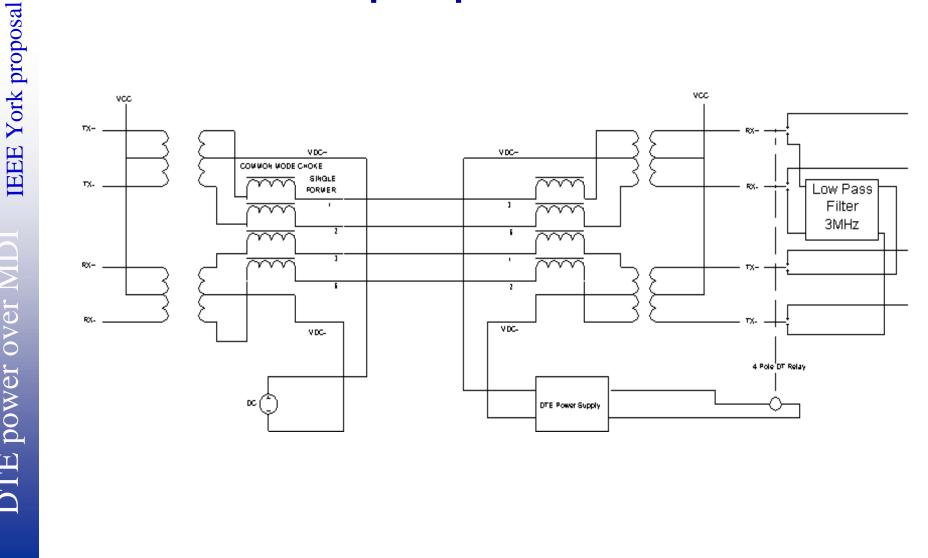

### **IEEE York proposal**

**IEEE Kauai**

DTE power over MD

LEVEL

November, 1999

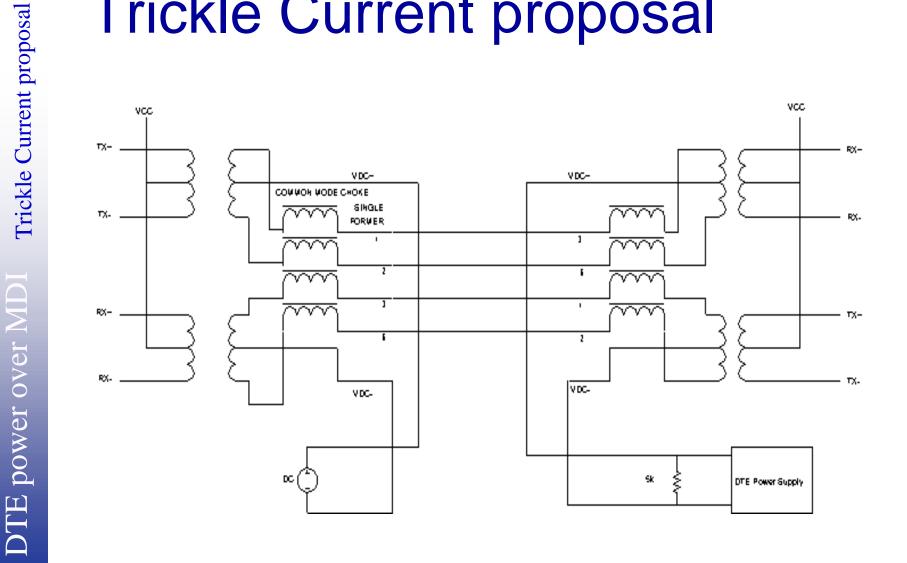

### **Trickle Current proposal**

.EVEL

**IEEE Kauai**

## Conclusions

- The LOC PHY based discovery process has the following advantages over the previous proposals;

- Solves the corner cases that were an issue with the original PHY based proposal.

- Minimal changes to switch or DTE to allow PHY discovery process.

- Fastest time to market implementation. All technology well understood.

- Lowest cost implementation.

- Eliminates the requirement for a relay in the DTE. \$0.30

- No requirement for isolated comparators or current sensing elements in the power supply. \$0.65 (\$0.95 if opto-isolated)

- Least number of components reduces return loss and layout issues