# Annex N

2 (informative)

# **Buffer requirements for PFC**

## 4 N.1 Overview

<sup>5</sup> To ensure that data frames are not lost due to lack of receive buffer space, receivers must ensure that a PFC 6 M\_CONTROL.request primitive is invoked while there is sufficient receive buffer to absorb the data that 7 can continue to be received during the time needed by the remote system to react to the PFC operation. The 8 PFC headroom (see 36.1.1) is the minimum buffer size that needs to remain available on receiver. It helps 9 implementation to allocate buffer for PFC-enabled priorities. But the The precise calculation of this buffer 10 requirement and buffer allocation are is highly implementation dependent. This annex provides an example 11 of how it can be calculated based on a hypothetical delay model. Setting the PFCLinkDelayAllowance (see 12 12.22.6) to less than the round trip delay value can result in frames loss.

<sup>13</sup> This annex explains delay model of PFC headroom, and provides an example of buffer allocation based on <sup>14</sup> the PFC headroom calculation.

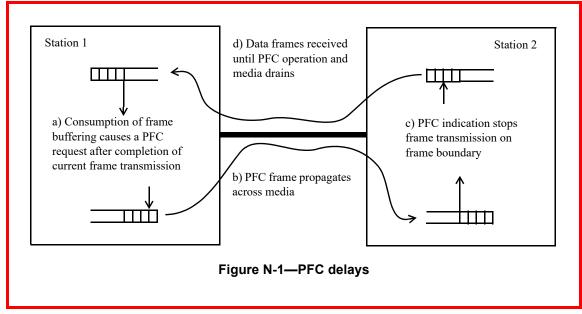

15 Figure N-1 provides an high-level view of the various delays to consider:

- 16 a) Processing and queuing delay of the PFC request

- 17 b) Propagation delay of the PFC frame across the media

- 18 c) Response time to the PFC indication at the far end

- 19 d) Propagation delay across the media on the return path-

# 20 N.2 Delay model of PFC headroom

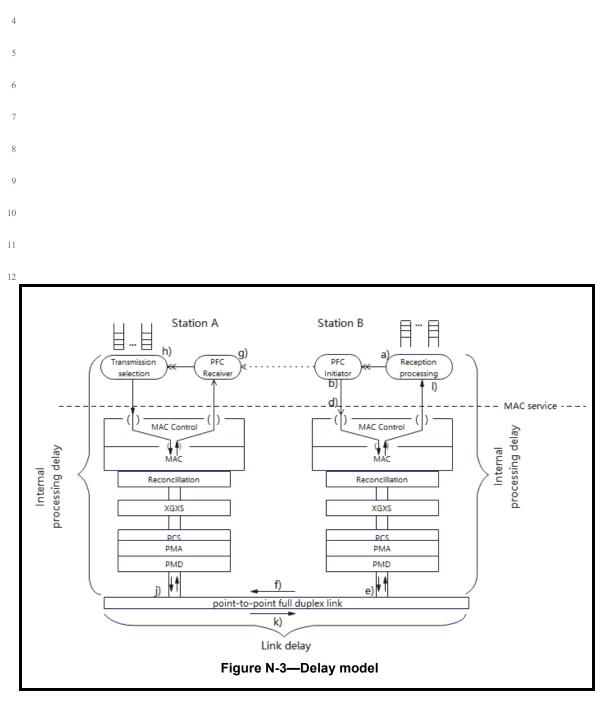

21 PFC headroom calculation considers various delays accumulated, from item a) to l) (see 36.1.1)

#### IEEE P802.1Q-Rev/D1.2

Draft Revision of IEEE Standard for Local and metropolitan area networks-Bridges and Bridged Networks

1 PFC frame transmission in PFC initiator station B:

- 2 a) <u>B's reception processing to calculate the remaining buffering following frame receipt.</u>

- b) <u>B's PFC Initiator to initiate PFC following that buffering calculation and PFC frame encoded ready</u>

<u>for transmission.</u>

- 5 c) <u>Any prior in-progress frame transmission by B (possibly of a maximum sized frame) to complete.</u>

- 6 d) First bit of PFC frame sent to MAC service.

- 7 e) Last bit of PFC frame sent on the physical link.

8 PFC frame transmission across link from B to A:

9 f) <u>The link delay for transmission from B to A.</u>

10 PFC frame reception in PFC receiver station A (including PFC taking action):

- g) <u>PFC frame reception since the last bit of PFC frame received on link, including frame validation, by</u>

<u>A's interface stack.</u>

- 13 h) <u>A's PFC Receiver to decode the PFC frame and halt transmission selection for specified priorities.</u>

14 User data transmission in PFC receiver station A:

- i) Any in-progress frame transmission by A (possibly of a maximum sized frame) to complete.

- 16 j) Last frame sent on the physical link.

17 User data transmission across link from A to B:

18 k) The link delay for transmission from A to B.

19 User data reception in PFC initiator station A:

I

20 I) <u>Reception delays associated with B's interface stack, reception processing, and buffering.</u>

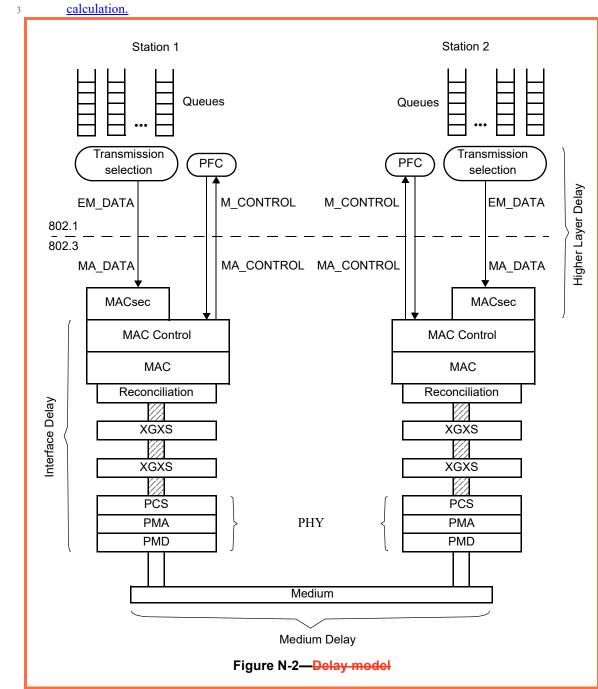

21 Figure N-2 shows how to model the various delays between two stations connected by a point-to-point full-22 duplex IEEE 802.3 link.

23 The main delay components shown in Figure N-2 are as follows:

24 When calculating PFC headroom, the delays are classified into 3 main components shown in Figure N-1, as 25 below:

| 26 | a) | <b>PFC transmission delay:</b> the time needed by a station to request transmission of a PFC frame after |  |  |  |

|----|----|----------------------------------------------------------------------------------------------------------|--|--|--|

| 27 |    | a PFC M_CONTROL.request has been invoked (e.g., because a maximum length data frame can be               |  |  |  |

| 28 |    | t <del>ransmitted).</del>                                                                                |  |  |  |

| 29 | b) | Interface Delay (ID): the sum of MAC Control, MAC/RS, PCS, PMA, and PMD delays, including                |  |  |  |

| 30 |    | item e), g), k). Interface Delay is dependent on the MAC and physical layer in use.                      |  |  |  |

| 31 | c) | Cable Delay: the number of bits in flight stored in the transmission medium. This delay value is         |  |  |  |

| 32 |    | dependent on the selected technology and on the medium length.                                           |  |  |  |

| 33 | d) | Higher Layer Delay (HD): the time needed for a queue to go into paused state after the reception of      |  |  |  |

| 34 |    | a PFC M CONTROL indication that paused its priority. A substantial portion of this delay                 |  |  |  |

| 35 |    | component is implementation specific.                                                                    |  |  |  |

| 36 | a) | Internal processing delay (ID): the time spent on frame processing within PFC initiator station and      |  |  |  |

| 37 | ,  | PFC receiver station, such as interface stack delay, and buffering delay etc, queue status change        |  |  |  |

| 38 |    | delay, assuming no prior in-progress frame transmission. ID includes item a) b) d) e) g) h) j) l).       |  |  |  |

| 39 | b) | Link delay (LD): the time spent on physical link between PFC initiator station and PFC receiver          |  |  |  |

| 40 |    | station. LD includes item f) and item k).                                                                |  |  |  |

| 41 | c) | Worst-case delay (WD): the additional time needed for a maximum sized frame transmission                 |  |  |  |

| 42 | ,  | before the PFC frame transmission at PFC initiator station, and the additional time needed for a         |  |  |  |

#### IEEE P802.1Q-Rev/D1.2 June 1, 2022 Draft Revision of IEEE Standard for Local and metropolitan area networks—Bridges and Bridged Networks

- maximum sized frame transmission after the PFC frame taking effect at PFC receiver station. WD

- includes item c) and item i). It is not shown in Figure N-2, but shall be considered by PFC headroom

4 The total delay value of PFC headroom is the sum of ID, LD and WD.

5 When calculating PFC headroom using link delays (see 36.8.1), 1588 measures LD. ID is based on peer

6 notification and local knowledge. WD depends on size of maximum frame and MACsec capability of user

7 <u>data.</u>

1

2

#### IEEE P802.1Q-Rev/D1.2

Draft Revision of IEEE Standard for Local and metropolitan area networks-Bridges and Bridged Networks

- 1 When calculating PFC headroom using measurement protocol (see 36.9), ID + LD is obtained by running

- 2 the protocol.\_Then by adding WD, the total delay is got. Keeping the measurement requests and responses

- 3 the same MACsec capability as PFC frames increases the measurement accuracy.

13

- 14

- 15

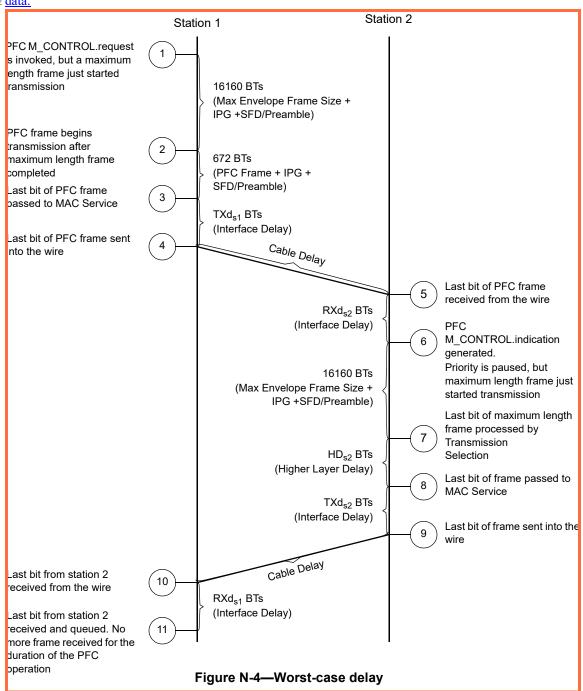

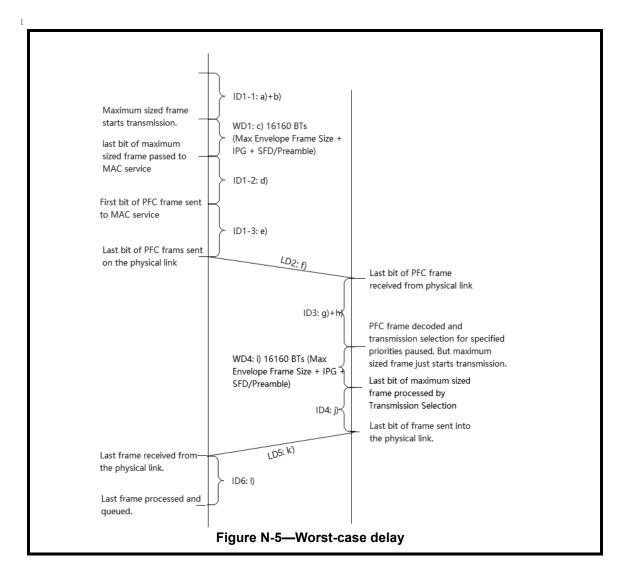

Figure N-4 shows a possible worst-case delay example where MACsec is disabled for PFC frame and user

2 data.

#### IEEE P802.1Q-Rev/D1.2 June 1, 2022 Draft Revision of IEEE Standard for Local and metropolitan area networks—Bridges and Bridged Networks

2

3 The total Delay Value (DV) is the sum of all delays shown in Figure N-4:

4  $DV = 2 \times (Max Frame) + (PFC Frame) + 2 \times (Cable Delay) + TXd_{s1} + RXd_{s2} + HD_{s2} + TXd_{s2} + S$ 5  $RXd_{s1}$

$6 \qquad \underline{DV = ID_1 + WD_1 + LD_2 + ID_3 + WD_4 + ID_4 + LD_5 + ID_6}$

7

$$\underline{ID}_{1} = \underline{ID}_{1-1} + \underline{ID}_{1-2} + \underline{ID}_{1-3}$$

```

8 It is the round-trip delay from PFC initiation to last frame reception and buffered, plus 2 maximum sized

9 frames represented by bit times.

```

```

10 For any given station the Interface Delay includes both transmit and receive paths (i.e., ID = TXd + RXd).

11 Therefore:

```

12  $DV = 2 \times (Max Frame) + (PFC Frame) + 2 \times (Cable Delay) + ID_{s1} + ID_{s2} + HD_{s2}$

13 Usually the peer stations connected by a point-to-point link use the same technology, therefore  $ID_{s1}$ -ID<sub>s2</sub>:

- 14  $DV = 2 \times (Max Frame) + (PFC Frame) + 2 \times (Cable Delay) + 2 \times ID + HD_{s2}$

- 15

# 1 N.3 Interface Delay Internal Processing Delay

2 The Internal Processing Delay is implementation dependent. It comprises frame processing delays above

3 MAC service which is between MAC control client and transmission selection, as well as MAC and PHY 4 layer interface delays.

<sup>5</sup> Example of processing delays above MAC service are MACsec and entering pause state delays.

6 For link speeds of up to 10Gb/s, MACsec constrains each of the transmit delay and the receive delay to a 7 maximum of 19 360 bit times (see 36.1.3.3).

8 <u>This standard defines a queue shall go into paused state in no more than 614.4 ns (see 36.1.3.3)</u>. This delay

9 is equivalent to 6144 bit times at the speed of 10Gb/s.

10 IEEE 802.3 defines different interfaces delay constraints for different MAC and PHY. Table N-1 shows the 11 delay constraints for some IEEE 802.3 interfaces.

12 The Interface Delay comprises all delay components below the MAC Control Client, excluding the cable 13 delay. Table N-1 shows the Interface Delay constraints for some IEEE 802.3 interfaces.

| Sublayer                     | Maximum RTT<br>(bit times) | Maximum RTT<br>(pause quanta) | Reference<br>(subclause of IEEE<br>Std 802.3-2018 [B14]) |

|------------------------------|----------------------------|-------------------------------|----------------------------------------------------------|

| 10G MAC Control, MAC, and RS | 8192                       | 16                            | 46.1.4                                                   |

| XGXS and XAUI                | 2048                       | 4                             | 48.5                                                     |

| 10GBASE-X PCS                | 2048                       | 4                             | 49.2.15                                                  |

| 10GBASE-R PCS                | 3584                       | 7                             | 50.3.7                                                   |

| LX4 PMD                      | 512                        | 1                             | 53.2                                                     |

| CX4 PMD                      | 512                        | 1                             | 54.3                                                     |

| Serial PMA and PMD           | 512                        | 1                             | 52.2                                                     |

| 10GBASE-T                    | 25 600                     | 50                            | 55.11                                                    |

Table N-1—IEEE 802.3 Interface Delays

### 14 N.4 Cable Delay Link Delay

15 The Cable Link Delay is the propagation delay over the transmission medium and can be approximated by 16 the following equation:

17 Cable Link Delay = Medium Length ×  $\frac{1}{BT \times v}$

18 where v is the signal propagation speed in the medium and *BT* is the bit time of the medium.

### 19 N.5 Higher Layer Delay Worst-case Delay

20 The Worst-case Delay comprises 2 parts.

21 At PFC initiator station, it is assumed a maximum sized frame just start transmission from Transmission

22 Selection when PFC is invoked. PFC frame has to wait until this in-progress frame complete transmission.

#### IEEE P802.1Q-Rev/D1.2

June 1, 2022

Draft Revision of IEEE Standard for Local and metropolitan area networks-Bridges and Bridged Networks

1 <u>At PFC receiver station, it is assumed queue is paused but a maximum sized frame just starts transmission.</u> 2 <u>Thus, bit times of the maximum sized frame is added into the total delay.</u>

3 The Higher Layer Delay comprises the delay components between the MAC Control Client and the port

4 Transmission Selection. Example of these delays are MACsee and implementation specific delays.

<sup>5</sup> For link speeds of up to 10Gb/s, MACsee constrains each of the transmit delay and the receive delay to a <sup>6</sup> maximum of 19 360 bit times (see 36.1.3.3).

7 This standard constrains the implementation specific delays to be less that 614.4 ns (see 36.1.3.3). This 8 delay is equivalent to 6144 bit times at the speed of 10Gb/s.

## 1 N.6 Buffer allocation Computation example

<sup>2</sup> A station needs to be capable of buffering DV bit times of data to ensure no frame loss due to congestion. <sup>3</sup> The worst case is with a 10GBASE-T PHY. Assuming MACsec is not supported, this results in the <sup>4</sup> following:

- 5 <u>PFC frame generation: 200 bit times;</u>

- 6 Maximum envelope frame size: 2000 octets, 16 160 bit times;

- 7 PFC frame size: 64 octets, 672 bit times;

- 8 XGMII MAC/RS and XAUI interface:  $8192 + 2 \times 2048 = 12288$  bit times;

- 9 10GBASE-T Delay: 25 600 bit times;

- 10 100 meters Cat6 cable: 5556 bit times (computed assuming  $v = 0.6 \times c$ , where c is the speed of the

- 11 light in meters per second);

- 12 <u>Entering paused state</u> HD = 6144 bit times

13 The total Delay Value in this scenario results as follows:

- 14  $DV = 2 \times (Max Frame) + (PFC Frame) + 2 \times (Cable Delay) + 2 \times ID + HD_{s2}$

- 15  $DV = 2 \times (16\ 160) + (672) + 2 \times (5556) + 2 \times (25\ 600) + 2 \times (12\ 288) + 6144 = 126\ 024\ bit\ times$

- $16 \qquad \underline{DV = ID_1 + WD_1 + LD_2 + ID_3 + WD_4 + ID_4 + LD_5 + ID_6}$

- 17  $DV = (200) + (16\ 160) + (672 + (12\ 288 + 25\ 600)\ /2) + (5556) + ((12\ 288 + 25\ 600)\ /2 + 6144) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 160) + (16\ 1$

- 18 160 + ((12 288 + 25 600) /2) + (5556) + ((12 288 + 25 600) /2) = 126 224 bit times

<sup>19</sup> For this case, the amount of buffering needed to ensure no frame loss due to congestion results to be <sup>20</sup> <del>126 024</del> <u>126 224</u> bit times, roughly equivalent to <del>15.5</del> <u>15.4</u> kB. <u>30.8kB is allocated to PFC enabled priority</u> <sup>21</sup> <u>queue.\_XON/XOFF threshold is set to 15.4kB. So PFC guarantees no frame loss and no throughput loss.</u>

22 If MACsec is used <u>for user data</u>, WD1 and ID4, each <del>the High Layer Delay</del> is incremented by 19 360 bit 23 times; therefore, the total Delay Value results as follows:

- 24  $DV = 2 \times (16\ 160) + (672) + 2 \times (5556) + 2 \times (25\ 600) + 2 \times (12\ 288) + 25\ 504 = 145\ 384\ bit\ times$

- $DV = 126\ 224 + 19\ 360 + 19\ 360 = 164\ 944\ bit\ times$

<sup>26</sup> For this case, the amount of buffering needed to ensure no frame loss due to congestion results to be <sup>27</sup> <del>145</del> <del>384</del> <u>164</u> <del>944</del> <u>944</u> bit times, roughly equivalent to <del>18</del> <u>20</u> kB. Similar as non-MACsec case, <u>40kB is allocated</u> <sup>28</sup> <u>to PFC enabled priority queue. XON/XOFF threshold is set to 20kB.</u>

29