# Backfeed v250

### Info (not part of baseline)

## Changelog:

### v250 Changes:

- Fix typo's in 145.3.2 and 145.3.5

- Fix wrong Table reference in 145.2.10.3a (should be 16, was 20)

- New attempt at describing what reverse current is + simplified requirement

### v240 Changes:

- Added general PD requirement to meet detection, pd signature configuration, and classification requirements under 3-pair condition.

- Clarifications to PD signature configurations 145.3.5

- v230 Added PSE requirement to limit current to I<sub>rev</sub>, different level depending on V<sub>PSE</sub>, PD 3P spec reduced to detection range only.

### v220 Changes:

- Replace the construct "are not required" by "may" (both in PD and PSE section)

- Replace "cause current to flow" by "source" (unless the PD is sourcing power, it's impossible for current to be sunk into a negative pair).

- Only allow 3P-backfeed from 21 V and up for PDs, but exclude 3P-after-4P

- Cleanup of PSE requirement (got rid of incomprehensible 'range of potentials')

- v212 As presented during the ad-hoc call of May 7

### 145.2.4 PSE PI

A PSE device may provide power via one or both of the two valid four-conductor connections, named pairsets. A pairset consists of a pair at the positive  $V_{PSE}$  and a pair at the negative  $V_{PSE}$ . The two conductors associated with a pair each carry the same nominal current in both magnitude and polarity. Figure 145–12, in conjunction with Table 145–3, illustrates the pairsets, which for PSEs are named Alternative A and Alternative B.

PSE are required to switch the negative pairs, and may switch the positive pairs as defined in 145.4.1.1.1. This may lead to both positive pairs providing current in 2-pair mode.

### 145.2.10 Power supply output

# Add new item to Table 145–16 as follows:

Item 17a

Parameter Unpowered negative pair sourced current

$\begin{array}{ccc} \text{Symbol} & & I_{rev} \\ \text{Unit} & & A \\ \text{Min} & & -- \end{array}$

$\begin{array}{ll} \text{Max} & 0.0013 \text{ (split: when highest } V_{PSE} > 21 \, \text{V}) \\ \text{Max} & 0.0005 \text{ (split: when highest } V_{PSE} \leq 21 \, \text{V}) \\ \end{array}$

PSE Type 3, 4

Additional information See 145.2.10.3a

#### Insert new subclause after 145.2.10.3 as follows:

### 145.2.10.3a Reflected voltage

When a 4-pair capable PSE provides power in 2-pair mode, whereby two pairs are connected to the positive  $V_{PSE}$ , and one pair is connected to the negative  $V_{PSE}$ , a single-signature PD may reflect a voltage of up to  $V_{PSE}$  back onto the unpowered pairset. See 145.3.8.8. This can cause a reverse current to flow, named  $I_{rev}$ , defined in Table 145–16. Reverse current is any current that flows between two negative pairs.

The PSE shall not source a current higher than  $I_{rev}$ , as defined in Table 145–16. This requirement holds only when no power is being sourced into the PSE.

### 145.3.2 PD PI

. . .

A PD shall meet the requirements of detection (145.3.4), PD signature configuration (145.3.5), and PD classification (145.3.6) in any valid 2-pair configuration, as defined in Table 145-20.

NOTE—this includes configurations with two pairs connected to the positive  $V_{PD}$  and one pair connected to the negative  $V_{PD}$ .

A single-signature PD shall meet all specifications related to current by meeting the specified total current, where total current is the combined current of the two pairs at the same polarity, unless otherwise noted (see 145.3.8.9). A dual-signature PD shall meet all specifications related to current by meeting the specified current on the negative pair of a given Mode, unless otherwise noted (see 145.3.8.9).

• •

# Change the note at the bottom of Table 145–20 as follows:

PSEs are required to switch the negative pairs, but not required to and may switch the positive pairs as defined in 145.4.1.1.1. This may lead to both positive pairs providing current in 2-pair mode.

# 145.3.5 PD signature configurations

A single-signature PD shall present a valid detection signature, as defined in Table 145–21, on a given Mode when no voltage or current is applied to across the other Mode, and shall not present a valid detection signature on the given Mode when any voltage in the range of 3.7 V to 57 V is applied to across the other Mode or any current greater than 124 µA is applied to drawn from the negative pair of the other Mode. These requirements apply to both Mode A and Mode B.

NOTE—A valid detection signature meets every requirement in Table 145–21 across all specified conditions. A failure under any allowed condition is considered "not a valid signature."

A dual-signature PD shall present a valid detection signature, as defined in Table 145–21, on a given Mode, regardless of any voltage between 0 V and 57 V applied to the other Mode. This requirement applies to both Mode A and Mode B.

These requirements allow the PD to be correctly identified by a PSE performing connection check as defined in 145.2.7.

# 145.3.8 PD power

Change item 18 such that:

- Parameter: Reflected voltage

- Symbol: V<sub>refl</sub>

### 145.3.8.8 Backfeed Reflected voltage

### Replace the contents of 145.3.8.8 as follows:

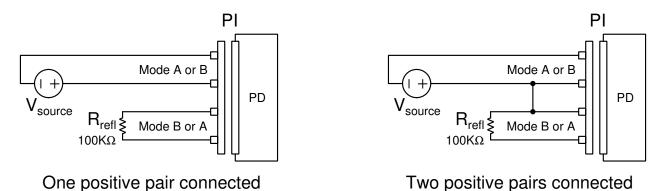

For a single-signature PD, when any voltage in the range of 0 V to  $V_{Port.PD-2P}$  max is applied per any of the valid 2-pair configurations, defined in Table 145–20, that have only a single pair connected to positive  $V_{PSE}$  (see Figure 145–29a), the voltage on the Mode not connected to the voltage source, with a 100 k $\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29.

For a single-signature PD, when any voltage in the range of  $0\,\mathrm{V}$  to  $10.1\,\mathrm{V}$  is applied per any of the valid 2-pair configurations, defined in Table 145–20, including those with two pairs connected to positive  $V_{PSE}$  (see Figure 145–29a), the voltage on the Mode with at least one pair not connected to the voltage source, with a  $100\,\mathrm{k}\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29. This requirement does

not apply if a voltage greater than  $10.1\,V$  has been applied on either Mode until the voltage on both Modes has been less than  $V_{Reset}$  for at least  $T_{Reset}$ .

For a dual-signature PD, when any voltage in the range of 0 V to  $V_{Port.PD-2P}$  max is applied per any of the valid 2-pair configurations, defined in Table 145–20, including those with two pairs connected to positive  $V_{PSE}$  (see Figure 145–29a), the voltage on the Mode with at least one pair not connected to the voltage source, with a  $100 \, k\Omega$  resistor connected across that Mode, shall not exceed  $V_{refl}$  as defined in Table 145–29.

Figure 145-29a — Reflected voltage requirements

Update PICS to reflect changes.