# User Perception of 10GBASE-T Training time/Time-To-Link

IEEE P802.3bq 40GBASE-T Task Force

Pete Cibula, Intel Dave Chalupsky, Intel

PHY Baseline Proposal Ad Hoc – 27 February 2014

## What is Time-To-Link (TTL)?

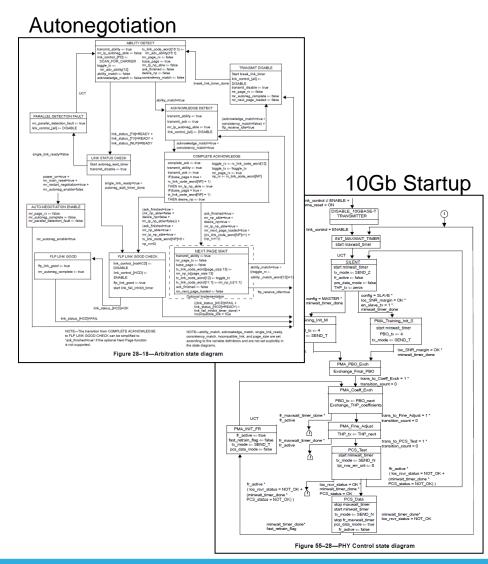

- Time-To-Link (TTL): A system performance metric that characterizes and measures PHY behavior through autonegotiation and the 10GBASE-T startup sequence

- Defined in 802.3 Clause 28,

"Physical Layer link signaling for Auto-Negotiation on twisted pair" and 802.3 Clause 55, Subclause

"55.4.2.5.14 Startup sequence")

- One of two primary performance measures (along with BER) used to characterize 10GBASE-T physical layer link interoperability

## Why is it Important?

- Server networking drivers must meet 3<sup>rd</sup>-party certifications

- Example Windows Hardware Quality Labs (WHQL) testing & certification "devfund"

- A series of "device fundamentals" tests to evaluate the compatibility, reliability, performance, security and availability of a device in Windows OS

- Includes many automated driver stress tests that execute multiple device resets

- Long link times appear as a "failure" to these tests, which expect a link in 3s-4s based on 10Mb/100Mb/1Gb

PHY performance

Server device fundamentals requirements Test Applicability Matrix Mapping of Tests to Various Operating Systems Server 2008 R2 **Device Fundamentals Tests** Vista Common Scenario Stress with IO Sleep Stress With IO **V** Disable Enable With IO Device Path Exerciser Run INFTest against a single INF Plug and Play Driver Test Embedded Signature Verification Reinstall With IO CHAOS - Concurrent Hardware & OS Device Install Checks (2 tests) ~ IO Cancellation Tests (2 tests) WDF Tester Dynamic Partitioning Multiple Processor Group

Source: Device Fundamentals Overview Presentation at <a href="https://linear.nlm.nih.gov/">https://linear.nlm.nih.gov/</a>

Long TTLs (>6s) can lead to device certification failures!

#### Link Interoperability Measurements

- Representative Link Interoperability metrics associated with TTL

- Time-To-Link (Time to achieve link after link initiation event)

- # Link Attempts (Number of attempts for each link)

- # Link Drops (Number of link drops observed after link is established)

- Clock Recovery (Master/Slave resolution)

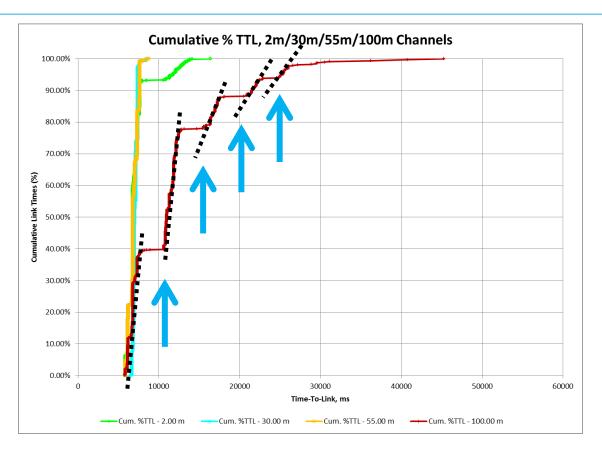

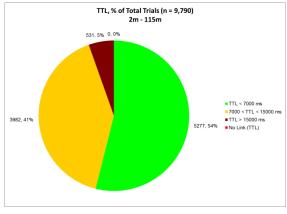

- TTL Distribution (% of links by link time)

- Speed Downshift/Downgrade (Resolved speed if other than 10Gb/s)

- Variables that can affect TTL

- Channel (type, configuration, length)

- Link initiation event on either endpoint

- Hardware reset, "soft" reset or MDIO PHY reset, autoneg restart, transmitter disable/enable, cable connect/disconnect

#### Time-To-Link Levers?

- TTL is a combination of both autonegotiation and 10Gb startup behavior

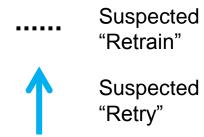

- Two sources of variability? "Retrain" (variability through 55.4.6.1) and "Retry" (return to 28.3.4)

- Longest TTLs typically driven by multiple passes through the Clause Arbitration state diagram after failed training attempts

#### Considerations for 40GBASE-T

- Can autonegotiation and 40GBASE-T startup times be improved to be consistently less than or equal to 6s?

- Improved loop timing?

- Changes in 10GBASE-T startup state timing?

- Example Simple PBO scheme similar to that proposed in Wu\_01a\_0214\_802.3bq\_adhoc.pdf

- Others?

Version 2.4

# Thank You!