## Hari Word Stripe Coding I ssues & Status

Mike Jenkins

LSI Logic Corp.

# Why Word Striping instead of Byte (Column) Striping?

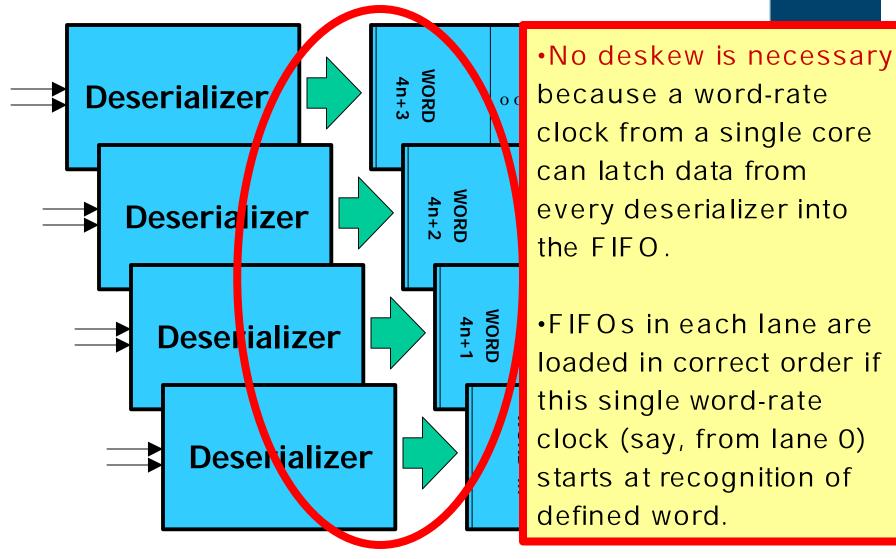

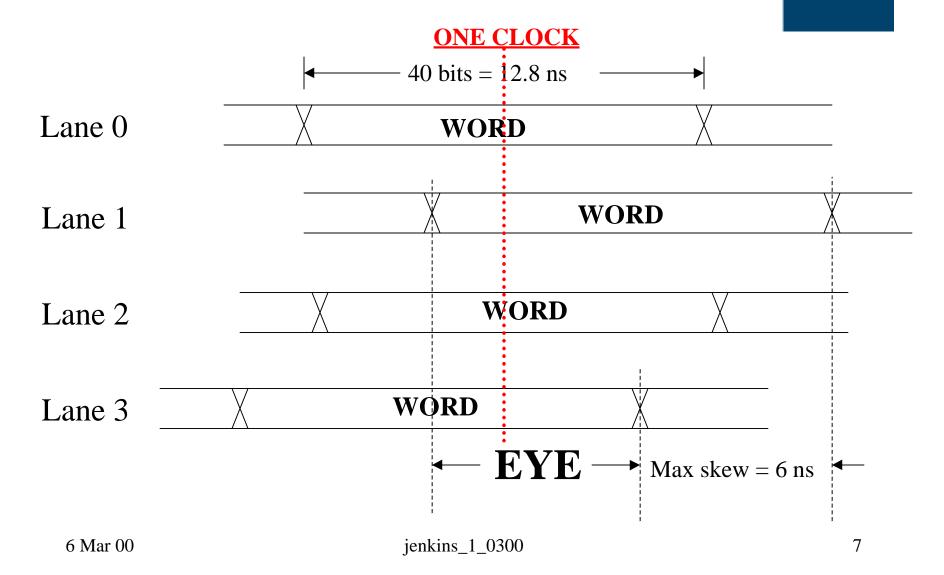

- Word striping avoids need to deskew

- Technical risks of byte deskew are at least comparable to clock-matching EFIFO design (for which several implementations suffered flaws)

- Word striping avoids need for high speed, byte rate (320 MHz) clocks

- Word striping allows more deletable characters in IPG

### Correcting some misinformation...

- Statement in taborek\_1\_0100 that "Word Striping requires commas in (WAN PHY) Preamble" is not true.

- Neither striping scheme modifies packet data

- For either coding scheme, Hari is an "XMII extender", so following layers (e.g., 64b/66b) are independent.

4

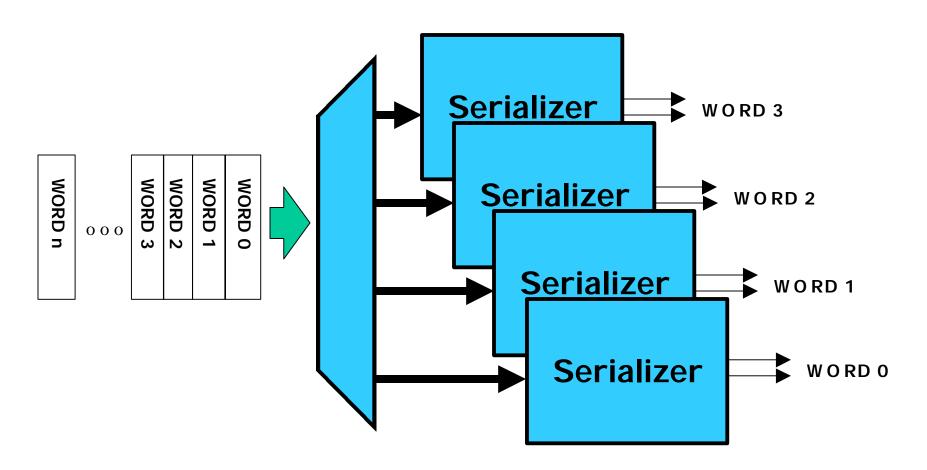

#### 10G Architecture (Ser)

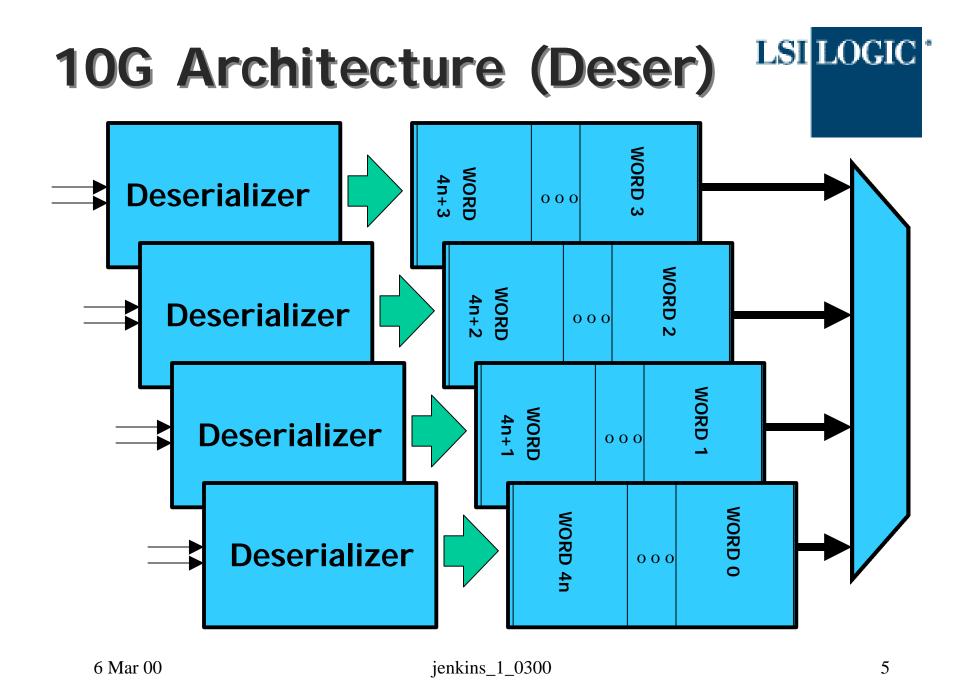

#### 10G Architecture (Deser)

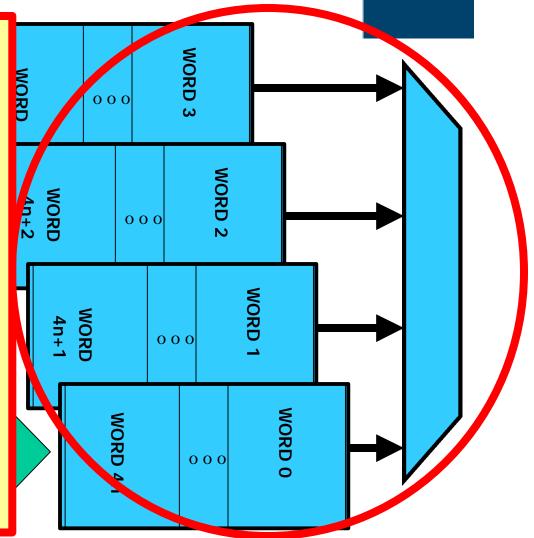

#### **Word Striping**

#### 10G Architecture (Deser)

4 FIFOs vs. 1 FIFO is solely a matter of memory organization. That is, the four lane FIFOs can be viewed as a single FIFO, written by a single recovered clock and read by the local clock.

Therefore, the exact same elasticity algorithm that was proven for 1G and 2G designs can be used for 10G designs.

LSI LOGIC

#### Summary

- Design work proceeding on both coding schemes (word & column striping)

- Word striping extends much more directly from existing designs

- Recommendation: reserve judgement until thorough hardware results are available

- References: ritter\_1\_1199, jenkins\_1\_1199