# Technical Study: Resistive Discovery for Power over MDI

Roger Karam, Cisco Systems rkaram@cisco.com

#### **DETECTION SPEC ANALYSIS**

- Verified the work of Rick Brooks

- Used SPICE and behavioral modeling

- Monte Carlo analysis for a feel on the spec windows

- Goal is to raise concerns and run them by the group...

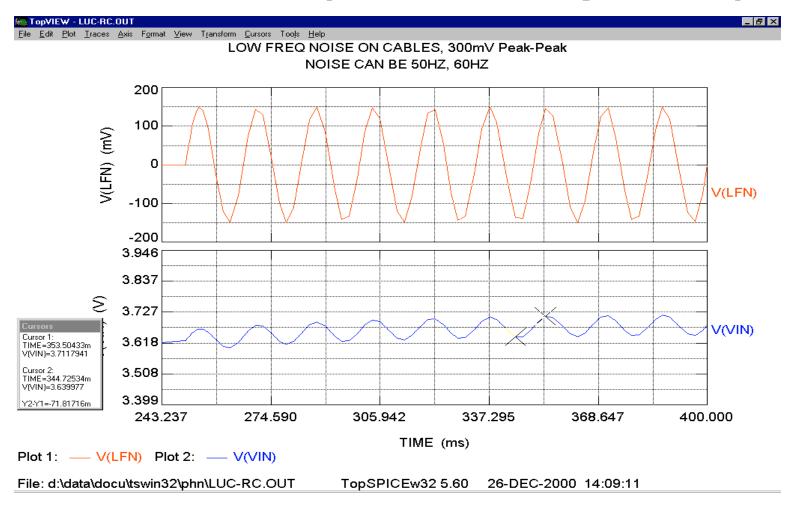

#### Capacitance vs. Discovery Time

Looking into the capacitance effect on the detection scheme, and the low frequency (50-60Hz) issue

# Settling Time For a Single Detection Voltage

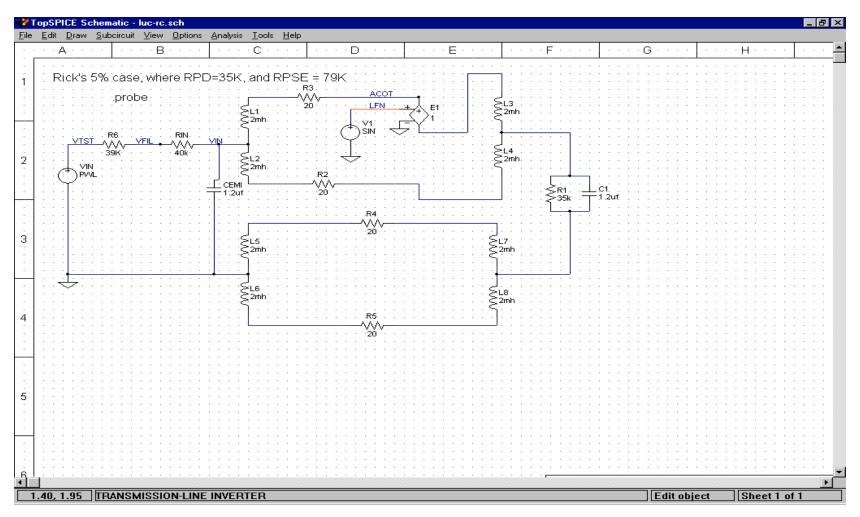

Rick's 5% TOLERANCE CASE, AND 20% 1UF PD CAPACITOR 268ms needed to settle to 1%

Plot 1: — V(VTST) Plot 2: — V(VIN)

File: d:\data\docu\tswin32\phn\LUC-RC.OUT TopSPICEw32 5.60 26-DEC-2000 13:53:56

Using a 20% capacitor tolerance and 5% resistor tolerance It takes 268ms to settle to 1%

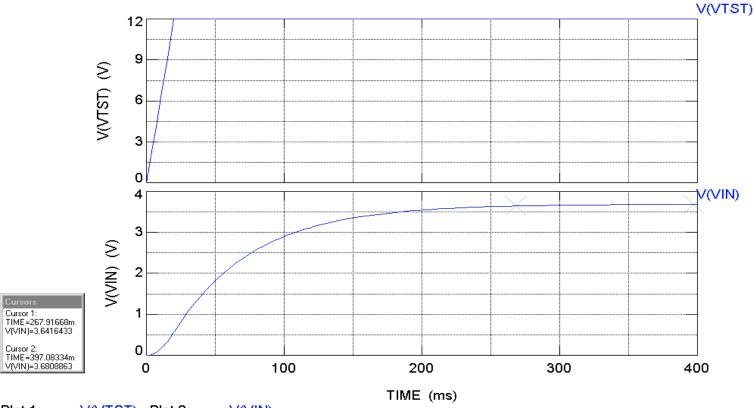

### **Effect Of Low Frequency Noise**

300mv at 60HZ was injected into the Cable (simulated with a 20ohm resistor per wire)

# About 72mV Is Seen Back At The PSE SIDE (3V & 6V expected)

We see around 72mV at the PSE side This is about 2.4% for a 3V Level

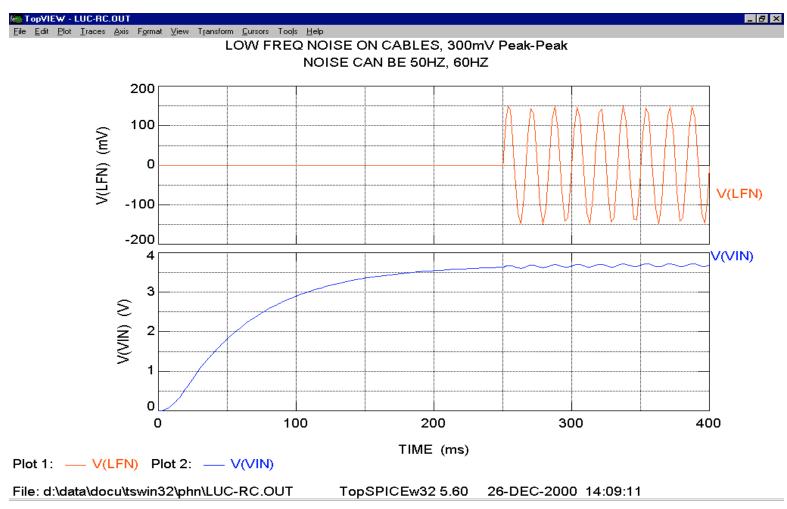

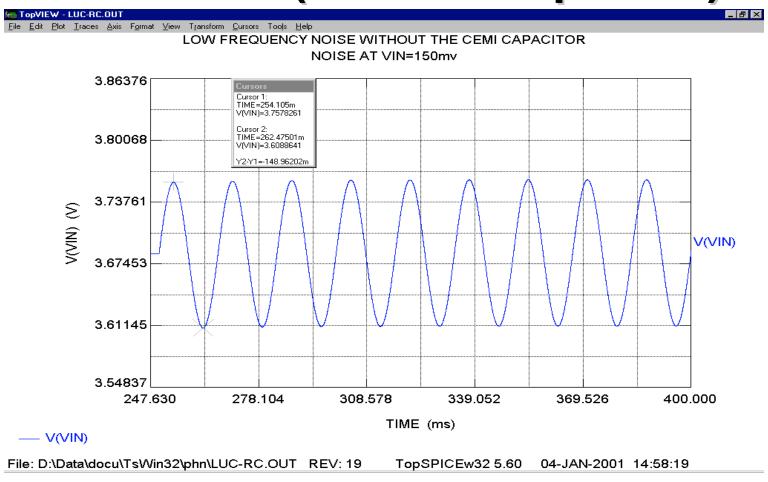

# About 150mV Is Seen Back At The PSE SIDE (3V & 6V expected)

We see around 150mV at the PSE side This is about 5% for a 3V Level When CEMI is removed from the circuit - 300mv/60-Hz on the wire peak-peak

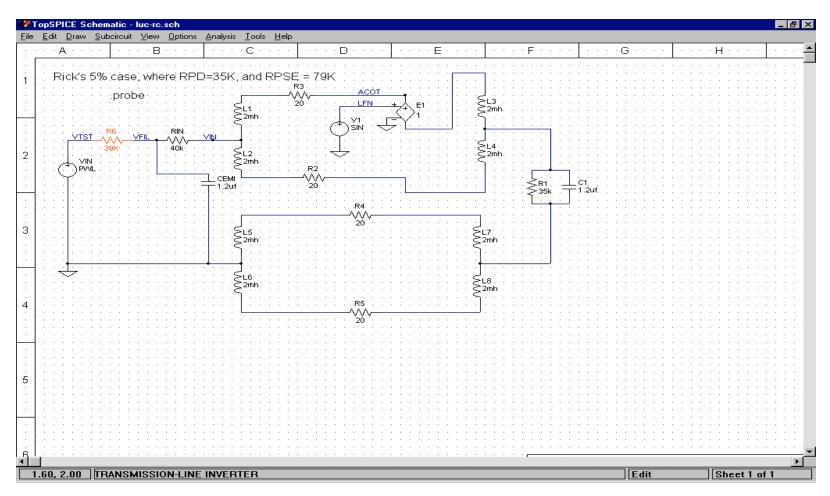

#### **Used A LOW PASS Filter**

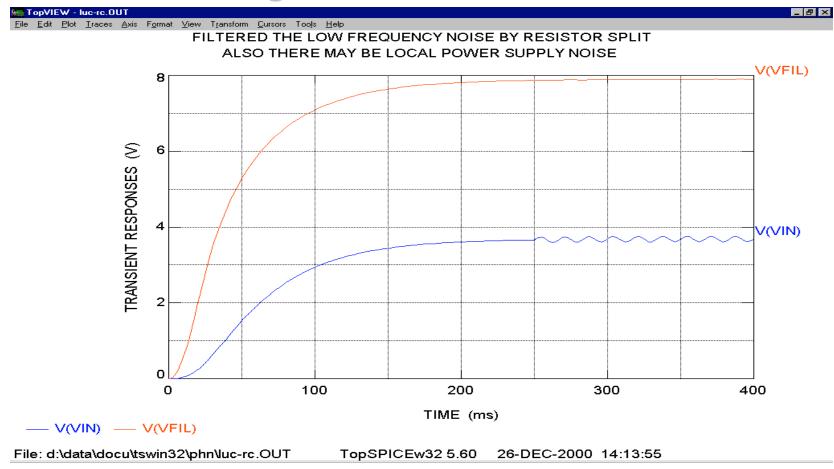

I Split the 75K resistor to Filter the Noise going Into the PSE, which helps. But the Detection Time may go out of control

# The Filter Helps, But Calls For a Change In Measurement

As visible V<sub>FIL</sub> has barely any noise on it...

But we would have to measure a higher voltage

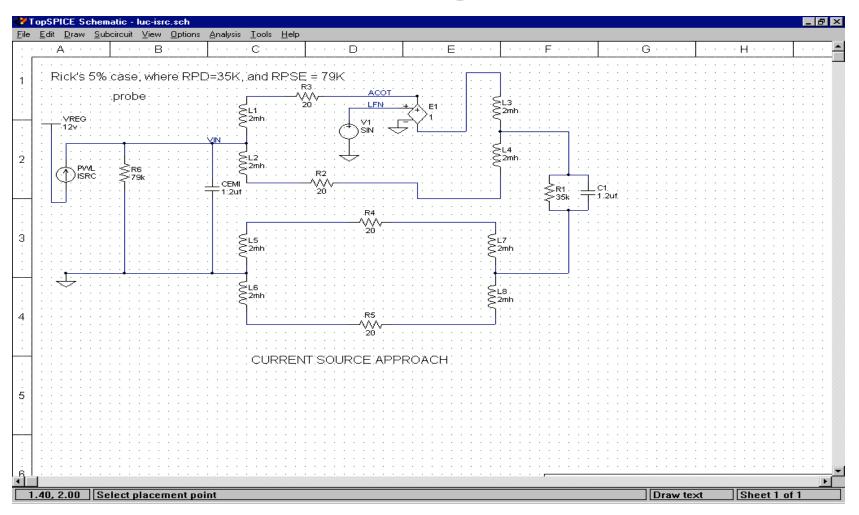

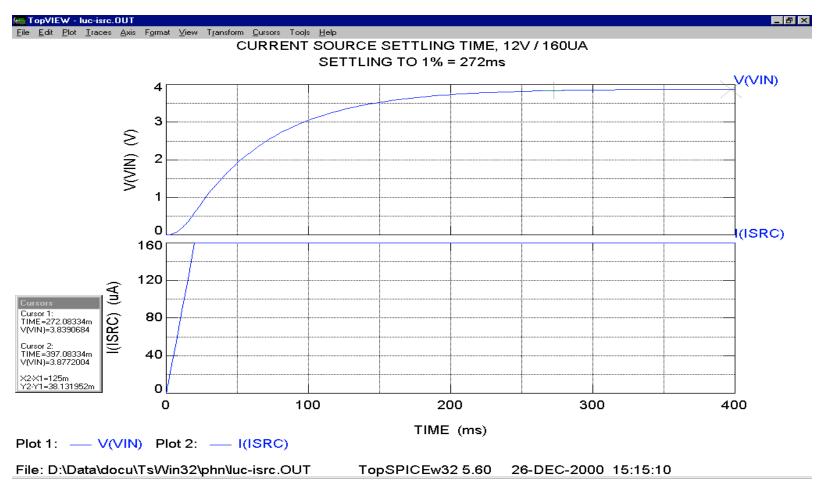

### Current Source Increases Detection Time??

**A Current Source Increases Detection Time Slightly?**

### Detection Time Slightly Increases With A CURRENT SOURCE

#### **Detection Time increased by 4msec**

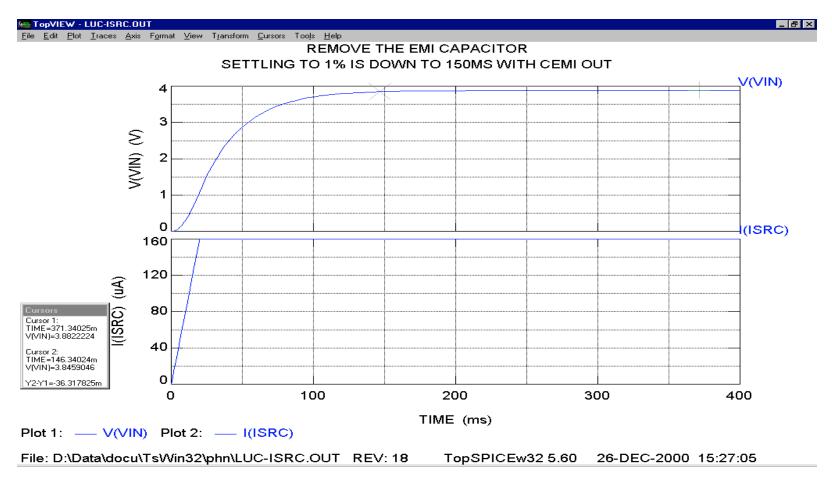

### Reducing Detection Time

Effect of Capacitance on Detection Time: Almost Cut in Half when the PSE Capacitor was removed.

#### Window Needed Around Thresholds

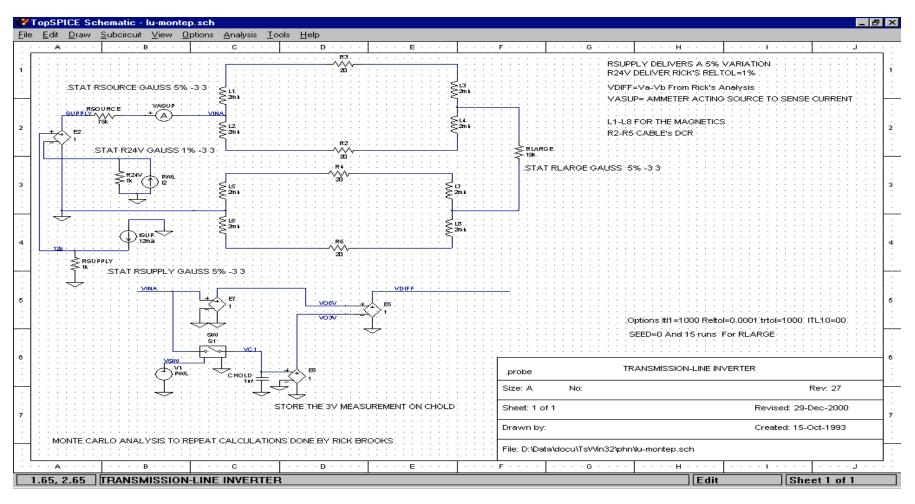

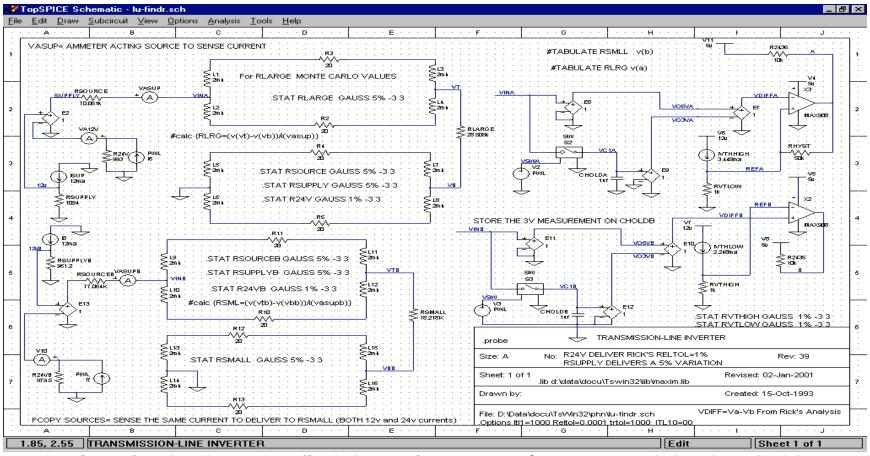

Did a Monte Carlo Analysis to find  $V_{\text{TH}(\text{MIN})}$  and  $V_{\text{TH}(\text{MAX})}$  of the window comparator.

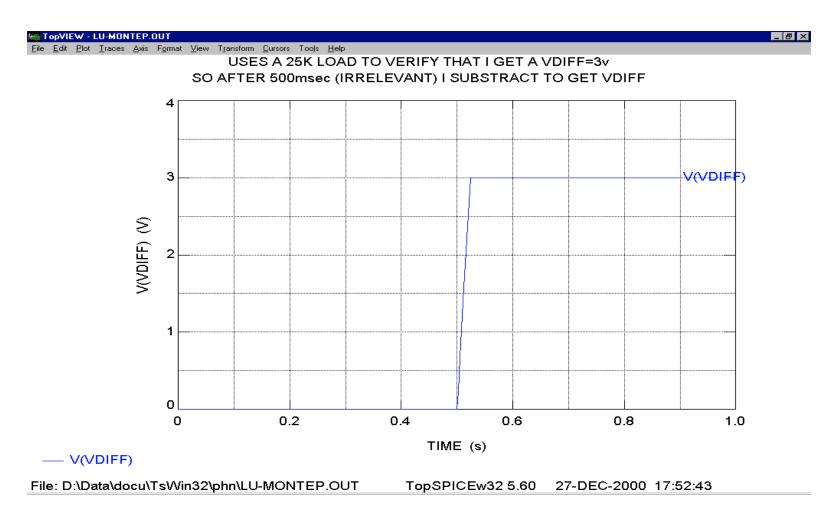

### Show Me The Voltage

### Pointing to the 3v $V_{DIFF}$ expected after subtracting the 6V from the 3V across the 25k resistor

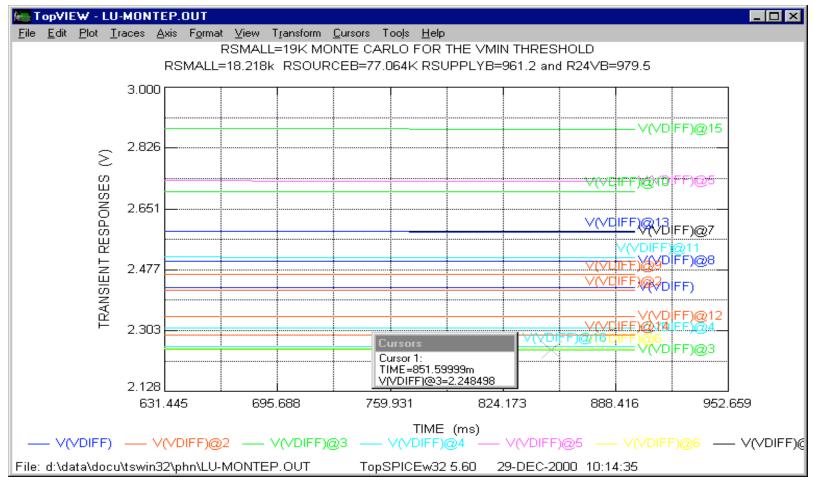

#### Using 19K From The AVAYA Spec To Find Threshold Windows

The Lowest Voltage for  $V_{TH(MIN)} = 2.248$  — Close to Rick's 5% Case of 2.194v

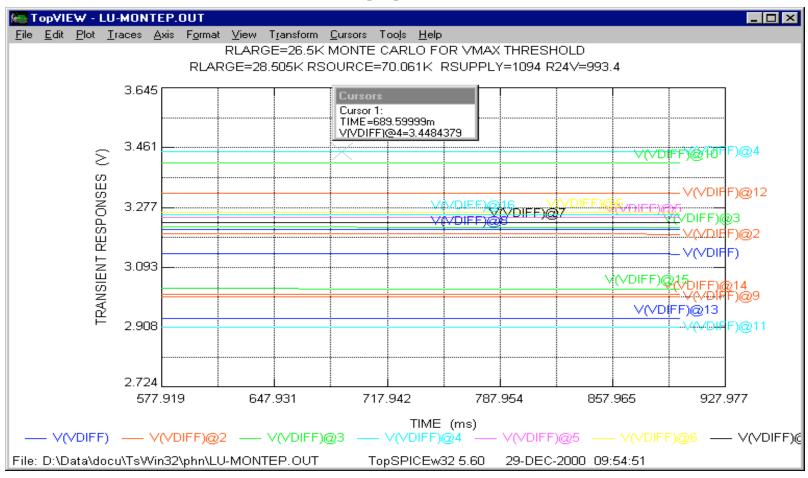

# Used 26.5k From AVAYA's Spec To Find The Upper Threshold

The Highest Voltage For the Window Comparator and the 5% case is 3.448v. Rick found it to be 3.45v

# Knowing Thresholds, What Resistor Range Is Needed For A 5% Spec?

- Again going backward to find the resistor-range/spec around the thresholds using a Monte Carlo analysis.

- I also added a 1% spec around the window comparator thresholds and last added hysteresis to see the effects.

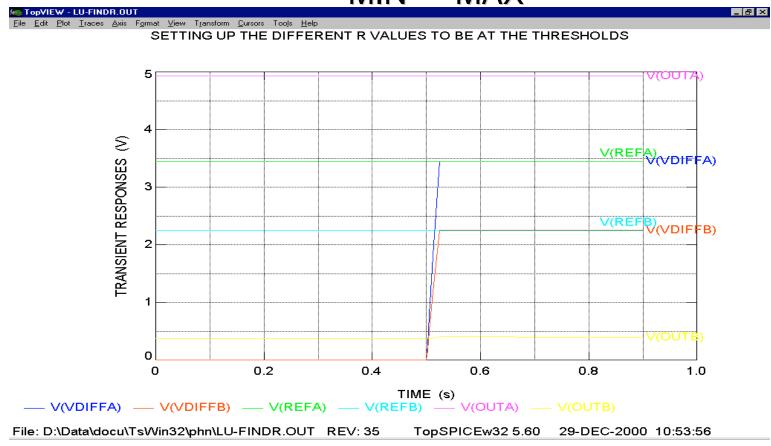

# Threshold Setup With $V_{THMIN}/V_{THMAX}$ And $R_{MIN}/R_{MAX}$

Showing the thresholds and the fact that the starting resistors cause  $V_{DIFF}$  to land right at the threshold. Thus, any resistors greater or lower in value must be rejected — but things move, so what is the window required?

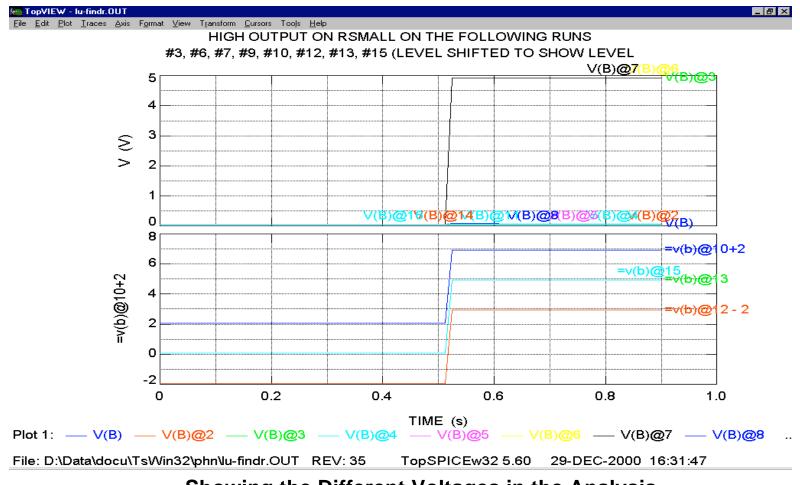

### Finding The Range Around R<sub>MIN</sub>

Showing the Different Voltages in the Analysis.

Next Slide shows the Resistor Values.

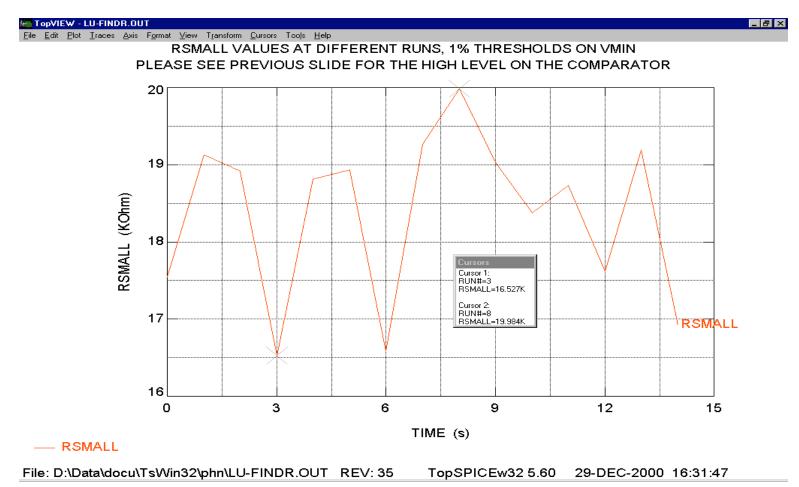

### The Range Around R<sub>MIN</sub>

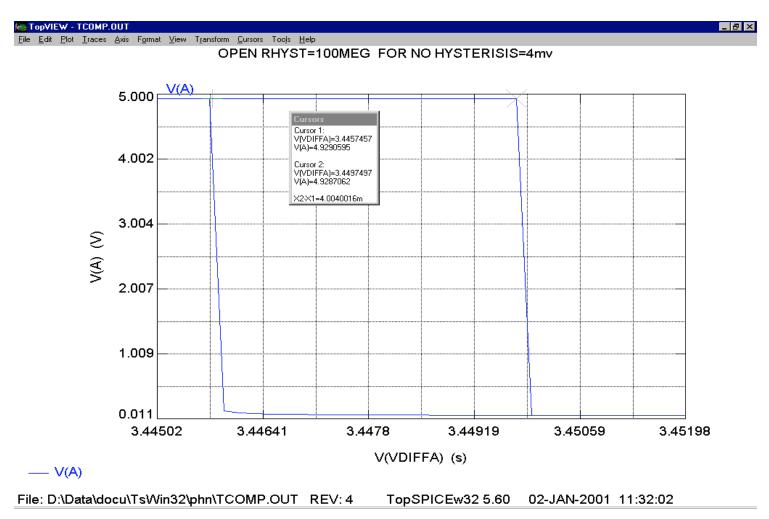

Range = 16.5k-20K Hysterisis is 4mv on the comparator.

Rick's calculations shows 14.8k-19k

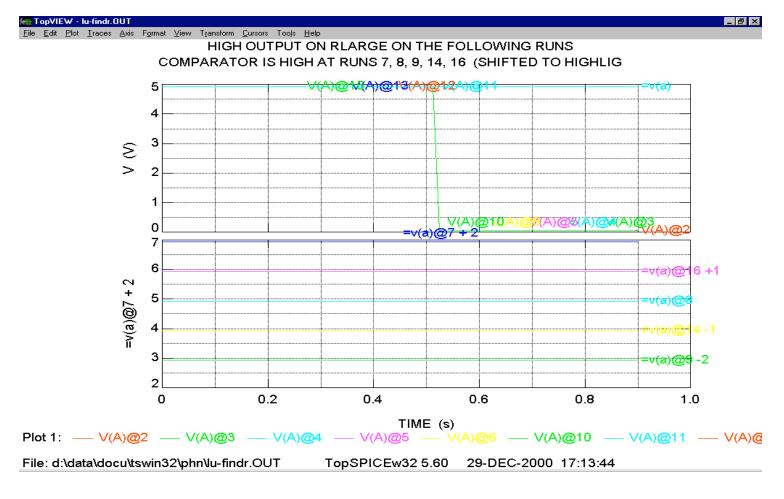

### Finding The Range Around R<sub>MAX</sub>

Showing the Different Voltages in the Analysis.

Next Slide shows the Resistor Values.

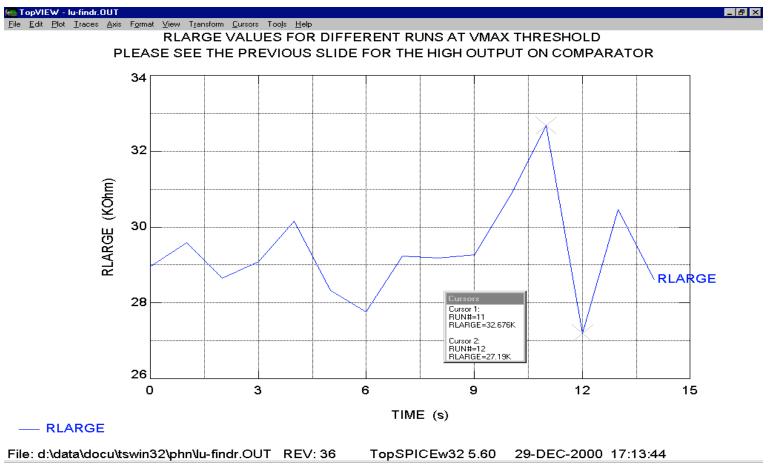

### The Range Around R<sub>MAX</sub>

Again For the 5% case from Rick's work added a 1% Threshold variations. Hysteresis is at 4mV. The resistor range found is 27k-32.6k Rick's calculations show 26.5k-34.6k, I am in agreement with Rick and the numbers are approximations...

### Hysterisis = 4mV as is

Without Added Hysteresis the Comparator has about 4mV

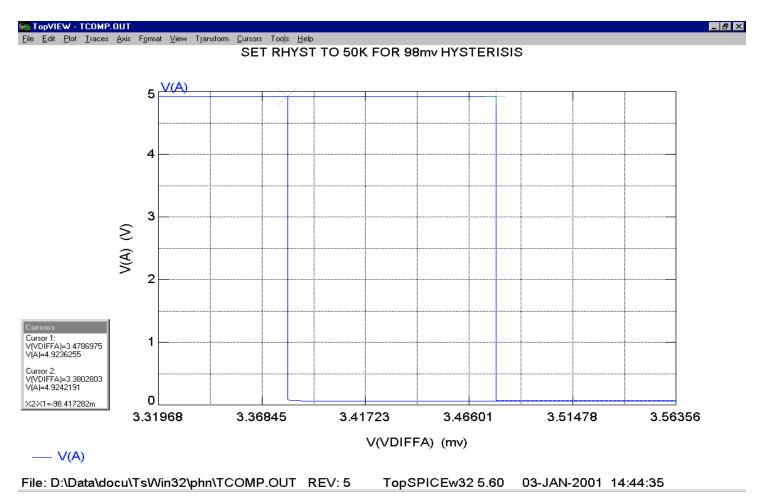

### Hysterisis = 98mV@ 50K R<sub>HYST</sub>

Changed R<sub>HYST</sub> from 100Meg to 50k to Increase The Comparator's Hysteresis to 98mV

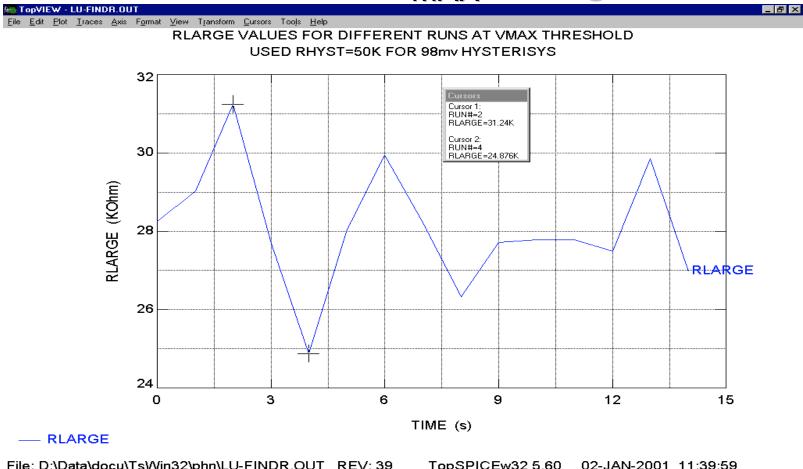

### Set The Hysteresis = 98mV & Find The New R<sub>MAX</sub> Range

File: D:\Data\docu\Ts\Win32\phn\LU-FINDR.OUT REV: 39

With Hysteresis = 98mv on the Comparator, the Latest  $R_{LARGE}$  range becomes 25k-31k

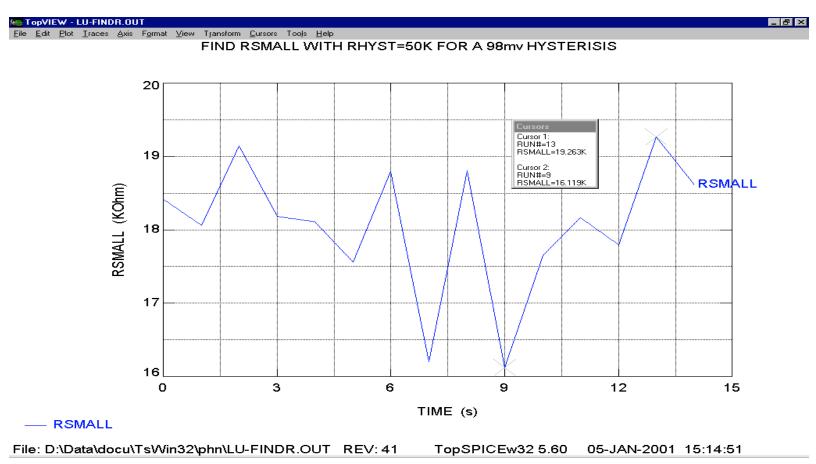

### Set The Hysteresis = 98mV & Find The New R<sub>Min</sub> Range

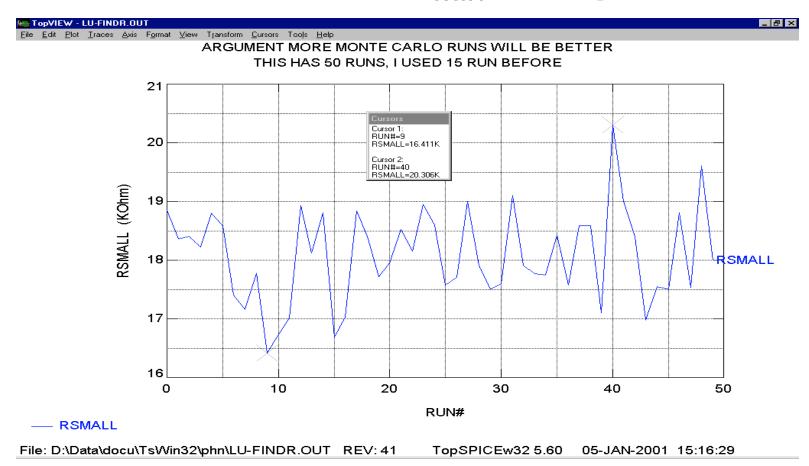

With Hysteresis = 98mv on the Comparator, the Latest  $R_{LARGE}$  range becomes 16k-19k

### Set The Hysteresis = 98mV & Find The New R<sub>Min</sub> Range

I have been using 15 run for Monte Carlo, Now I did 50 Runs Duplicating the Previous slide...

### Set The Hysteresis = 98mV & FindThe New R<sub>Min</sub> Range

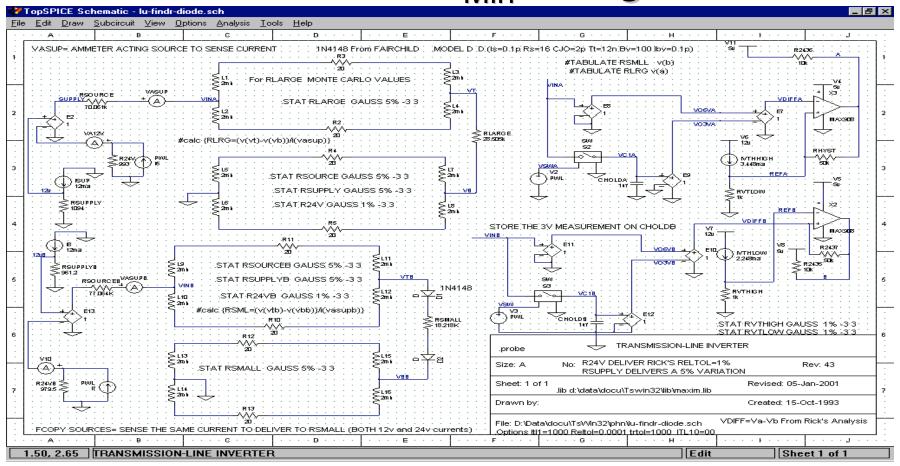

Schematic to Show addition of 2 - 1N4148 series diodes and 50K resistor for a 98mv hysterisis around the Rmin comparator.

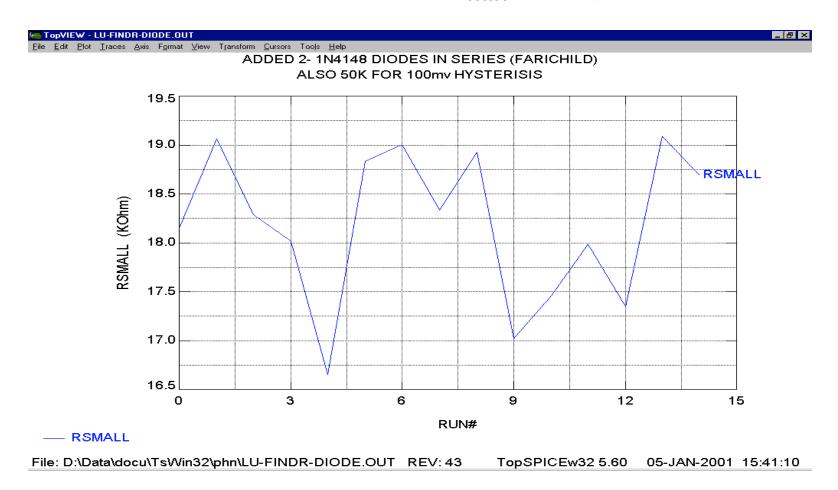

### Set The Hysteresis = 98mV, Add 2-Diodes & Find The New R<sub>Min</sub> Range

Finding Rmin with 98mv Hysterisis and 2-Series Diodes

#### **Observations And Conclusions**

- Agree with Rick's analysis (verified the 5% case)

- Cannot have a 1% spec on some design parameters some margin must be left for the system

- Low Frequency Noise does not Appear to be an issue but given that the noise can be 50-60Hz, now is the time to look into it because any filtering may slow down the detection. Latest simulation Shows a 5% error- No cap.

- Capacitance around these High R values will Slow the detection down. If a Switch is a must in the PD, can the capacitance be on the DC/DC side? In the PSE if we clamp the Voltage to 12v as we vary the current (double it) could this be of help avoid charging the cap to 24v, there can always be a cap at the supply side of the FET.

#### **Observations And Conclusions**

- Analog vendors recommend we increase detection current to at least 1ma.

- Advantages:

- \* Better noise immunity

- \* Less Sensitivity to Leakage

- \* Handy in Micro-Power Applications

- Drawback:

- \* Excessive current may cause Damage?!

- Spec The PSE with 2 parameters to allow ease of Current -Source based detection:

- \* An Open Circuit Voltage

- \* A Short Circuit Current

#### **Observations And Conclusions**

- Can we explore having a limited number of sub-classes?

- This if anything fits under "flexibility," and may come in handy one day in excluding a set of devices, or helping us avoid a gotcha we may have overlooked. Flexibility has value, though we are in a rush to wrap this up...

- Please note that no supply, aging, temperature variations were considered here for AVAYA has budget for them

- Concern that for the sake of finishing the standard we set ourselves up for future problems.