# Proposal for Transmitter Electrical Specifications

#### IEEE P803.2an Task Force Vancouver, January '05

Chris Pagnanelli, Solarflare Communications

#### **Objectives**

- Establish Transmitter Electrical Specifications

- Peak differential output voltage (paragraph 55.5.3.1)

- Maximum output droop (paragraph 55.5.3.2)

- Transmitter linearity (paragraph 55.5.4)

- Transmitter PSD and power level (paragraph 55.5.6)

- Transmitter clock frequency (paragraph 55.5.7)

- Specifications Based on Interoperability Requirements

- Electrical specifications that affect interoperability are normative

- Primary requirement is > 37 dB transmit SNR

- Corresponds to < 0.2 dB implementation loss at receiver</li>

- Electrical specifications that go beyond interoperability restrict ability of manufacturers to optimize performance

#### **Objectives**

- Specifications Tied to Objective Measurements

- Measurements should be possible with commerical lab equipment

- Errors due to lab equipment accuracy must be negligible

- Measurement procedures must be unambiguous

- Elaborate custom test fixtures should not be required

### **Basis for Output Voltage Specification**

- Output Voltage Range of 2.25 Vpp <u>+</u> 10%

- Corresponds to output power range of 4.0 dBm to 5.7 dBm (with transformer loss)

- Required Specification

#### 55.5.3.1 Peak differential output voltage

When transmitting the Test 1 waveform (i.e., repeating pattern of ten +16 symbols followed by ten -16 symbols) into a  $100\Omega$  differential resistive load, the peak-to-peak differential voltage at the MDI output shall be 2.25 V ± 10% at a point 10 nsec after the zero crossing.

# **Basis for Output Voltage Specification**

- Compatible with Required Output Power Levels

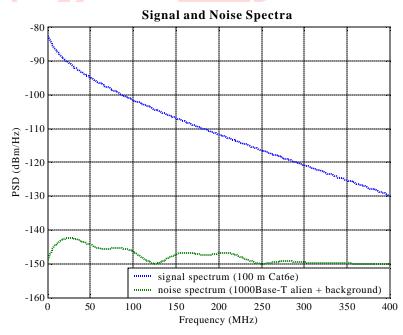

- Power > 4 dBm needed for > 37 dB SNR on 100m Cat6e

- Based on optimal DFE calculation with 1000BASE-T ANEXT and –150 dBm/Hz background noise

- Class E, 100 m ANEXT limit line applied to 1000BASE-T output PSD (1.5 Vpp before filtering)

# **Basis for Output Voltage Specification**

Compatible with EMI Compliant PSD Masks

# **Transmitter Droop Specification**

#### Required Specification

#### 55.5.3.2 Maximum output droop

When transmitting the Test 2 waveform (i.e., repeating pattern of sixty-four +16 symbols followed by sixty-four - 16 symbols) into a  $100\Omega$  differential resistive load, the magnitude of both the positive and negative droop shall be less than 10% over a period of 0.08 µsec beginning at a point 10 nsec after the zero crossing.

# **Basis for Droop Specification**

- Requirement Based on 200 kHz Line Transformer HighPass Response

- At least one transformer manufacturer has demonstrated lower corner frequency of 100 KHz on prototype design

- Provides margin for manufacturing tolerances

- 800 nsec effective time constant

### **Transmitter Linearity Specification**

#### Required Specification

#### 55.5.4 Transmitter linearity

When in Test mode 4 and transmitting on a single pair into a  $100\Omega$  differential resistive load, the signal to noise plus distortion ratio of the differential signal at the MDI output shall be greater than the values given in the following table. For two-tone sinusoids, signal power shall be defined as the total (sum) power of both tones. Signal to noise plus distortion ratio measurements shall be made over an effective integration time interval of not less than 10 msec and not more than 100 msec.

# **Transmitter Linearity Specification**

#### Required Specification (cont.)

Signal to Noise Plus Distortion Requirements

| Output Waveform Frequencies           | SNDR Specification (dB) |

|---------------------------------------|-------------------------|

| Single tone:                          |                         |

| (101/1024)*800 MHz                    | 38                      |

| (167/1024)*800 MHz                    | 38                      |

| Two tone:                             |                         |

| (179/1024)*800 MHz, (181/1024)*800MHz | 40                      |

| (277/1024)*800 MHz, (281/1024)*800MHz | 39                      |

| (397/1024)*800 MHz, (401/1024)*800MHz | 36                      |

# **Basis for Linearity Specification**

- Combine Linearity and Timing Jitter Requirements into Specification for Signal to Noise Plus Distortion

- Allows transmitter implementation losses to be optimally allocated by PHY manufacturers

- Test equipment limitations make accurate clock jitter measurements difficult at 10GBASE-T baud rates and jitter levels

- Jitter measured on test clocks can be very different (better or worse) from jitter on MDI output due to buffering and test point accessibility

# **Basis for Linearity Specification**

- Signal to Noise plus Distortion Ratio Required for Interoperability is > 37 dB

- Corresponds to < 0.3 dB link implementation loss on long lines</li>

- Distortion and Noise is Frequency Dependent

- Sufficient Requirement for Signal to Noise Plus Distortion is

SNDR

$$(f_{\text{MHz}}) = \begin{cases} 40 \text{ dB}, & f_{\text{MHz}} \le 200 \\ 58 - 20 \cdot \log_{10} (f_{\text{MHz}}/25) \text{ dB}, & 200 < f_{\text{MHz}} \le 500 \end{cases}$$

# **Basis for Linearity Specification**

- Signal to Noise plus Distortion Ratio Specification Based on Sinusoidal Test Signals

- Sinusoidal measurements provide an accurate estimate of distortion for Tomlinson-Harishima Precoded DSQ signals

- Sinusoidal measurements can be made in the frequency domain or time domain using basic lab equipment

- signal averaging is not needed to achieve necessary accuracy, allowing reliable noise measurements

- Sinusoidal measurements do not require special test access or complicated waveform acquisition and processing procedures

#### **PSD and Power Specification**

Required Specification

#### 55.5.6 Transmitter power spectral density (PSD) and power

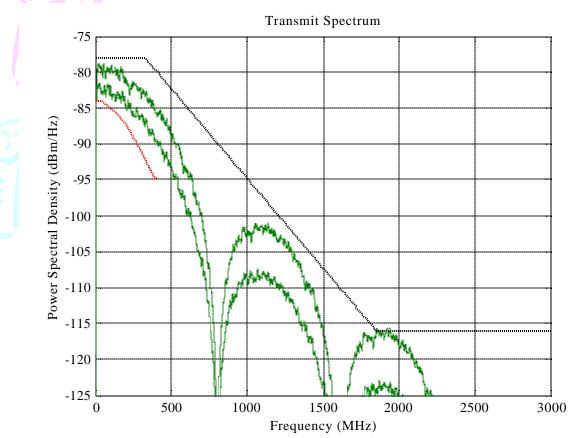

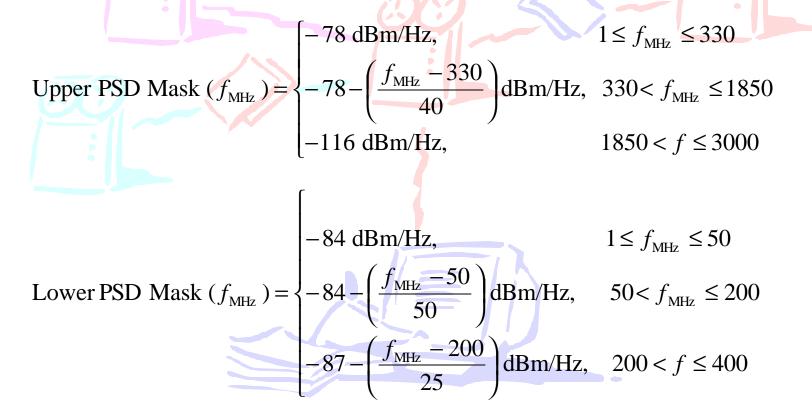

In test mode 5 (normal operation with no power back-off), the transmit power shall be in the range 4.0 dBm to 6.0 dBm and the power spectral density of the transmitter, measured into a  $100\Omega$  differential resistive load, shall be below the upper mask and above the lower mask specified in Figure 55-26, which corresponds to:

#### **PSD and Power Specification**

#### Required Specification (cont.)

### **Basis for PSD and Power Specification**

- Upper Mask Provides EMI-Based Bound for TH Precoded DSQ Signals (see pagnanelli\_2\_1104)

- Specified noise floor ensures > 37 dB transmit SNR

- Lower Mask Ensures Output Spectrum is Compatible with Expected Equalizer Capabilities

- PSD Masks Accommodate Reasonable Filter Design Variation and Manufacturing Tolerance

- Output Power Range of 4 dBm to 6 dBm Ensures > 37 dB SNR on 100m Cat6e in the Presence of 1000BASE-T ANEXT and –150 dBm/Hz Background Noise.

#### **Transmitter Clock Frequency**

Required Specification

#### 55.5.7 Transmitter clock frequency

The symbol transmission rate on each pair of the Master PHY shall be 800 Mbaud  $\pm$  50 ppm.

- Frequency References with <u>+</u> 50 ppm Tolerance are Readily Available

- Tighter Tolerance Eases Tracking Requirements of Low-Jitter Loop Timing Recovery Circuits

#### Conclusion

- Specific Transmitter Electrical Specifications have been Established Based on Interoperability Requirements

- Specifications are Tied to Objective Measurements that can be Made Accurately with Basic Lab Test Equipment and Simple Procedures