#### Vport ad hoc update part 2 March 2007

### Fred Schindler **Cisco Systems**

**Andrew Smith Anoop Vetteth** Bill Delveaux Brian Buckmeir Chad Jones Christen Beia Clav Stanford **Dan Dove** Daniel Feldman David Law **David Lucia** Derick Koonce Ferdinando Lari Frank Yung Fred Schindler **Geoff Thompson** Helen Kastner **Hugh Barrass**

**Power Integration Cisco Systems** Cisco Systems Bel Cisco Systems ST Microelectronics Linear Technology **HP Procurve Networking** Microsemi 3COM **SIFOS** Independent ST Microelectronics SystemX Cisco Systems **Nortel Networks** Cisco Systems Cisco Systems

John Jetzt Keith Hopwood Ken Bennett **Martin Patoka Matthew Landry** Pavlick Rimboim Ramesh Sastry Raul Lozano Riccardo Russo Saiol Ghoshal Taufique Ahmed **Thong Nguyen** Thuyen Dinh **Tim Parker** Wael Diab Yair Darshan Youhoa Xi

Jean Picard Texas Instruments Avaya Phihong **SIFOS Texas Instruments** Silicon Labs Michael Altmann **Akros Silicon** Microsemi Cisco Systems Pulse **ST Microelectronics** Akros Silicon Akros Silicon Maxim Pulse **Nortel Networks** Broadcom Microsemi **National Semiconductor**

Four ad hocs with an average attendance of 12 people since the last IEEE meeting. People that attended since the last IEEE meeting are shown in **bold**.

# System Considerations

IEEE parameters are valid only at the points where they are tested for compliance.

A PSE dv/dt rate of 3.5V/ $\mu$ s is valid when test at a load rate of 35 mA/ $\mu$ s.

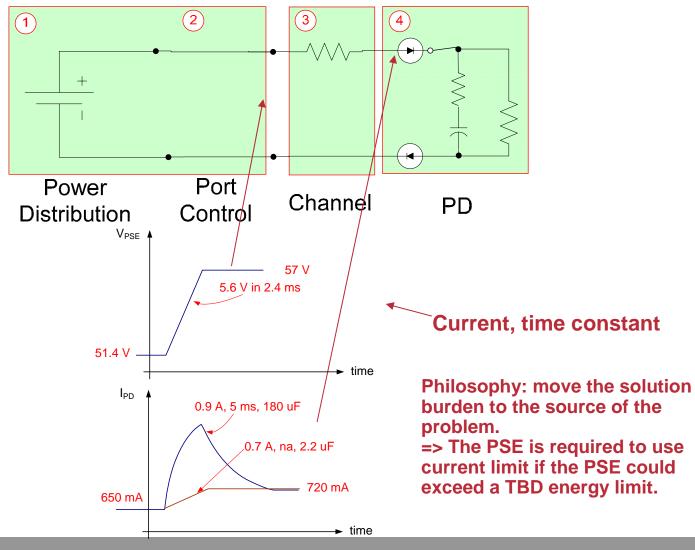

Philosophy: move the solution burden to the source of the problem.

# System Concerns being addressed by I<sub>LIM</sub>

Situations that lead to a PSE dv/dt rate that causes excess PD current demand.

Multiple PDs reducing their load.

A PSE switching in a new power supply to deal with a power supply failure.

Assuming a PSE transitions from the minimum supply voltage to the maximum supply voltage at the dv/dt test point of 3.5V/µs.

Philosophy: move the solution burden to the source of the problem.

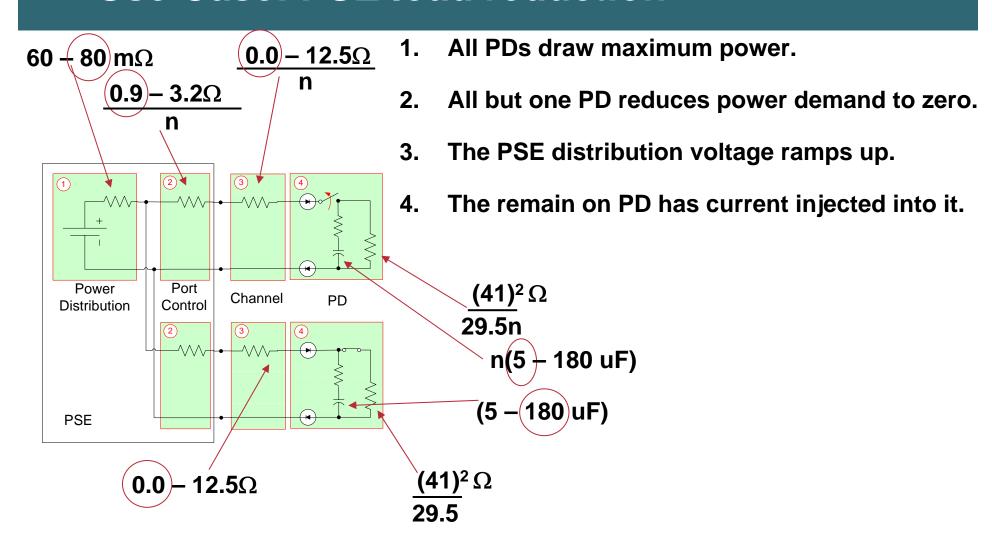

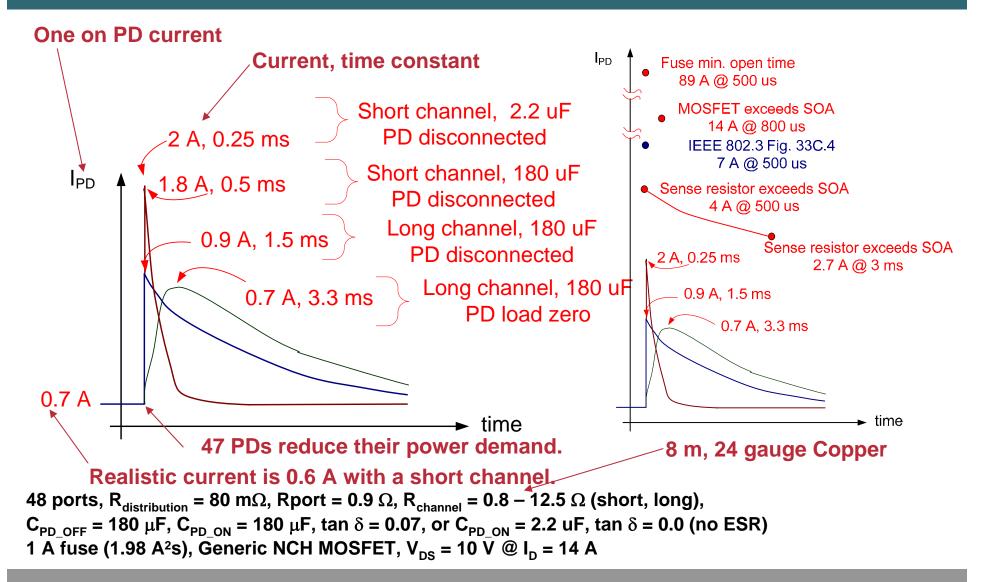

#### **Use Case: PSE load reduction**

A PSE providing 50 V at 720 mA results in a PD voltage of 41 V (29.5 W).

#### **Use Case: PSE load reduction**

### **Use Case: PSE power supply backup**

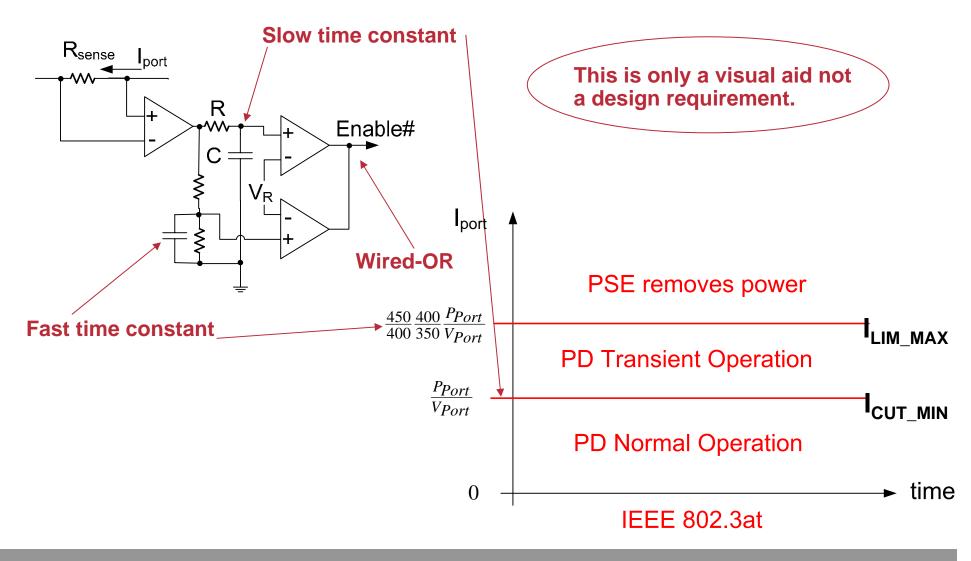

### **Proposed PSE current monitor**

# How to specify?

- Goal: Create a energy transfer compliance test that ensures system interoperability and permits a current limit design or an energy based design.

- Current limiting designs require more time to charge PDs than energy limited designs.

- Energy limit designs allow higher current for a shorter period of time than current limiting designs.

- Both transfer the same amount of energy to the PD capacitor but have different channel losses.

#### **PSE Limiting the Current**

Due to PSE supply change

$$Max\_Energy = \frac{1}{2}C_{PD}(V_f^2 - V_i^2)$$

$$= V_{PSE\_MIN} \times (I_{LIM\_MIN} - I_{CUT\_MIN}) \times T_{LIM\_MIN}$$

Current available for charging the PD capacitor.

$$\frac{1}{2}180\mu(57^2-50^2)$$

$$=50\times(0.820-0.720)\times T_{LIM}$$

MIN

These two parameters are under the control of the PSE.

$$T_{LIM\ MIN} = 13.5 \text{ ms}$$

#### **PSE Energy Limit**

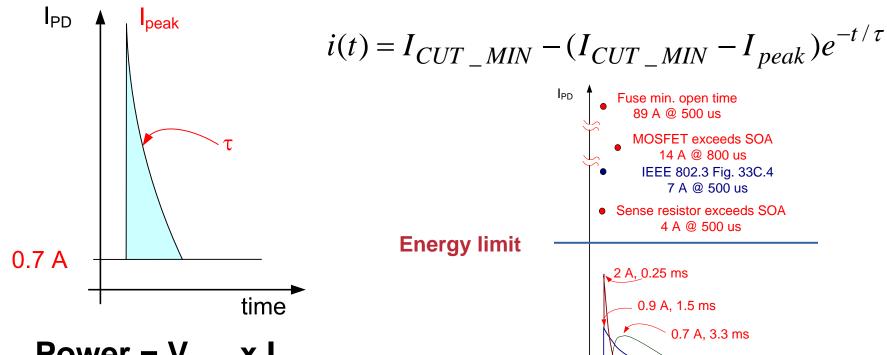

Power = V<sub>PSE</sub> x I<sub>port</sub> Energy = Power x time

$$AREA = \int_{0}^{4\tau} i(t)dt = I_{peak}\tau e^{-t/\tau} \mid_{0}^{4\tau}$$

time

#### **Next Step**

- Review and expand details on the proposed energy based limit.

- Create a simple method to test for compliance.

- Update the task force on progress made.