#### 40/100G Architecture and Interfaces proposal

Ilango Ganga, Intel Brad Booth, AMCC Howard Frazier, Broadcom Shimon Muller, Sun Gary Nicholl, Cisco

March 18, 2008

03/18/2008

## **Supporters**

- Andre Szczepanek

- Arthur Marris

- Subi Krishnamurthy

Texas Instruments Cadence Force 10 Networks

## Overview

- Proposed layer diagrams for 40Gb/s and 100Gb/s

- Additional references: ganga\_01\_1107, ganga\_01\_0108

- Proposed architectures

- See frazier\_01\_0308.pdf for interface definitions

- Possible implementation examples

- Summary

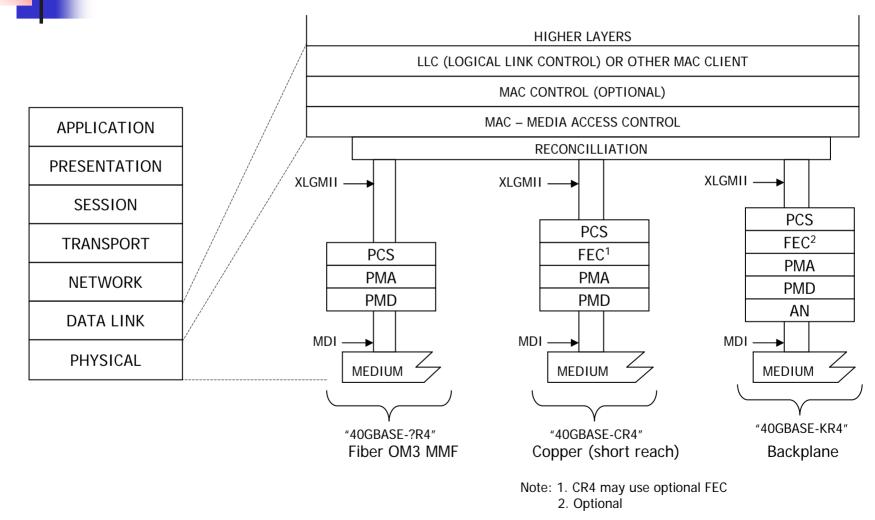

## Proposed 40GbE layer model

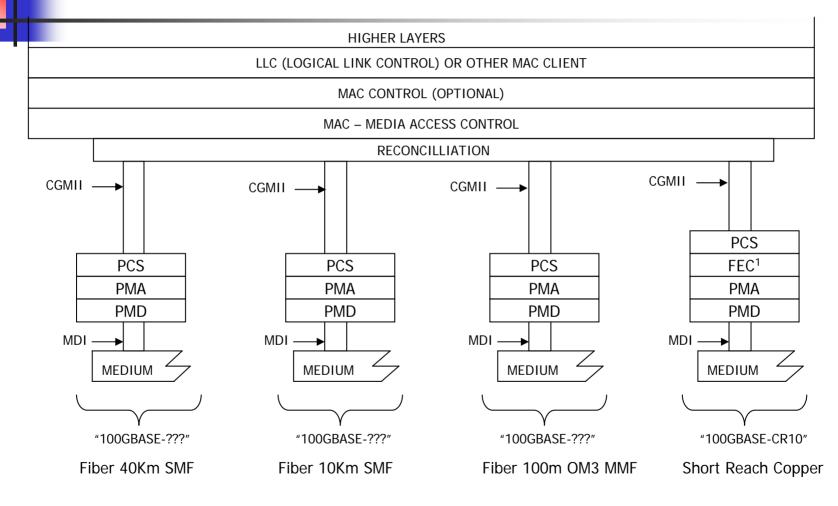

#### Proposed 100GbE layer model

Note: 1. CR10 may use optional FEC

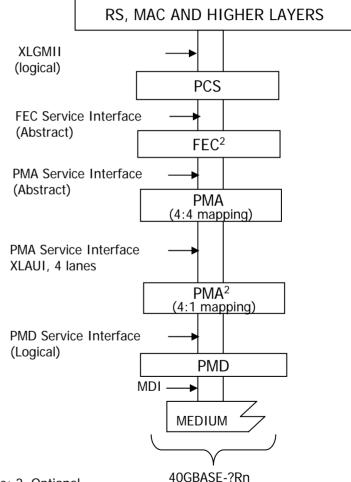

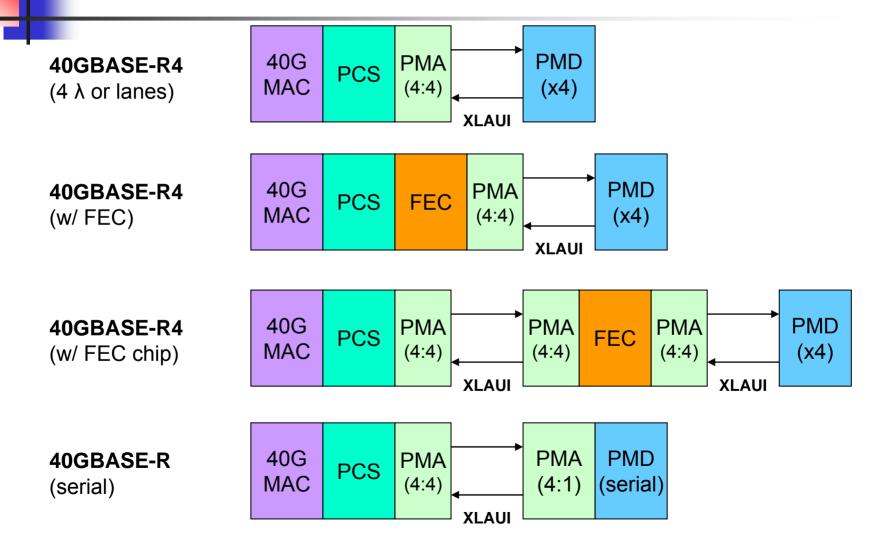

#### Proposed 40GbE architecture

- XLGMII (intra-chip)

- Logical, define data/control, clock, no electrical specification

- PCS

- 64B/66B encoding

- Lane distribution and alignment

- XLAUI (chip-to-chip)

- n lane x 10 GBaud electrical interface

- 4 lanes, short reach

- FEC service interface

- Abstract, can map to XLAUI electrical interface

- PMA Service interface

- Logical n lanes, maps to XLAUI electrical interface

- PMD Service interface

- Logical, can map to XLAUI electrical interface

Note: 2. Optional

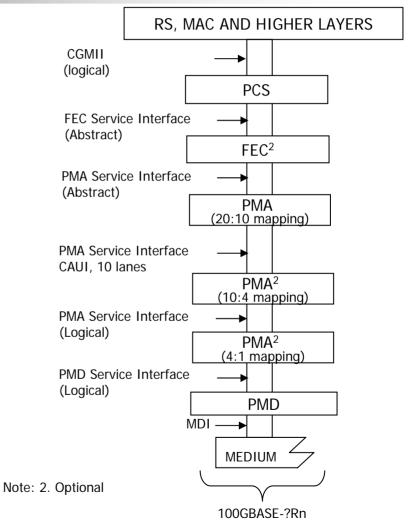

#### Proposed 100GbE architecture

- CGMII (intra-chip)

- Logical, define data/control, clock, no electrical specification

- PCS

- 64B/66B encoding

- Lane distribution and alignment

- CAUI (chip-to-chip)

- n lane x 10Gbaud electrical interface

- 10 lanes, short reach

- FEC service interface

- Abstract, can map to CAUI electrical interface

- PMA Service interface

- Logical n lanes, maps to CAUI electrical interface

- PMD Service interface

- Logical, can map to CAUI electrical interface

03/18/2008

# Interface description (1)

- XLGMII (Forty Gigabit MII) or CGMII (100 Gigabit MII) PCS interface

- Interface between MAC and PHY layers needed for intra-chip connectivity

- Need for Compatibility interface

- Multiple vendors develop IP blocks for system on chip implementations

- Provides a point of interoperability for multi vendor implementations

- Logical definition, data width, control, clock frequency, no electrical specification

- XLGMII and CGMII can have same logical behavior, different data/control width and/or clock frequency

- XLAUI or CAUI interface (Chip-to-Chip)

- n lane x 10Gbaud electrical interface

- Provides a point of interoperability for multi vendor implementations

- Similar to XAUI, for 10GbE, which is widely used as MAC PHY interface

- Low pin count, low power interface, for example PHYs, Switches, LAN controllers

- Electrical definition, n lane x 10 Gbaud differential signaling

- Short reach channel: e.g. around 10 inches with 1 pair of connector

- Lane width: 4 lane for 40G, and 10 lane for 100G;

- Same electrical definition can be optionally used with multiple Service interfaces (e.g. PMA, FEC, PMD)

# Interface description (2)

- FEC Service interface

- Interface between PCS and optional FEC sub-layer

- Used for backplane PHYs, may be used with other PHY types (e.g. copper cable assy)

- FEC Service interface is similar to PMA interface

- Possible implementations: FEC integrated with MAC/PCS, or with PMA/PMD device

- Abstract definition, with an option to map to XLAUI/CAUI electrical interface

- PMA Service interface

- Interface between PMA and PCS

- Logical definition with n Lanes, maps to XLAUI/CAUI electrical interface

- PMD Service interface

- Interface between PMD and PMA

- PMA and PMD may be implemented together in the same device

- Logical definition, with an option to map to XLAUI/CAUI electrical interface

#### Possible 40GbE implementations

03/18/2008

#### Possible 100GbE implementations 100G **PMD** 100GBASE-R10 **PMA** PCS (20:10)MAC (x10) (10 $\lambda$ or lanes) CAUI 100G 100GBASE-R10 **PMD PMA PMA PMA** PCS FEC<sup>1</sup> MAC (20:10)(10:20)(20:10)(x10)(w/ FEC chip) CAUI CAUI 100G **PMD 100GBASE-R4 PMA PMA** PCS MAC (20:10)(10:4)(4 $\lambda$ or lanes) (x4) CAUI 100G **PMA PMA PMA PMD** 100GBASE-R PCS MAC (20:10)(10:4)(4:1)(serial) (serial) CAUI

Note: 1. CR10 may use optional FEC

# Summary

Proposed 40/100G high level architecture

- Provides a common framework for both 40G and 100G

- Supports project objectives

- Provide an interface for multi-vendor interoperability

- XLGMII/CGMII for intra-chip connectivity

- XLAUI/CAUI for inter-chip connectivity