# 40GbE MTTFPA when using transcoding

#### Steve Trowbridge, Alcatel-Lucent Osamu Ishida, NTT

IEEE P802.3ba Task Force Orlando, FL March 2008

40GbE MTTFPA when using transcoding

For IEEE802.3ba, Mar. 2008

#### Purpose of This Presentation

- Potential issue with appropriate support for OTN

- 512b/513b transcoding could degrade MTTFPA

- to the order of BER^1 (< lifetime of the universe)

- far below the order of BER^3 in native 64b/66b

- Proposed improvements for MTTFPA

- Alternative transcodings increase MTTFPA

- to the order of BER^2 (> lifetime of the universe)

- ITU-T experts will meet in June to consider proposals

- IEEE input welcome

- Identify minimal MTTFPA related OTN support requirements to IEEE802.3ba

#### Potential "OTN compatibility" Issue

- Native 64b/66b provides excellent MTTFPA

- of the order of BER^3

- more than the age of the universe

- While transcoding is normally used into an FEC protected environment of OTN, MTTFPA could be degraded given uncorrected or miscorrected errors in OTN

- to the order of BER^1 when using 512b/513b

- less than the age of the universe

#### Remedy for MTTFPA

- During ITU-T Q11/SG15 February meeting, alternative transcoding proposals appear that improve MTTFPA

- to the order of BER^2

- bellow performance of native 64b/66b slightly, but

- well more than the age of the universe (See next slide)

- Alternative transcoding proposals (See Appendix)

- 512b/514b (Remedy 1) and 1024b/1027b (Remedy 2)

- NTT, "40 GbE MTTFPA when using 512B/513B transcoding ", C786, ITU-T Q11/15, Feb 2008, Geneva

- 1024b/1026b (Remedy 3)

- Alcatel Lucent, "Mapping of 40 GbE into OTN and MTTFPA", C892, ITU-T Q11/15, Feb 2008, Geneva

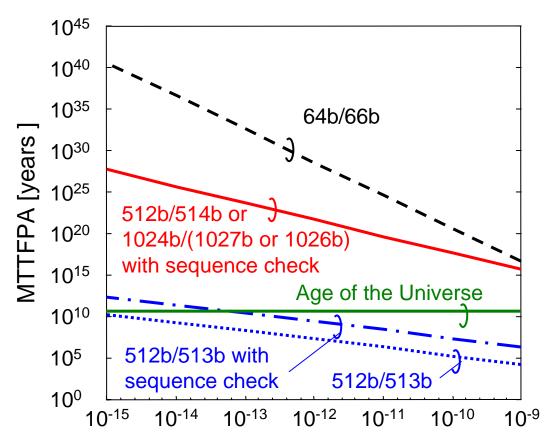

#### **Estimated MTTFPA**

Bit Error Rate (after the error correction if used)

NTT, "40 GbE MTTFPA when using 512B/513B transcoding ", C786, ITU-T Q11/15, Feb 2008, Geneva

Alcatel · Lucent

## ITU-T Will Discuss Pros and Cons in June

| Transcoding                       | 512B/513B                              | 512B/514B                                                                                                                                               | 1024B/1027B                      | 1024B/1026B                          |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------|--|--|--|--|--|--|

| Proposal<br>in ITU-T Q11/SG15     | Alcatel-Lucent<br>WD12,Q11/15 Oct 2007 | <mark>NTT</mark><br>СОМ 15 – С 786 – Е                                                                                                                  | <b>NTT</b><br>СОМ 15 – С 786 – Е | Alcatel-Lucent<br>COM 15 – C 892 – E |  |  |  |  |  |  |

| Features                          |                                        |                                                                                                                                                         |                                  |                                      |  |  |  |  |  |  |

| MTTFPA at link BER<br>of 10^-12   | NO<br>10^7.4 Years                     | YES<br>10^22 Years                                                                                                                                      | YES<br>10^22 Years               | YES<br>10^22 Years                   |  |  |  |  |  |  |

| Self-synchronization              | NO                                     | YES                                                                                                                                                     | YES                              | YES                                  |  |  |  |  |  |  |

| Coding delay                      | 512 bits                               | 512 bits                                                                                                                                                | 1024 bits                        | 1024 bits                            |  |  |  |  |  |  |

| OTN mapping                       | •                                      |                                                                                                                                                         |                                  |                                      |  |  |  |  |  |  |

| Bit rate for 40GbE                | 40.078 Gb/s                            | 40.156 Gb/s                                                                                                                                             | 40.117 Gb/s                      | 40.078 Gb/s                          |  |  |  |  |  |  |

| 40GbE mapping into<br>OPU3        | YES                                    | YES <sup>*1</sup>                                                                                                                                       | YES                              | YES                                  |  |  |  |  |  |  |

| Full Ethernet symbol transmission | YES                                    | NO                                                                                                                                                      | YES                              | YES                                  |  |  |  |  |  |  |

| Client clock<br>transmission      | YES                                    | YES <sup>*2</sup>                                                                                                                                       | YES                              | YES                                  |  |  |  |  |  |  |

| Comments                          |                                        | <ul> <li>*1: IDLE shrinkage<br/>of 100ppm and<br/>using ODU3 NJO<br/>(1byte)</li> <li>*2: Constant rate<br/>IDLE shrinkage<br/>and insertion</li> </ul> |                                  |                                      |  |  |  |  |  |  |

40GbE MTTFPA when using transcoding

#### MTTFPA OTN support Requirements

- Permit MTTFPA of the order of BER^2

- Below performance of native 64b/66b, but

- still greater than lifetime of universe

- If with 512b/514b (Remedy 1)

- No extension of 64b/66b control code

- Operate at lower end of +/- 100ppm clock tolerance range

- If with 1024b/1027b (Remedy 2)

- No extension of 64b/66b control code

- If with 1024b/1026b (Remedy 3)

- No extension of 64b/66b control code

- Only start packets and ordered sets on 8B boundary

#### Appendix

#### Alternative Transcoding Details

- 512b/513b and Its MTTFPA Issues

- What happens if a bit error hits ....?

- (1) Flag Bit for 512b Payload

- requires 512b/514b (Remedy 1), or

- 1024b/1027b (Remedy 2), or

- 1024b/1026b (Remedy 3)

- (2) 1-Bit Control-Block Continuation Flag

- requires Block Sequence Check

- (3) 3-bit original position of control block

- (not a problem)

- (4) 4-bit representation of 66B control block type

- requires re-mapping the control block type

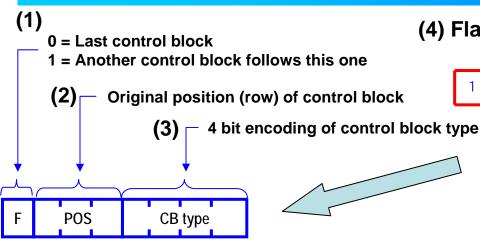

#### 512b/513b and Its MTTFPA Issues

#### Control block header byte

"Proposed mapping of 40 Gb Ethernet into standard ODU3", (Alcatel Lucent) wd12, ITU-T Q11/15, Oct 2007, Shenzhen

| ock) |

|------|

| (    |

|   | <i>(</i>     |                                                   |                                                   |    |    |    |    | · · |  |  |  |  |

|---|--------------|---------------------------------------------------|---------------------------------------------------|----|----|----|----|-----|--|--|--|--|

|   | 1aaa<br>TTTT |                                                   |                                                   |    |    |    |    |     |  |  |  |  |

| ÷ | 1bbb<br>TTTT | 7 byte (per format of 64B/66B control block type) |                                                   |    |    |    |    |     |  |  |  |  |

|   | Occc<br>TTTT |                                                   | 7 byte (per format of 64B/66B control block type) |    |    |    |    |     |  |  |  |  |

|   | D0           | D1                                                | D2                                                | D3 | D4 | D5 | D6 | D7  |  |  |  |  |

|   | D0           | D1                                                | D2                                                | D3 | D4 | D5 | D6 | D7  |  |  |  |  |

|   | D0           | D1                                                | D2                                                | D3 | D4 | D5 | D6 | D7  |  |  |  |  |

|   | D0           | D1                                                | D2                                                | D3 | D4 | D5 | D6 | D7  |  |  |  |  |

|   | D0           | D1                                                | D2                                                | D3 | D4 | D5 | D6 | D7  |  |  |  |  |

#### • What happens if a bit error hits the following bits?

| NTT                                                                     | Alcatel·Lucent 🅢 |

|-------------------------------------------------------------------------|------------------|

| <ul> <li>4-bit representation of 66B control block type (CB)</li> </ul> | (4)              |

| <ul> <li>3-bit original position of control block (POS)</li> </ul>      | (3)              |

| <ul> <li>1-bit continuation flag (F)</li> </ul>                         | (2)              |

| <ul> <li>A control-block header byte</li> </ul>                         |                  |

| <ul> <li>A flag bit for 512b payload</li> </ul>                         | (1)              |

40GbE MTTFPA when using transcoding

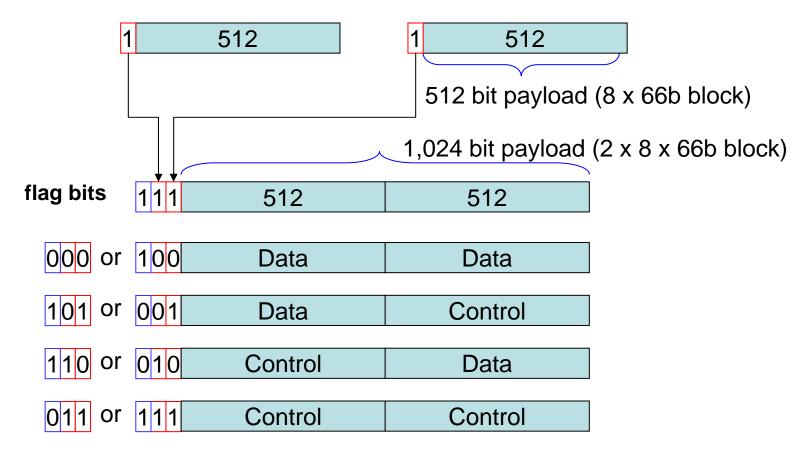

# (1) Flag Bit for 512b Payload

- If a bit error hits this 1-bit header of the 512b block that includes 66B control blocks, all the 66B blocks are misinterpreted as data

- This is sometimes critical, since the minimum inter-frame spacing is far less than 512b, and hence two consecutive MAC frames may be mis-integrated and still pass the CRC check.

- Our recommendations

- Remedy 1: Add one more bit for the flag; i.e. 512b/514b

- Like 64b/66b, two-bit header also provides capabilities for block synchronization and bit-error monitoring

- Remedy 2: Concatenate two 512b/513b blocks and add one more bit for the flag; i.e. 1024b/1027b

- Allow ODU3 mapping without any IDLE shrinkage

- Remedy 3: Increase the transcoding compression to 1024b/1025b per malpass\_03\_0907, then add one more bit for the flag; i.e. 1024b/1026b

🕐 NTT

#### Remedy 1: 512b/514b

- Nominal rate of 512b/514b is slightly higher than that of OPU3 payload area, but can be accommodated within 100ppm clock tolerance margin of Ethernet

- by removing some of inter frame idles

| 40 Gigabit<br>Ethernet   | LAN PMD                                                       | 41.25 Gb/s (4x10.3125 Gb/s) |  |  |  |

|--------------------------|---------------------------------------------------------------|-----------------------------|--|--|--|

| Ethemet                  | Effective rate                                                | 40 Gb/s                     |  |  |  |

| 512B/514B<br>transcoding | Nominal rate                                                  | 40.15625 Gb/s               |  |  |  |

| transcouling             | Removal allowance clock tolerance of -100 ppm                 | 40.15223438 Gb/s            |  |  |  |

| OPU3                     | Nominal payload rate                                          | 40.150519322 Gb/s           |  |  |  |

| payload<br>area          | Maximum payload rate with NJO byte                            | 40.15315525 Gb/s            |  |  |  |

|                          | Maximum payload rate under worst case clock tolerance -20 ppm | 40.15235219 Gb/s            |  |  |  |

#### 40.15235219 Gb/s > 40.15223438 Gb/s

Alcatel·Lucent 🥢

#### Remedy 2: 1024b/1027b

- Concatenate two 512b/513b blocks and add one more flag bit

- Provide two-bit Hamming distance between 3-bit flags

🕐 NTT

40GbE MTTFPA when using transcoding

Alcatel · Lucent

#### Remedy 2: 1024b/1027b on ODU3 ?

• Yes, nominal rate of 1024b/1027b is lower than that of OPU3 payload area!

| 40 Gigabit<br>Ethernet     | LAN PMD                                                         | 41.25 Gb/s (4x10.3125 Gb/s) |  |  |

|----------------------------|-----------------------------------------------------------------|-----------------------------|--|--|

| Ellemel                    | Effective rate                                                  | 40 Gb/s                     |  |  |

| 1024B/1027B<br>transcoding | Nominal rate                                                    | 40.1171875 Gb/s             |  |  |

| transcoung                 | Maximum rate under worst case clock tolerance of + 100 ppm      | 40.12119921875 Gb/s         |  |  |

| OPU3                       | Nominal payload rate                                            | 40.150519322 Gb/s           |  |  |

| payload area               | Minimum payload rate under worst case clock tolerance of -20ppm | 40.14971631161356 Gb/s      |  |  |

40.12119921875 Gb/s < 40.14971631161356 Gb/s

# Remedy 3: Additional compression to allow more robust code to fit standard ODU3

- Huawei proposed generalization of 512B/513B to (64\*N)B/(64\*N+1)B to enable more compact coding (malpass\_03\_0907.pdf)

- More compact code than 512B/513B not needed just to get 40 GbE to fit standard ODU3, and not generally desirable as larger block sizes for transcoding increase latency

- "One notch" more compact coding to apply MTTFPA improvements and still fit standard ODU3.

- o Doubling of Flag bit to two bits (01 or 10) improves MTTFPA and provides additional benefit that it is "self framing"

- o Use 1024B/1026B code (sixteen 66B input blocks per 1026B block), which has same efficiency as 512B/513B

- o Four bit position indicator (instead of 3) for control block position

- Use variable length control block type, taking advantage of unused bits in certain control block formats and 66B control block types not needed given 8-byte packet start and ordered set position rules with 2-bit Hamming distance between control block types with packet terminate /T/

- Since 1024B/1026B is the same ratio as 512B/513B, it fits ODU3

#### Possible control block reductions for 40/100 GbE From MLD proposal

| Ordered sets can't start in 5 <sup>th</sup> lane | Input Data                                                                                                               | S<br>y<br>n<br>c | Block I             | Payload        |                |                |                |                |                |                |                |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                                                  | Bit Position:<br>Data Block Format:                                                                                      | 01               | 2                   |                |                |                |                |                |                |                | 65             |

|                                                  | D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 01               | D <sub>0</sub>      | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D              | 4              | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|                                                  | Control Block Formats:                                                                                                   |                  | Block Type<br>Field |                | l              | 1              |                |                | 1              | 1              |                |

|                                                  | C <sub>0</sub> C <sub>1</sub> C <sub>2</sub> C <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x1e                | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | $C_4$          | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| \ <b>\</b> _                                     |                                                                                                                          | 10               | 0v2d                | C <sub>0</sub> | C;             | C <sub>2</sub> | C <sub>0</sub> | 0;             | D <sub>0</sub> | D <sub>0</sub> | . D,           |

|                                                  |                                                                                                                          | 10               | 0×22                | C <sub>0</sub> | C,             | C_             | C,             |                | D,             | P,             | D,             |

| X                                                | O <sub>2</sub> D <sub>1</sub> D <sub>2</sub> D <sub>2</sub> /S <sub>1</sub> D <sub>2</sub> D <sub>2</sub> D <sub>2</sub> | 10               | 0x66                | D4             |                | D              | 0,             |                | De             | De             | D-             |

|                                                  | 0- D- D- D-/0- D- D- D-                                                                                                  | 10               | 0×55                | D,             | D              | D              | 0-             | 0.             | De             | De             | D-             |

|                                                  | S <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 10               | 0x78                | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D              | 4              | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |

|                                                  | O <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x4b                | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | O <sub>0</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | ${\rm T}_0{\rm C}_1{\rm C}_2{\rm C}_3/{\rm C}_4{\rm C}_5{\rm C}_6{\rm C}_7$                                              | 10               | 0x87                |                | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | D <sub>0</sub> T <sub>1</sub> C <sub>2</sub> C <sub>3</sub> /C <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | 0x99                | D <sub>0</sub> |                | C <sub>2</sub> | C <sub>3</sub> | $C_4$          | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | $D_0 D_1 T_2 C_3 / C_4 C_5 C_6 C_7$                                                                                      | 10               | 0xaa                | D <sub>0</sub> | D <sub>1</sub> |                | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| Packets can't                                    | $D_0 D_1 D_2 T_3 / C_4 C_5 C_6 C_7$                                                                                      | 10               | 0xb4                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> |                | C <sub>4</sub> | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

| start in 5 <sup>th</sup> Iane                    | D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /T <sub>4</sub> C <sub>5</sub> C <sub>6</sub> C <sub>7</sub> | 10               | Охсс                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D              | 3              | C <sub>5</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | $D_0D_1D_2D_3/D_4T_5C_6C_7$                                                                                              | 10               | 0xd2                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D              | 3              | D <sub>4</sub> | C <sub>6</sub> | C <sub>7</sub> |

|                                                  | $D_0 D_1 D_2 D_3 / D_4 D_5 T_6 C_7$                                                                                      | 10               | 0xe1                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D              | 3              | D <sub>4</sub> | D <sub>5</sub> | C <sub>7</sub> |

|                                                  | D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> /D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> T <sub>7</sub> | 10               | 0xff                | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D              | 3              | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> |

Figure 49–7–64B/66B block formats

40GbE MTTFPA when using transcoding

For IEEE802.3ba, Mar. 2008

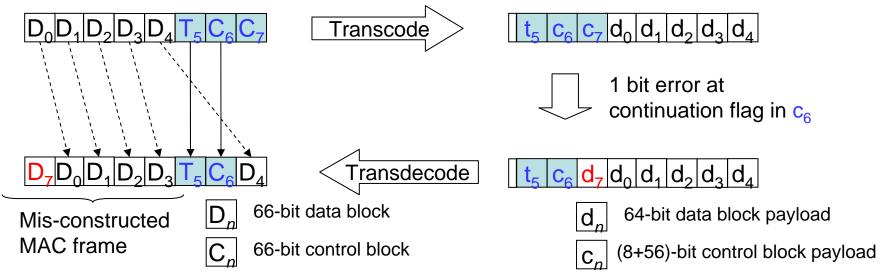

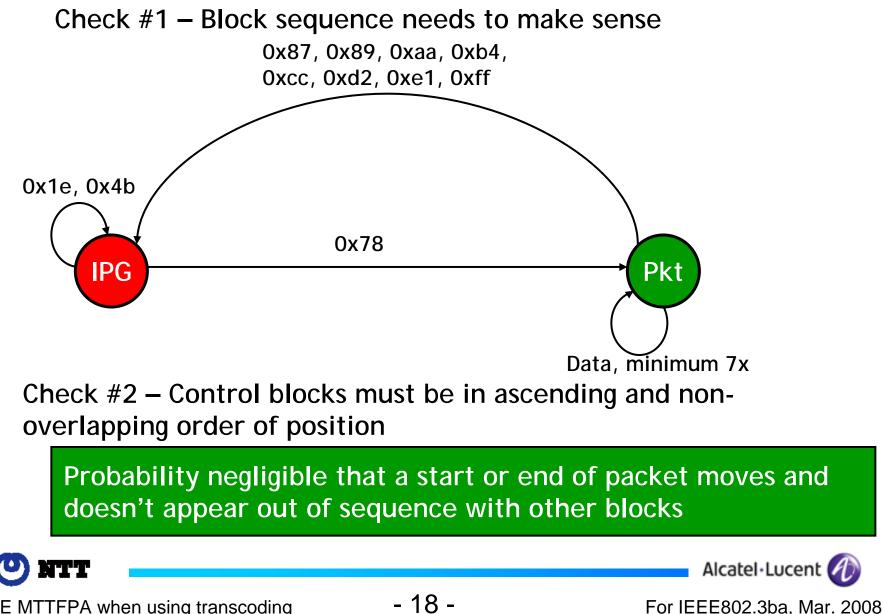

# (2) 1-Bit Control-Block Continuation Flag

- If a bit error hits this flag, the following 66B control blocks are all misinterpreted as data blocks

- This is critical, since some of 66B control blocks may be misinterpreted as data, and a MAC frame may be mis-constructed and still pass the CRC check.

- Our recommendation

- Check 66B block sequence at the decoder

- Replace the 512-bit payload with eight 66B Error Control Blocks if the sequence violation is detected

🙂 NTT

# **Block Sequence Check**

40GbE MTTFPA when using transcoding

## (3) 3-bit Original Position of Control Block

- If a bit error hits these bits, the 66B control block is misplaced in the 512-bit payload, yielding misplaced 66B data blocks

- This is not critical, since such wrong 66B block sequence will be detected at 64/ 66 PCS

- Not a Problem

40GbE MTTFPA when using transcoding

Alcatel · Lucent

# (4) 4-bit representation of control block type

- If a bit error hits these bits, the 66B control block is misinterpreted

- This is critical, especially if the frame delimiter block T or S is misinterpreted, MAC frame may be stretched or shrunk by several bytes and still pass the CRC check

- 64B/66B avoids this issue by selecting type codes with Hamming distance of 4

- 512b/513b can not fully utilize this since we steal 4-bit from this type field, but ....

#### Our recommendation

- Re-map the 4-bit control block (CB) type to keep the Hamming distance of 2 among CB-types for T and S

- Rearrangement of code values for flag bit Solution 1 or 2

- Take advantage of reduced set of control block types for 40 GbE and 100 GbE for flag bit solution 3 Alcatel · Lucent

#### Control Block (CB) Type Update Example Flag bit for Remedy 1 or 2

|    | 64b/66b Block                                                                                                             |            | СВ Туре | Cf. original 512b/513b |            |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------|------------|---------|------------------------|------------|--|--|

| #  | Control Block Formats                                                                                                     | Type Field | свтуре  | (Table                 | 1 of [4] ) |  |  |

| 1  | $C_0 C_1 C_2 C_3 / C_4 C_5 C_6 C_7$                                                                                       | 0x1e       | 0001    | 1                      | 0001       |  |  |

| 2  | $C_0 C_1 C_2 C_3 / O_4 D_5 D_6 D_7$                                                                                       | 0x2d       | 0010    | 1                      | 0010       |  |  |

| 3  | $C_0 C_1 C_2 C_3 / S_4 D_5 D_6 D_7$                                                                                       | 0x33       | 0111    | Hamming                | 0011       |  |  |

| 4  | $O_0 D_1 D_2 D_3 / S_4 D_5 D_6 D_7$                                                                                       | 0x66       | 1011    | distance               | 0100       |  |  |

| 5  | O <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> / O <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | 0x55       | 1101    | greater                | 0101       |  |  |

| 6  | $S_0 D_1 D_2 D_3 / D_4 D_5 D_6 D_7$                                                                                       | 0x78       | 1110    | f than two             | 0110       |  |  |

| 7  | $O_0 D_1 D_2 D_3 / C_4 C_5 C_6 C_7$                                                                                       | 0x4b       | 1000    | ]                      | 0111       |  |  |

| 8  | $T_0 C_1 C_2 C_3 / C_4 C_5 C_6 C_7$                                                                                       | 0x87       | 0011    |                        | 1000       |  |  |

| 9  | $D_0 T_1 C_2 C_3 / C_4 C_5 C_6 C_7$                                                                                       | 0x99       | 0101    |                        | 1001       |  |  |

| 10 | $D_0 D_1 T_2 C_3 / C_4 C_5 C_6 C_7$                                                                                       | 0xaa       | 1001    | Hamming                | 1010       |  |  |

| 11 | $D_0 D_1 D_2 T_3 / C_4 C_5 C_6 C_7$                                                                                       | 0xb4       | 1010    | distance               | 1011       |  |  |

| 12 | $D_0 D_1 D_2 D_3 / T_4 C_5 C_6 C_7$                                                                                       | Охсс       | 1100    | ( greater              | 1100       |  |  |

| 13 | $D_0 D_1 D_2 D_3 / D_4 T_5 C_6 C_7$                                                                                       | 0xd2       | 0110    | than two               | 1101       |  |  |

| 14 | $D_0 D_1 D_2 D_3 / D_4 D_5 T_6 C_7$                                                                                       | 0xe1       | 0000    | 1                      | 1110       |  |  |

| 15 | $D_0 D_1 D_2 D_3 / D_4 D_5 D_6 T_7$                                                                                       | Oxff       | 1111    | ] )                    | 1111       |  |  |

40GbE MTTFPA when using transcoding

# 2-bit Hamming distance for control block types with additional compression (flag bit for Remedy 3)

- Flag = 01 no 66B control blocks in 1026-bit block

- Flag = 10 One or more 66B control blocks in 1026-bit block

- Flag bits plus sixteen transcoded 66B codewords combined (as below) to form each 1026bit block

- All 66B control blocks are sorted to front of 1026-bit block with f indicating if there are more control blocks, 4-bit POS indicating original position (row) of this control block

- Minimum 2-bit Hamming distance between coding for block types with terminate /T/ in different positions

| Input Data         | BI | lock Pay       | load |       |    |    |    |    |    |    |            |       |    |  |    |   |    |    |    |

|--------------------|----|----------------|------|-------|----|----|----|----|----|----|------------|-------|----|--|----|---|----|----|----|

| Bit Position:      | 0  |                |      |       |    |    |    |    |    |    |            |       |    |  |    |   |    |    | 63 |

| Data Block Format: |    |                |      |       |    |    |    |    |    |    |            |       |    |  |    |   |    |    |    |

| D0D1D2D3/D4D5D6D7  |    | D0             |      |       | 1  |    | D  | 2  |    | D3 |            | [     | D4 |  | D5 |   | D6 | D7 |    |

|                    |    | ock Typ<br>eld | Гуре |       |    |    |    |    |    |    |            |       |    |  |    |   |    |    |    |

| C0C1C2C3/C4C5C6C7  | f  | pos            | 001  | C     | )  |    | C1 |    | C2 |    | Ca         | 3     | C4 |  | C5 |   | C6 | C  | 7  |

| S0D1D2D3/D4D5D6D7  | f  | pos            | 010  | 0     | 1  |    | D  | 2  |    | D3 |            | [     | D4 |  | D5 |   | D6 | D7 |    |

| O0D1D2D3/C4C5C6C7  | f  | pos            | 100  | 0     | 1  |    | D  | 2  |    | D3 |            | O0 C4 |    |  | C5 |   | C6 | C  | 7  |

| T0C1C2C3/C4C5C6C7  | f  | pos            | 110  | 0101  |    |    | C1 |    | C2 | C2 |            | C3 C4 |    |  | C5 |   | C6 | C  | 7  |

| D0T1C2C3/C4C5C6C7  | f  | pos            | 110  | 00110 |    | D0 |    |    | C2 | C2 |            | C3 C4 |    |  | C5 |   | C6 | C  | 7  |

| D0D1T2C3/C4C5C6C7  | f  | pos            | 110  | 01001 |    | D0 |    |    | D1 |    | Ca         | 3     | C4 |  | C5 |   | C6 | C  | 7  |

| D0D1D2T3/C4C5C6C7  | f  | pos            | 110  | 01010 |    | D0 |    |    | D1 |    | D2         |       | C4 |  | C5 |   | C6 | C  | 7  |

| D0D1D2D3/T4C5C6C7  | f  | pos            | 1010 | 01    | D0 |    |    | D1 |    | 1  | <b>D</b> 2 |       | D3 |  | C5 |   | C6 | C  | 7  |

| D0D1D2D3/D4T5C6C7  | f  | pos            | 101  | 10    | D0 |    | D1 |    |    | [  | <b>)</b> 2 |       | D3 |  | D4 |   | C6 | C  | 7  |

| D0D1D2D3/D4D5T6C7  | f  | pos            | 000  | L C   | 0  |    | D1 |    |    | D2 | D2 [       |       | D3 |  | D4 | - | D5 | C  | 7  |

| D0D1D2D3/D4D5D6T7  | f  | pos            | 011  |       | 0  |    | D  | 1  |    | D2 |            |       | D3 |  | D4 |   | D5 | D6 |    |

#### Minimum Hamming distance 2

Alcatel·Lucent 🅢

40GbE MTTFPA when using transcoding

#### **Probability of False Frame Generation**

| Coding<br>Location of<br>Bit error             | Original<br>512b/513b       | 512b/514b<br>1024b/1027b<br>1024b/1026b     | Improved by           |

|------------------------------------------------|-----------------------------|---------------------------------------------|-----------------------|

| Flag for 512b payload                          | 1 x 10 <sup>-15</sup> x BER | 1 x 10 <sup>-17</sup> x BER <sup>2</sup>    | One more header bit   |

| Control block<br>continuation flag (F)         | 8 x 10 <sup>-15</sup> x BER | None                                        | Sequence<br>check     |

| Original position of control block (POS)       | Negligible                  | (9 x 10 <sup>-20</sup> x BER <sup>3</sup> ) | (Sequence<br>check)   |

| 4 bit encoding of control block type (CB type) | 2 x 10 <sup>-14</sup> x BER | 2 x 10 <sup>-16</sup> x BER <sup>2</sup>    | Re-mapping<br>CB type |

40GbE MTTFPA when using transcoding

## Summary of Appendix

- MTTFPA estimation has revealed that 512b/513b has issues against a bit error that hits

- A flag bit for 512b payload

- A control block header byte

- 1 bit continuation flag (F)

- 4 bit representation of 66B control block type (CB)

- MTTFPA can be improved by the following updates

- Increase header bits

- Add one more header bit, i.e. 512b/514b, or

- Concatenate two 512b/513b blocks and add one more header bit, i.e. 1024b/1027b

- Use additional compression and add one header bit; i.e. 1024b/1026b

- Check 66B block sequence at the decoder

- Re-map 4-bit representation of the control block type

- Potential "OTN compatibility" issue

- MTTFPA can be improved to order of BER^2 at if transcoding is used in an error prone environment

- Below performance of native 64b/66b, but still greater than lifetime of universe