## Performance Evaluation of Transcoding and FEC Schemes for 100 Gb/s Backplane and Copper Cable

IEEE 802.3bj Task Force

Atlanta, November 8 - 10, 2011

Roy Cideciyan - IBM

#### **Outline**

- Error models at RS decoder input

- Define coding gain

- Compute coding gain

- Compare error-rate performance for selected schemes

- Post-decoding bit error rate vs. pre-decoding bit error rate

- Post-decoding bit error rate vs. signal-to-noise ratio

- Error flooring

**IBM**

# М

#### Independent Bit Error Model

$$(e = 0, 1 - p_b)$$

(e = 1,  $p_b$ )

- Very simple one-state bit error model for additive white Gaussian noise (AWGN)

- Each state transition labeled by a pair: (error value, state transition probability)

- Binary bit error values e, i.e., either e = 0 (no error) or e = 1 (error)

- Independent bit errors at Reed-Solomon (RS) decoder input

- Error model determined by only one parameter

p<sub>b</sub> = bit error probability at RS decoder input

Bit error probability p<sub>b</sub> for antipodal binary signals as a function of signal-to-noise ratio (SNR)

$$p_b = Q(\sqrt{\text{SNR}})$$

where  $Q(x) = \int_x^\infty \frac{1}{\sqrt{2\pi}} e^{-y^2/2} dy$  and

SNR =

$$d^2_{min}/(4 \sigma^2)$$

,

d<sub>min</sub> = distance between two signal levels

$\sigma$  = noise standard deviation

#### Independent Symbol Error Model

(correct symbol,  $1 - p_{sym}$ )

(erroneous symbol, p<sub>sym</sub>)

- Very simple one-state symbol error model

- m-bit symbols at decision-feedback equalizer output

- There are 2<sup>m</sup>-1 possible symbol errors

- Independent symbol errors at RS decoder input

- In this work, symbol errors (not bit errors) at RS decoder input are assumed to be independent in order to compute random coding gain

- Error model determined by only one parameter

p<sub>svm</sub> = symbol error probability at RS decoder input

Symbol errors at DFE output are modeled as independent errors to compute random coding gain

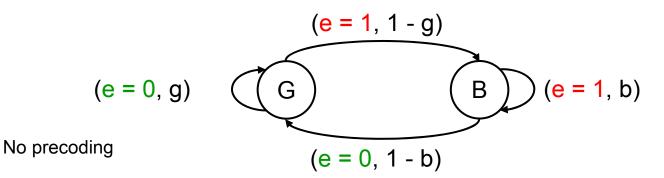

# Gilbert Burst Error Model

- A simple two-state Gilbert burst error model [1] accounting for DFE error propagation

- Each state transition labeled by a pair: (error value, state transition probability)

- Binary bit error values e, i.e., either e = 0 (no error) or e = 1 (error)

- Correlated bit errors at RS decoder input accounting for DFE error propagation

- Error model determined by two parameters

p<sub>b</sub> = bit error probability at RS decoder input

b = probability of staying in bad state B (b = 0.5 assumed in this work)

[1] E. N. Gilbert (1960), "Capacity of a burst-noise channel", Bell System Technical Journal 39: 1253–1265.

#### Gilbert Burst Error Model (cont.)

Probability g of staying in good state G as a function of p<sub>b</sub> and b

$$g = (1 - p_b) + p_b (b - p_b) / (1 - p_b)$$

- Steady state

- probability of being in good state G is (1-b) / (2-b-g)

- probability of being in bad state B is (1-g) / (2-b-g)

- Model to determine bit error probability w/o DFE error propagation

■ DFE slicer bit error probability w/o error propagation  $p_{sl} = (1-b) p_{bl}$

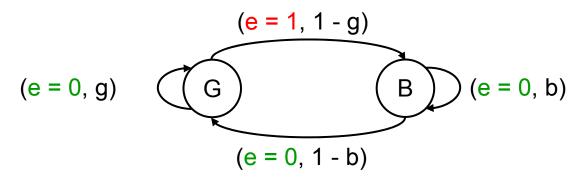

#### **Definition of Coding Gain**

- Uncoded case for 0% overclocking (s=0)

- SNR<sub>b</sub> = SNR at DFE slicer input assuming previously detected bits are correct and 0% overclocking

- Coding gain depends on target BER, e.g.

1e-15

- Random coding gain in coded case with s% overclocking can be computed using independent symbol error model specified by p<sub>sym</sub>

- Total coding gain in coded case with s% overclocking computed using Gilbert burst error model specified by the parameters p<sub>b</sub> and state transition probability b

#### **Computation of Coding Gain**

p<sub>d</sub> = Bit error rate (BER) at RS decoder output

Uncoded: SNR<sub>b</sub> = SNR at DFE slicer input in uncoded case with 0% overclocking

1)

$$p_{sl} = Q (sqrt(SNR_b))$$

, e.g.,  $p_{sl} = 0.5 erfc (sqrt (SNR_b / 2))$  for NRZ signaling

2)

$$p_d = p_{sl} / (1-b) = f (SNR_b)$$

Coded: SNR<sub>c</sub> = SNR at DFE slicer input in coded case with s% overclocking

1)  $p_d = g(p_b)$  from decoding with correlated bit errors at RS decoder input

2)

$$p_{sl} = (1-b) p_b$$

3)

$$SNR_c = (Q^{-1}(p_{sl}))^2$$

, e.g.,  $SNR_c = 2 (erfc^{-1}(2 p_{sl}))^2$  for NRZ signaling

4)

$$SNR_c$$

[dB] =  $SNR_b$  [dB] - s D [dB] as in bhoja\_01\_0911.pdf

D [dB] = SNR degradation in dB per 1% overclocking, D [dB] = 0.043 dB in AWGN channel

D [dB] ~ (increase in insertion loss for 1% overclocking) / 2 = 0.15 - 0.2 dB on channels w/ 30 - 40 dB loss

5)

$$p_d = h (SNR_b)$$

Random coding gain:  $p_d = g_{random}(p_b)$  is computed using independent symbol error model  $\Rightarrow p_d = h_{random}(SNR_b)$

Total coding gain:  $p_d = g_{Gilbert}(p_b)$  is computed using Gilbert burst error model  $\rightarrow p_d = h_{Gilbert}(SNR_b)$

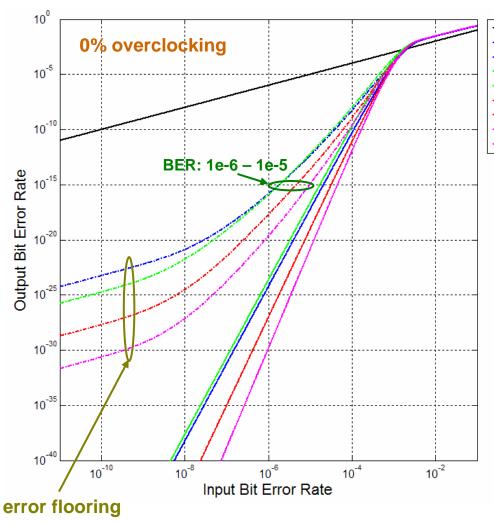

#### Post-Decoding Bit Error Rate vs. Pre-Decoding Bit Error Rate

- uncoded

RS(468,456), t=6, m=9, random

RS(468,456), t=6, m=9, burst

RS(528,516), t=6, m=10, random

RS(528,516), t=6, m=10, burst

RS(528,514), t=7, m=10, random

RS(528,514), t=7, m=10, burst

RS(632,616), t=8, m=10, random

- Assumptions: target BER 1e-15, b=0.5,

D [dB] = 0.175 dB

- BER = 1e-6 to 1e-5 at DFE output in order to achieve target BER 1e-15 at RS decoder output

- Error flooring due to error propagation at DFE output

- Error floors decrease with increasing t

- At post-decoding bit error rates in the range of 1e-18 to 1e-12 and for 6 ≤ t ≤ 8, error flooring is not expected to be a problem

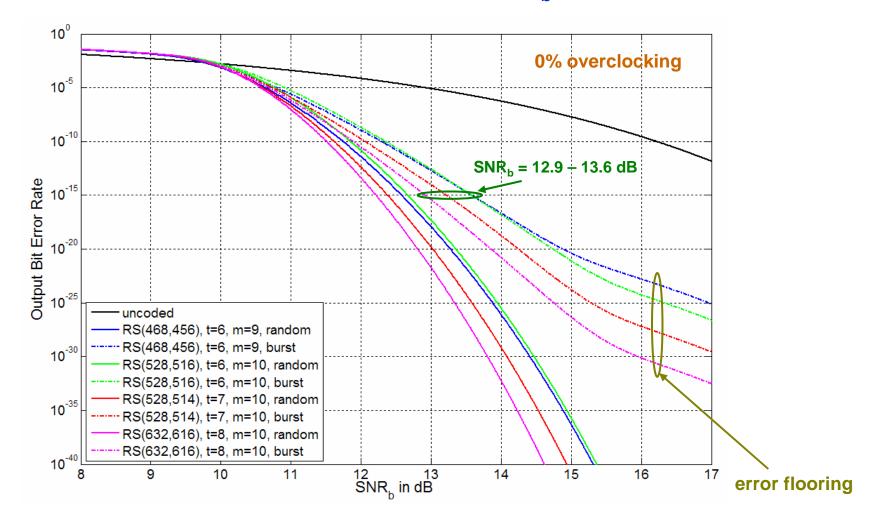

### Post-Decoding Bit Error Rate vs. SNR<sub>b</sub>

For 0% overclocking and  $6 \le t \le 8$ , SNR<sub>b</sub> at DFE slicer input must be 12.9 - 13.6 dB to achieve target bit error rate 1e-15

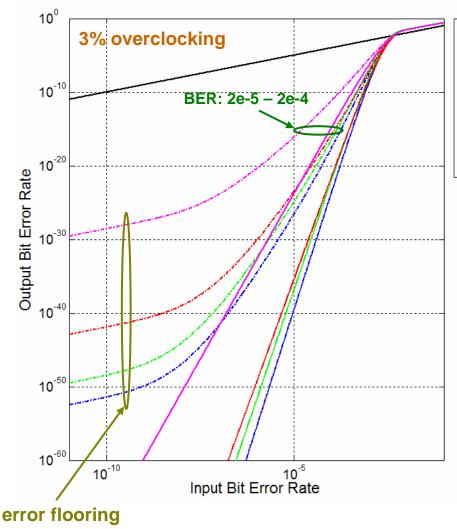

#### Post-Decoding Bit Error Rate vs. Pre-Decoding Bit Error Rate

- Assumptions: target BER 1e-15, b=0.5,

D [dB] = 0.175 dB

- BER = 2e-5 2e-4 at DFE output in order to achieve target BER 1e-15 at RS decoder output

- Error flooring due to error propagation at DFE output

- Error floors decrease with increasing t

- At post-decoding bit error rates in the range of 1e-18 to 1e-12 and for 8 ≤ t ≤ 15, error flooring is not expected to be a problem

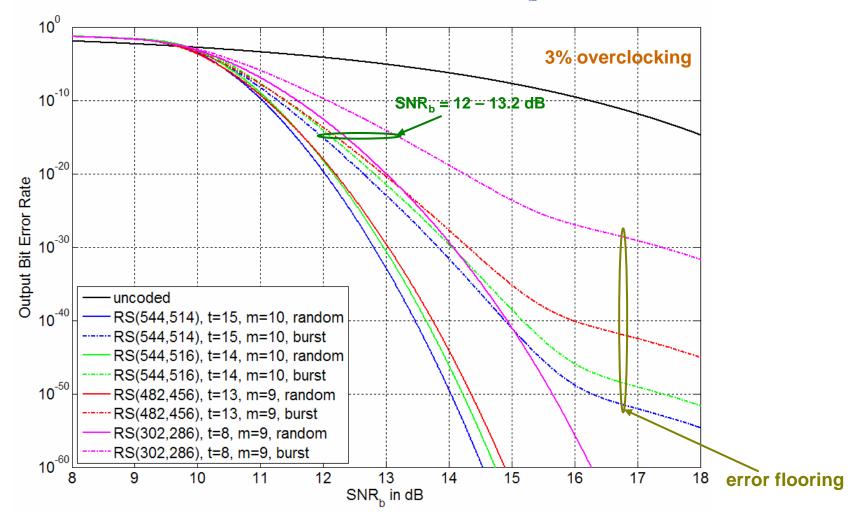

### Post-Decoding Bit Error Rate vs. SNR<sub>b</sub>

For 3% overclocking and  $8 \le t \le 15$ , SNR<sub>b</sub> is in the range 12 - 13.2 dB to achieve target bit error rate 1e-15

**IBM**

#### Summary

- Introduced error models to evaluate RS decoder performance in the presence of DFE error propagation

- Defined random and total coding gain as a performance measure

- Parameters required to compute coding gain: n, t, m, b, s, D, target BER

- Presented methodology to compute random and total coding gain

- Compared performance of various transcoding and FEC schemes by computing

- post-decoding bit error rate vs. pre-decoding bit error rate

- post-decoding bit error rate vs. SNR<sub>b</sub>

- Demonstrated existence of error floors which occur below 1e-20 if RS error correction capability t ≥ 6

## Backup

### Comparison of Transcoding/FEC Schemes

| Total<br>Coding<br>Gain [dB] | Random<br>Coding<br>Gain [dB] | Latency<br>[ns] | TC block size [bit] | FEC | k   | n   | t  | m  | Line Rate<br>[Gb/s] | Overclocking [%] | Multiplier of<br>156.25 MHz |

|------------------------------|-------------------------------|-----------------|---------------------|-----|-----|-----|----|----|---------------------|------------------|-----------------------------|

| 4.51                         | 5.51                          | 87              | 513                 | RS  | 456 | 468 | 6  | 9  | 25.78125            | 0                | 165                         |

| 4.52                         | 5.42                          | 108             | 516                 | RS  | 516 | 528 | 6  | 10 | 25.78125            | 0                | 165                         |

| 4.87                         | 5.71                          | 108             | 514                 | RS* | 514 | 528 | 7  | 10 | 25.78125            | 0                | 165                         |

| 5.17                         | 5.88                          | 128             | 513                 | RS  | 616 | 632 | 8  | 10 | 25.78125            | 0                | 165                         |

| 5.17                         | 6.03                          | 87              | 513                 | RS  | 456 | 472 | 8  | 9  | 25.92773            | 0.6              | 165 15/16                   |

| 5.13                         | 5.93                          | 108             | 514                 | RS  | 514 | 530 | 8  | 10 | 25.93750            | 0.6              | 166                         |

| 4.89                         | 6.14                          | 56              | 514                 | RS  | 286 | 302 | 8  | 9  | 26.56250            | 3                | 170                         |

| 5.88                         | 6.81                          | 87              | 513                 | RS  | 456 | 482 | 13 | 9  | 26.56250            | 3                | 170                         |

| 5.96                         | 6.81                          | 107             | 516                 | RS  | 516 | 544 | 14 | 10 | 26.56250            | 3                | 170                         |

| 6.10                         | 6.92                          | 107             | 514                 | RS  | 514 | 544 | 15 | 10 | 26.56250            | 3                | 170                         |

Assumptions: target BER 1e-15, b=0.5, D [dB] = 0.175 dB

<sup>\*</sup> Z. Wang, H. Jiang and C. Chen, Oct. 2011