# 97. Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA) sublayer, Physical Medium Dependent (PMD) sublayer, and baseband medium, type 1000BASE-T1

#### 97.1 Overview

This clause defines the type 1000BASE-T1 Physical Coding Sublayer (PCS), type 1000BASE-T1 Physical Medium Attachment (PMA) sublayer, and type 1000BASE-T1 Physical Medium Dependent (PMD). Together, the PCS, PMA, and PMD sublayers comprise a 1000BASE-T1 Physical Layer (PHY). Provided in this clause are fully functional and electrical specifications for the type 1000BASE-T1 PCS, PMA, and PMD. This clause also specifies the critical parameters of the baseband medium used with 1000BASE-T1 PHY.

The 1000BASE-T1 PHY is one of the Gigabit Ethernet family of high-speed full-duplex network specifications, capable of operating at 1000 Mb/s and intended to be operated over a single pair of balanced copper cabling, referred to as an automotive link segment (Type A) or additional link segment (Type B), defined in 97.5.6. The cabling supporting the operation of the 1000BASE-T1 PHY is defined in terms of performance requirements between the attachment points (Medium Dependent Interface (MDI)), allowing implementers to provide their own cabling to operate the 1000BASE-T1 PHY as long as the normative requirements included in this Clause are met.

This clause also specifies 1000BASE-T1 Low Power Idle (LPI) as part of Energy-Efficient Ethernet (EEE). This allows the PHY to enter a low power mode of operation during periods of low link utilization as described in Clause 78.

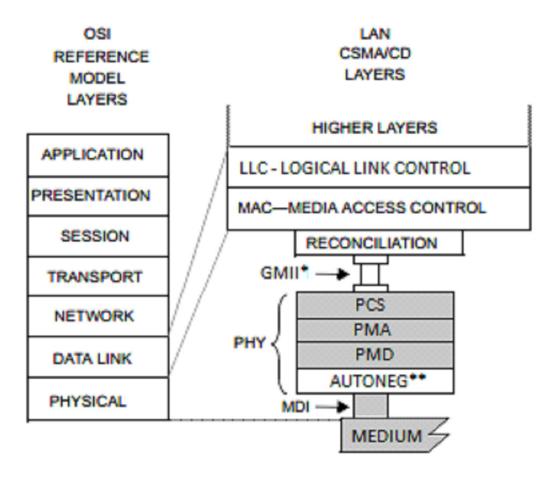

# 97.1.1 Relationship of 1000BASE-T1 to other standards

Relations between the 1000BASE-T1 PHY, the ISO Open Systems Interconnection (OSI) Reference Model, and the IEEE 802.3 CSMA/CD LAN Model are shown in Figure 97–1. The PHY sublayers (shown shaded) in Figure 97–1 connect one Clause 4 Media Access Control (MAC) layer to the medium. Auto-Negotiation for 1000BASE-T1 is defined in Clause 98. GMII is defined is Clause 35.

Figure 97–1—Relationship of 1000BASE-T1 PHY to the ISO/IEC OSI reference model and the IEEE 802.3 CSMA/CD LAN Model

MDI = MEDIUM DEPENDENT INTERFACE

GMII = GIGABIT MEDIA INDEPENDENT INTERFACE

AUTONEG = AUTO-NEGOTIATION

PCS = PHYSICAL CODING SUBLAYER

PMA = PHYSICAL MEDIUM ATTACHMENT

PHY = PHYSICAL LAYER DEVICE

PMD = PHYSICAL MEDIUM DEPENDENT

\* GMII is optional

\*\* AUTONEG is optional

# 97.1.2 Operation of 1000BASE-T1

The 1000BASE-T1 PHY operates using full-duplex communications (using echo cancellation) over a single pair of balanced copper cabling with an effective rate of 1 Gb/s in each direction simultaneously while meeting the requirements (EMC, temperature, etc.) of automotive and industrial environments. The PHY supports operation on two types of link segments:

- a) An automotive link segment supporting up to four inline connectors using unshielded balanced copper cabling for at least 15 meters (referred to as link segment type A).

- b) An additional link segment supporting up to four inline connectors using balanced copper cabling for at least 40 meters to support applications requiring additional physical reach, such as industrial and automation controls and transportation (aircraft, railway, bus and heavy trucks). This link segment is referred to as link segment type B.

The 1000BASE-T1 PHY utilizes 3 level Pulse Amplitude Modulation (PAM3) transmitted at a 750 MHz rate. A 15-bit scrambler is used to improve the EMC performance. GMII TX\_D, TX\_EN, and TX\_ER are encoded together in using 81B encoding where 10 cycles of GMII data and control are encoded together in 81 bits to reduce the overhead. To maintain a bit error ratio (BER) of less than or equal to 10<sup>-10</sup>, the 1000BASE-T1 PHY adds a 396 bit Reed Solomon Forward Error Correction (RS FEC) code to each group of forty-five 81B blocks (containing 450 octets of GMII data). The PAM3 mapping, scrambler, RS FEC, and 81B encoder/decoder are all contained in the PCS (see 97.3).

Auto-Negotiation (Clause 98) may optionally be used by 1000BASE-T1 devices to detect the abilities (modes of operation) supported by the device at the other end of a link segment, determine common abilities, and configure for joint operation. Auto-Negotiation is performed upon link startup through the use of half-duplex differential Manchester encoding.

A 1000BASE-T1 PHY can be configured either as a MASTER PHY or as a SLAVE PHY. A MASTER PHY uses a local clock to determine the timing of transmitter operations. A SLAVE PHY recovers the clock from the received signal and uses it to determine the timing of transmitter operations. When Auto-Negotiation is used, The MASTER-SLAVE relationship between two stations sharing a link segment is established during Auto-Negotiation (see Clause 98). If Auto-Negotiation is not used, MASTER-SLAVE relationship is established by management or hardware configuration of the PHY, and the MASTER and SLAVE are synchronized by a PHY Link Synchronization function in the PHY (see 97.6).

A 1000BASE-T1 PHY may optionally support Energy Efficient Ethernet (see Clause 78) and advertise the EEE capability as described in 78.3. The EEE capability is a mechanism by which 1000BASE-T1 PHYs are able to reduce power consumption during periods of low link utilization.

The 1000BASE-T1 PMA couples messages from the PCS to the MDI and provides clock recovery, link management and PHY Control functions. The PMA provides full duplex communications at 750 MBd over the single pair of balanced copper cabling. PMA functionality is described in 97.4. The PMD is described in 97.5. The MDI is specified in 97.8.

#### 97.1.2.1 Physical Coding Sublayer (PCS)

The 1000BASE-T1 PCS couples a Gigabit Media Independent Interface (GMII), as described in Clause 35, to a Physical Medium Attachment (PMA) sublayer, described in 97.4, which supports communication over a single pair of balanced copper cabling.

The PCS comprises the PCS Reset function, PCS Transmit, and PCS Receive. The Transmit and Receive functions start immediately after completion of the Reset function and run simultaneously and asynchronously with relation to each other.

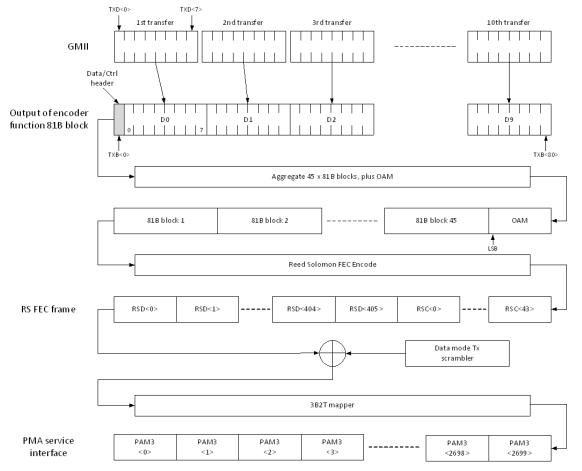

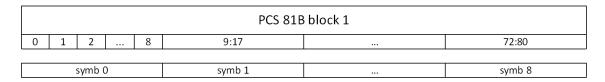

In Data Mode, the PCS Transmit function data path starts with the GMII interface, where TXD, TX\_EN, and TX\_ER input data to the PCS every 8 ns (as clocked by GTX\_CLK). Data and control from ten GTX\_CLK cycles are encoded into an 81 bit "81B block" that encodes every possible combination of data and control (control signals include error propagation, assert low power idle, and inter-frame signaling). Each set of forty-five 81B blocks along with 9 bits of OAM data (see 97.7) processed by a Reed Solomon FEC encoder (RS FEC). The RS encoder adds 396 bits of FEC data and the 4050 bits (forty-five 81B blocks = 3645 bits, 9 bits of OAM, and 396 bits of FEC data) are scrambled using a 15-bit side-stream scrambler. Each 3 bits of the scrambled data is converted to 2 ternary PAM3 symbols by the 3B2T mapper (the 4050 bits in the RS frame become 2700 PAM3 symbols) and passed to the PMA. PCS transmit functions are described in 97.3.2.2.

In Data Mode, the PCS Receive function data path operates in the opposite order as the transmit path. The incoming PAM3 symbols are synchronized to frame boundaries. Within each frame, each two PAM3 symbols are de-mapped to 3 bits by the 3B2T demapper (the 2700 PAM3 symbols are converted to 4050 bits). The data is then descrambled and passed to the RS FEC decoder for data validation and correction. Finally, each of the forty-five 81B blocks is decoded into GMII data or control. PCS data mode receive is described in 97.3.2.3.

In Training Mode (see 97.4.2.5), the PCS transmits and receives data sequences to synchronize the RS FEC blocks, learn the Data Mode scrambler seed, and exchange EEE and OAM capabilities. The training mode uses PAM2 encoding.

# 97.1.2.2 Physical Medium Attachment (PMA) sublayer

The 1000BASE-T1 PMA transmits/receives symbol streams to/from the PCS onto the single balanced twisted pair and provides the clock recovery, link monitor and the 1000BASE-T1 PHY Control function. The PMA provides full duplex communications at 750 MBd.

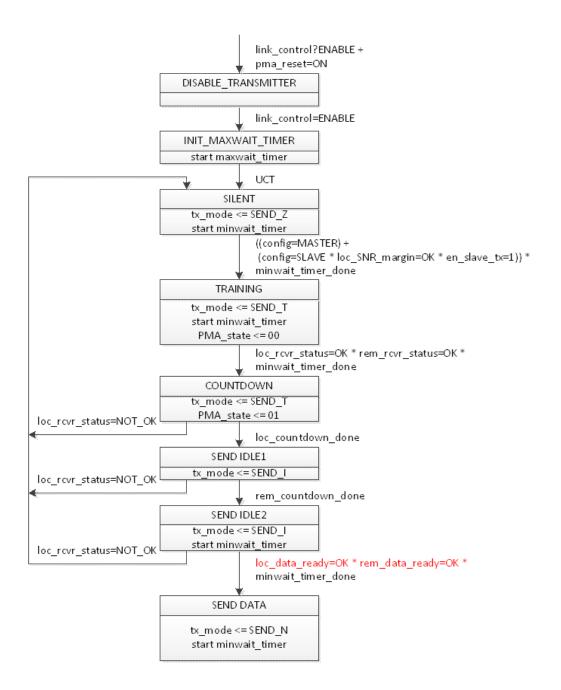

The PMA PHY Control function generates signals that control the PCS and PMA sublayer operations. PHY Control is enabled following the completion of Auto-Negotiation or PHY Link Synchronization and provides the start-up functions required for successful 1000BASE-T1 operation. It determines whether the PHY operates in a disabled state, a training state, or a data state where MAC frames can be exchanged between the link partners.

The Link Monitor determines the status of the underlying link channel and communicates this status to other functional blocks. A failure of the receive channel causes data mode operation to stop and Auto-Negotiation or Link Synchronization to restart.

#### 97.1.2.3 Physical Medium Dependent (PMD) sublayer

The 1000BASE-T1 PMD (see 97.5) defines the transmit and receive electrical characteristics. The PMD also specifies the minimum link segment characteristics, EMC requirements, and test modes.

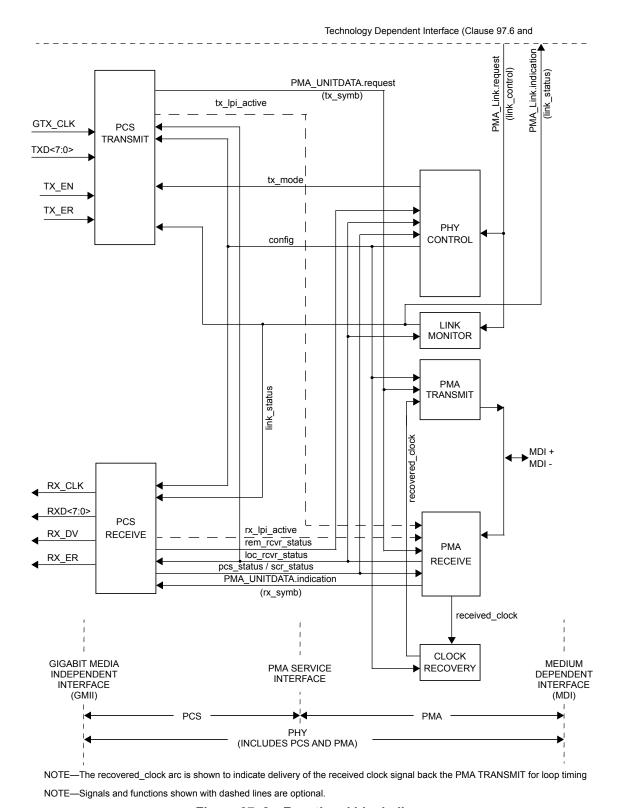

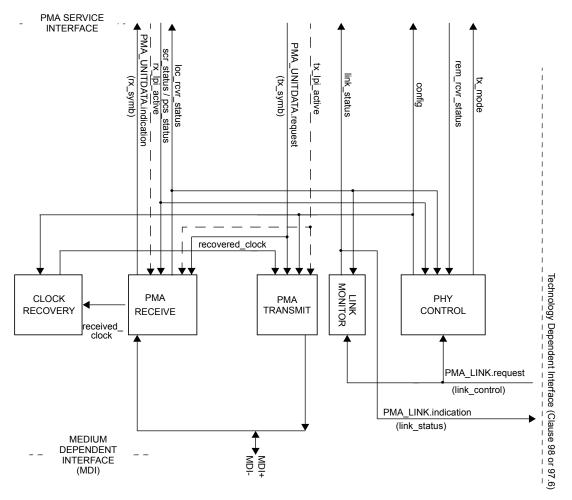

Figure 97–2—Functional block diagram

# 97.1.2.4 EEE capability

A 1000BASE-T1 PHY may optionally support the EEE capability, as described in 78.3. The EEE capability is a mechanism by which 1000BASE-T1 PHYs are able to reduce power consumption during periods of low link utilization. PHYs can enter this mode of operation after completing training. Each direction of the full duplex link is able to enter and exit the LPI mode independently, supporting symmetric and asymmetric LPI operation. This allows power savings when only one side of the full duplex link is in a period of low utilization. The transition to or from LPI mode shall cause no data frames be lost or corrupted.

In the transmit direction the transition to the LPI transmit mode begins when the PCS transmit function detects an "Assert Low Power Idle" condition on the GMII in the last 80B/81B block of a frame. At the next RS frame the PCS transmits a sleep signal composed of an entire RS frame containing only LP\_IDLE. The sleep signal indicates to the link partner that the transmit function of the PHY is entering the LPI transmit mode. Immediately after the transmission of the sleep frame, the transmit function of the local PHY enters the LPI transmit mode. While the transmit function is in the LPI mode the PHY may disable data path and control logic to save additional power. Periodically the transmit function of the local PHY transmits refresh frames that may be used by the link partner to update adaptive filters and timing circuits in order to maintain link integrity. LPI mode may begin with quiet signaling, a full refresh period, or a wake frame. The quiet-refresh cycle continues until the PCS function detects a condition that is not Assert Low Power Idle on the GMII. This condition signals to the PHY that the LPI transmit mode should end. At the next RS frame the PCS transmits a wake frame composed of an entire RS frame containing only Idle. On the next RS frame normal power mode shall resume.

Support for EEE capability is advertised during Training. See 97.4.2.5.5 for details. Transitions to and from the LPI transmit mode are controlled via GMII signaling. Transitions to and from the LPI receive mode are controlled by the link partner using sleep and wake signaling.

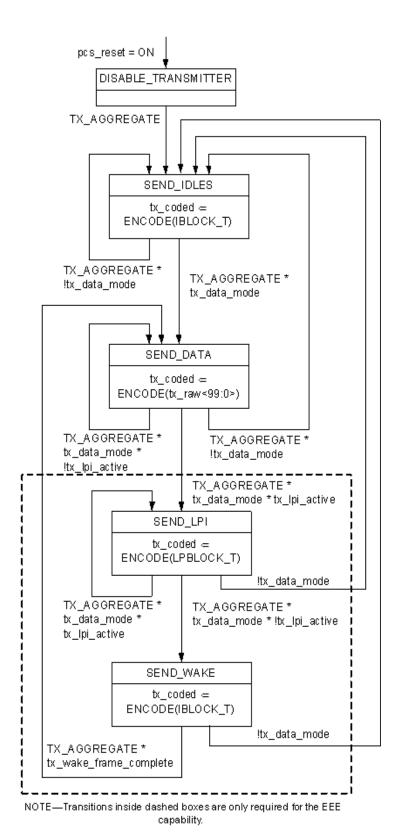

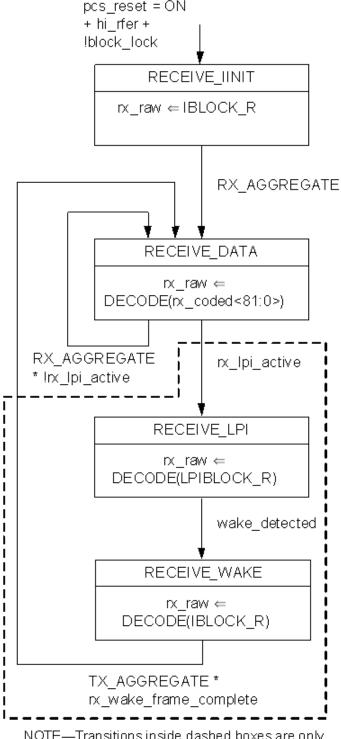

The PCS 80B/81B Transmit state diagram in Figure 97–14 includes additional states for EEE. The PCS 80B/81B Receive state diagram in Figure 97–15 includes additional states for EEE.

#### 97.1.2.5 Link Synchronization

The Link Synchronization function is used when Auto-Negotiation is disabled to synchronize between the MASTER PHY and SLAVE PHY before training starts. Link Synchronization provides a fast and reliable mechanism for the link partner to detect the presence of the other, validate link, and start the timers used by the link monitor. Link Synchronization operates in a half-duplex fashion. Based on timers, the MASTER PHY sends a synchronization sequence for 1 us. If there is no response from the slave, the MASTER repeats by sending a synchronization sequence every 5 us. If the slave detects the sequence, it responds by responding with a synchronization sequence for 1 us (after the MASTER has stopped transmitting). If no other detection happens after the slave response for 4 us then Link Synchronization is successfully complete, link monitor timers are started, and the PHY Control state machine starts Training. Link synchronization is defined in 97.6.

# 97.1.3 Signaling

1000BASE-T1 signaling is performed by the PCS generating continuous code-group sequences that the PMA transmits over the single pair of balanced copper cabling. The signaling scheme achieves a number of objectives including:

- a) Algorithmic mapping from TXD<7:0> to PAM3 symbols in the transmit path.

- b) Algorithmic mapping from PAM3 symbols to TXD<7:0> in the receive path

- c) Adding FEC coded data to transmit and validating data using FEC on receive

- d) Uncorrelated symbols in the transmitted symbol stream.

- e) No correlation between symbol streams traveling both directions.

- f) Ability to signal the status of the local receiver to the remote PHY to indicate that the local receiver is not operating reliably and requires retraining.

- g) Optionally, ability to signal to the remote PHY that transmit in entering the LPI mode or exiting the LPI mode and returning to normal operation.

The PHY may operate in three basic modes, normal mode, training mode, or an optional LPI mode.

In the normal mode, PCS generates code-groups that represent data, control, or idles for transmission by the PMA.

In the training mode, the PCS is directed to generate only a PAM2 pattern with periodic embedded data which enables the receiver at the other end to train and synchronize timing, scrambler seeds, and capabilities. The LPI mode is enabled separately in each direction (see LPI signaling in 97.3.5). When transmitting in LPI mode, the PCS is directed to generate zero symbols and periodically send a REFRESH pattern to keep the two PHYs synchronized (see 97.3.2.2.16).

#### 97.1.4 Interfaces

All 1000BASE-T1 PHY implementations are compatible at the MDI and at a physically exposed GMII, if made available. Physical implementation of the GMII is optional. Designers are free to implement circuitry within the PCS and PMA in an application-dependent manner provided that the MDI and GMII (if the GMII is implemented) specifications are met. System operation from the perspective of signals at the MDI and management objects are identical whether the GMII is implemented or not.

#### 97.1.5 Conventions in this clause

The body of this clause contains state diagrams, including definitions of variables, constants, and functions. Should there be a discrepancy between a state diagram and descriptive text, the state diagram prevails.

The notation used in the state diagrams follows the conventions of 21.5.

The values of all components in test circuits shall be accurate to within ±1% unless otherwise stated.

Default initializations, unless specifically specified, are left to the implementer.

# 97.2 1000BASE-T1 Service Primitives and Interfaces

1000BASE-T1 transfers data and control information across the following four service interfaces:

- a) Gigabit Media Independent Interface (GMII)

- b) Technology Dependent Interface

- c) PMA service interface

- d) Medium dependent interface (MDI)

The GMII is specified in Clause 35; the Technology Dependent Interface is specified in 97.6 and Clause 98. The PMA service interface is defined in 97.2.2 and the MDI is defined in 97.8.

# 97.2.1 Technology Dependent Interface

1000BASE-T1 uses the following service primitives to exchange status indications and control signals across the Technology Dependent Interface as specified in 97.6 or Clause 98:

PMA LINK.request (link control)

PMA LINK.indication (link status)

# 97.2.1.1 PMA LINK.request

This primitive allows the Auto-Negotiation or the PHY Link Synchronization algorithm to enable and disable operation of the PMA, as specified in 98.4.2 or 97.6, respectively.

#### 97.2.1.1.1 Semantics of the primitive

PMA LINK.request (link control)

The link\_control parameter can take on one of two values: DISABLE, or ENABLE.

DISABLE Used by the Auto-Negotiation or PHY Link Synchronization process to

disable the PHY.

ENABLE Used by the Auto-Negotiation or PHY Link Synchronization process to

enable the PHY.

#### 97.2.1.1.2 When generated

Auto-Negotiation or PHY Link Synchronization generates this primitive to indicate a change in link\_control as described in 97.6 or Clause 98.

# 97.2.1.1.3 Effect of receipt

This primitive affects the operation of the PMA Link Monitor function as defined in 97.4.2.6 and the PMA PHY Control function as defined in 97.4.2.5.

#### 97.2.1.2 PMA\_LINK.indication

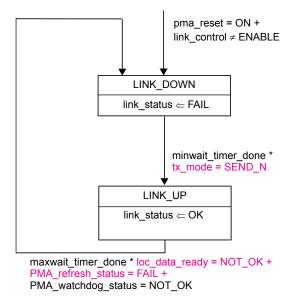

This primitive is generated by the PMA to indicate the status of the underlying medium as specified in 98.4.1. This primitive informs the PCS, PMA PHY Control function, and the Auto-Negotiation or PHY Link Synchronization process about the status of the underlying link.

# 97.2.1.2.1 Semantics of the primitive

PMA LINK.indication (link status)

The link\_status parameter can take on one of two values: FAIL or OK.

FAIL No valid link established.

OK The Link Monitor function indicates that a valid 1000BASE-T1 link is established.

Reliable reception of signals transmitted from the remote PHY is possible.

# 97.2.1.2.2 When generated

The PMA generates this primitive to indicate a change in link\_status in compliance with the state diagram given in Figure 97–21.

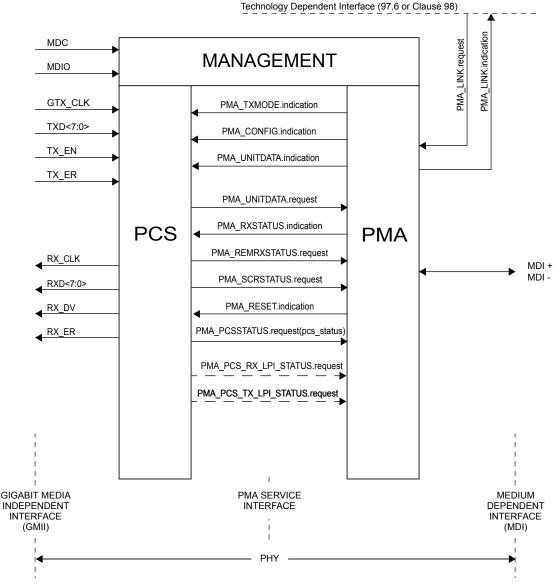

#### 97.2.1.2.3 Effect of receipt 1 2 The effect of receipt of this primitive is specified in 98.4.1. 3 4 5 97.2.2 PMA service interface 6 7 1000BASE-T1 uses the following service primitives to exchange symbol vectors, status indications, and control signals across the service interfaces: 8 9 PMA TXMODE.indication (tx mode) 10 PMA CONFIG. indication (config) 11 PMA UNITDATA.request (tx symb) 12 PMA UNITDATA.indication (rx symb) 13 PMA SCRSTATUS.request (scr status) 14 PMA PCSSTATUS.request (pcs status) 15 PMA RXSTATUS.indication (loc revr status) 16 17 PMA DATAREADY.indication (loc data ready) PMA REMRXSTATUS.request (rem rcvr status) 18 19 PMA\_REMDATAREADY.request (rem\_data\_ready) PMA RESET.indication() 20 21 The use of these primitives is illustrated in Figure 97–3. Connections from the management interface 22 (signals MDC and MDIO) to the sublayers are pervasive and are not shown in Figure 97–3. 23 24 EEE-capable PHYs additionally support the following service primitives: 25 26 PMA PCS RX LPI STATUS.request (rx lpi active) 27 PMA PCS TX LPI STATUS.request (tx lpi active) 28 97.2.2.1 PMA\_TXMODE.indication 29 30 The transmitter in a 1000BASE-T1 link normally sends over the MDI symbols that represent a GMII data 31 stream with framing, scrambling and encoding of data, control information, or idles. 32 33 97.2.2.1.1 Semantics of the primitive 34 35 PMA TXMODE.indication (tx mode) 36 37 38 PMA TXMODE indication specifies to PCS Transmit via the parameter tx mode what sequence of code-groups the PCS should be transmitting. The parameter tx mode can take on one of the following four 39 values of the form: 40 41 SEND N This value is continuously asserted during transmission of sequences of 42 symbols representing a GMII data stream in data mode. 43 SEND I This value is continuously asserted when transmission of sequences of 44 idle symbols is to take place. 45 SEND T This value is continuously asserted in case transmission of sequences of 46 code-groups representing the training mode is to take place. 47 SEND Z This value is continuously asserted in case transmission of zeros is required. 48 49 97.2.2.1.2 When generated 50 51 52 The PMA PHY Control function generates PMA TXMODE.indication messages to indicate a change in tx mode. 53

#### 97.2.2.1.3 Effect of receipt

Upon receipt of this primitive, the PCS performs its transmit function as described in 97.3.2.2.

NOTE—Service interface primitives shown with dashed lines are optional.

Figure 97-3—1000BASE-T service interfaces

# 97.2.2.2 PMA\_CONFIG.indication

Each PHY in a 1000BASE-T1 link is capable of operating as a MASTER PHY and as a SLAVE PHY. If the Auto-Negotiation process is enabled, PMA\_CONFIG MASTER-SLAVE configuration is determined during Auto-Negotiation (Clause 98) and the result is provided to the PMA. If the Auto-Negotiation process is not enabled, PMA\_CONFIG MASTER-SLAVE configuration is pre-determined to be Master or Slave via management control during initialization or via default hardware set-up.

53 54

#### 16 March 2015 97.2.2.1 Semantics of the primitive 1 2 3 PMA CONFIG.indication (config) 4 5 PMA CONFIG indication specifies to PCS and PMA Transmit via the parameter config whether the PHY operates as a MASTER PHY or as a SLAVE PHY. The parameter config can take on one of the following 6 7 two values of the form: 8 9 MASTER This value is continuously asserted when the PHY operates as a MASTER PHY. SLAVE This value is continuously asserted when the PHY operates as a SLAVE PHY. 10 11 97.2.2.2.2 When generated 12 13 PMA generates PMA CONFIG. indication messages to indicate a change in config. 14 15 97.2.2.2.3 Effect of receipt 16 17 PCS and PMA Clock Recovery perform their functions in MASTER or SLAVE configuration according to 18 19 the value assumed by the parameter config. 20 21 97.2.2.3 PMA\_UNITDATA.request 22 This primitive defines the transfer of code-groups in the form of the tx symb parameter from the PCS to the 23 PMA. The code-groups are obtained in the PCS Transmit function using the encoding rules defined in 24 97.3.2.2 to represent GMII data and control streams or other sequences. 25 26 27 97.2.2.3.1 Semantics of the primitive 28 29 PMA UNITDATA.request (tx symb) 30 During transmission, the PMA UNITDATA request simultaneously conveys to the PMA via the parameter 31 tx symb the value of the symbols to be sent over the MDI. The tx symb may take on one of the values in the 32 33 set $\{-1, 0, 1\}$ 34 97.2.2.3.2 When generated 35 36 The PCS generates PMA UNITDATA request (tx symb) synchronously with every transmit clock cycle. 37 38 97.2.2.3.3 Effect of receipt 39 40 41 Upon receipt of this primitive the PMA transmits on the MDI the signals corresponding to the indicated symbols after processing with optional transmit filtering and other specified PMA Transmit processing. The 42 parameter tx symb is also used by the PMA Receive function to process the signals received on the MDI for 43 cancelling the echo. 44 45 97.2.2.4 PMA\_UNITDATA.indication 46 47 This primitive defines the transfer of code-groups in the form of the rx symb parameter from the PMA to 48 the PCS. 49 50 97.2.2.4.1 Semantics of the primitive 51

PMA UNITDATA.indication (rx symb)

During reception the PMA UNITDATA indication conveys to the PCS via the parameter rx symb the value 1 of symbols detected on the MDI during each cycle of the recovered clock. 2 3 4 97.2.2.4.2 When generated 5 The PMA generates PMA UNITDATA.indication (rx symb) messages synchronously for every symbol 6 received at the MDI. The nominal rate of the PMA UNITDATA indication primitive is 750 MHz, as 7 8 governed by the recovered clock. 9 97.2.2.4.3 Effect of receipt 10 11 The effect of receipt of this primitive is unspecified. 12 13 97.2.2.5 PMA\_SCRSTATUS.request 14 15 This primitive is generated by PCS Receive to communicate the status of the descrambler for the local PHY. 16 The parameter scr status conveys to the PMA Receive function the information that the training mode 17 descrambler has achieved synchronization. 18 19 97.2.2.5.1 Semantics of the primitive 20 21 22 PMA SCRSTATUS.request (scr status) 23 The scr status parameter can take on one of two values of the form: 24 25 26 OK The training mode descrambler has achieved synchronization. 27 NOT OK The training mode descrambler is not synchronized. 28 97.2.2.5.2 When generated 29 30 PCS Receive generates PMA SCRSTATUS request messages to indicate a change in scr status. 31 32 97.2.2.5.3 Effect of receipt 33 34 The effect of receipt of this primitive is specified in 97.4.2.4 and 97.4.2.5. 35 36 97.2.2.6 PMA PCSSTATUS.request 37 38 This primitive is generated by PCS Receive to indicate the fully operational state of the PCS for the local 39 PHY. The parameter pcs status conveys to the PMA Receive function the information that the PCS is 40 41 operating reliably in data mode. 42 97.2.2.6.1 Semantics of the primitive 43 44 PMA PCSSTATUS.request (pcs status) 45 46 47 The pcs status parameter can take on one of two values of the form: 48 OK The PCS is operating reliably in data mode. 49 NOT OK The PCS is not operating reliably in data mode. 50 51 97.2.2.6.2 When generated 52 53 PCS Receive generates PMA PCSSTATUS.request messages to indicate a change in pcs status. 54

#### 97.2.2.6.3 Effect of receipt

The effect of receipt of this primitive is specified in 97.4.2.5.9 and 97.4.5.

# 97.2.2.7 PMA\_RXSTATUS.indication

This primitive is generated by PMA Receive to indicate the status of the receive link at the local PHY. The parameter loc\_rcvr\_status conveys to the PCS Transmit, PCS Receive, PMA PHY Control function, and Link Monitor the information on whether the status of the overall receive link is satisfactory or not. Note that loc\_rcvr\_status is used by the PCS Receive decoding functions. The criterion for setting the parameter loc\_rcvr\_status is left to the implementor. It can be based, for example, on observing the mean-square error at the decision point of the receiver and detecting errors during reception of symbol stream.

# 97.2.2.7.1 Semantics of the primitive

PMA RXSTATUS.indication (loc revr status)

The loc rcvr status parameter can take on one of two values of the form:

OK This value is asserted and remains true during reliable operation of the receive

link for the local PHY.

NOT OK This value is asserted whenever operation of the link for the local PHY is unreliable.

# 97.2.2.7.2 When generated

PMA Receive generates PMA\_RXSTATUS.indication messages to indicate a change in loc\_rcvr\_status on the basis of signals received at the MDI.

#### 97.2.2.7.3 Effect of receipt

The effect of receipt of this primitive is specified in Figure 97–22, 97.3.2.3, 97.4.2.5, and 97.4.5.

# 97.2.2.8 PMA\_DATAREADY.indication

This primitive is generated by PMA Receive to indicate the local PHY is ready or not ready to receive data. The parameter loc data ready is conveyed to the link partner by the PCS as defined in Table 97-1.

#### 97.2.2.8.1 Semantics of the primitive

PMA\_DATAREADY.indication (loc\_data\_ready)

The loc\_data\_ready parameter can take on one of two values of the form:

OK The local PHY is ready to receive data.

NOT\_OK The local PHY is not ready to receive data.

# 97.2.2.8.2 When generated

PMA Receive generates PMA\_DATAREADY.indication messages to indicate a change in loc\_data\_ready based on loc\_rcvr\_status and pcs\_status values.

# 97.2.2.8.3 Effect of receipt

The effect of receipt of this primitive is specified in Figure 97–22 and Figure 97-23.

# 97.2.2.9 PMA\_REMRXSTATUS.request

This primitive is generated by PCS Receive to indicate the status of the receive link at the remote PHY as communicated by the remote PHY via its encoding of its loc\_rcvr\_status parameter. The parameter rem\_rcvr\_status conveys to the PMA PHY Control function the information on whether reliable operation of the remote PHY is detected or not. The parameter rem\_rcvr\_status is set to the value received in the loc\_rcvr\_status bit in the InfoField from the remote PHY. The rem\_rcvr\_status is set to NOT\_OK if the PCS has not decoded a valid InfoField from the remote PHY.

# 97.2.2.9.1 Semantics of the primitive

PMA\_REMRXSTATUS.request (rem\_rcvr\_status)

The rem revr status parameter can take on one of two values of the form:

OK The receive link for the remote PHY is operating reliably.

NOT OK Reliable operation of the receive link for the remote PHY is not detected.

#### 97.2.2.9.2 When generated

The PCS generates PMA\_REMRXSTATUS.request messages to indicate a change in rem\_rcvr\_status based on the PCS decoding the loc\_rcvs\_status bit in InfoField messages received from the remote PHY during training.

#### 97.2.2.9.3 Effect of receipt

The effect of receipt of this primitive is specified in Figure 97–22.

# 97.2.2.10 PMA\_REMDATAREADY.request

This primitive is generated by PCS Receive to indicate whether the remote PHY is ready or not ready to receive data. Its value is received from the link partner by the PCS as defined in Table 97-1.

#### 97.2.2.10.1 Semantics of the primitive

PMA REMDATAREADY.request (rem\_data\_ready)

<u>The rem\_data\_ready parameter can take on one of two values of the form:</u>

OK The remote PHY is ready to receive data.

NOT\_OK The remote PHY is not ready to receive data.

# 97.2.2.10.2 When generated

The PCS generates PMA\_REMDATAREADY.request messages to indicate a change in rem\_data\_ready based on the PCS decoding the control words in Table 97-1 received from the remote PHY.

# 97.2.2.10.3 Effect of receipt

The effect of receipt of this primitive is specified in Figure 97–22.

|                                                                                                                                                                                                             |                                                                                           | 1        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|

| 97.2.2.11 PMA_R                                                                                                                                                                                             | ESET.indication                                                                           | 2 3      |

|                                                                                                                                                                                                             |                                                                                           | 4        |

| This primitive is us                                                                                                                                                                                        | ed to pass the PMA Reset function to the PCS (pcs_reset=ON) when reset is enabled.        | 5<br>6   |

| The PMA_RESET.                                                                                                                                                                                              | indication primitive can take on one of two values:                                       | 7        |

| TDIE D                                                                                                                                                                                                      |                                                                                           | 8        |

|                                                                                                                                                                                                             | set is enabled.                                                                           | 9<br>10  |

|                                                                                                                                                                                                             |                                                                                           | 11       |

| 97.2.2.11.1 When                                                                                                                                                                                            | generated                                                                                 | 12       |

| The PMA Reset fur                                                                                                                                                                                           | action is executed as described in 97.4.2.1.                                              | 13<br>14 |

| The T Wit Coset ful                                                                                                                                                                                         | netion is executed as described in 77.4.2.1.                                              | 15       |

| 97.2.2.11.2 Effec                                                                                                                                                                                           | t of receipt                                                                              | 16       |

|                                                                                                                                                                                                             |                                                                                           | 17       |

| The effect of receip                                                                                                                                                                                        | t of this primitive is specified in 97.4.2.1.                                             | 18<br>19 |

| 97.2.2.12 PMA P                                                                                                                                                                                             | 97.2.2.12 PMA_PCS_RX_LPI_STATUS.request                                                   |          |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                       |                                                                                           | 20<br>21 |

| When the PHY sup                                                                                                                                                                                            | ports the EEE capability this primitive is generated by the PCS receive function to indi- | 22       |

| cate the status of tl                                                                                                                                                                                       | ne receive link at the local PHY. The parameter PMA_PCS_RX_LPI_STATUS.request             | 23       |

| conveys to the PCS                                                                                                                                                                                          | transmit and PMA receive functions information regarding whether the receive function     | 24       |

| is in the LPI receive                                                                                                                                                                                       | e mode.                                                                                   | 25       |

|                                                                                                                                                                                                             |                                                                                           | 26       |

| 97.2.2.12.1 Sema                                                                                                                                                                                            | intics of the primitive                                                                   | 27<br>28 |

| PMA PCS RX LE                                                                                                                                                                                               | PI STATUS.request (rx lpi active)                                                         | 28       |

| I MA_I C5_KA_LI                                                                                                                                                                                             | 1_51A1 Ob. request (IX_lpi_active)                                                        | 30       |

| The rx_lpi_active p                                                                                                                                                                                         | arameter can take on one of two values of the form:                                       | 31       |

|                                                                                                                                                                                                             |                                                                                           | 32       |

| TRUE                                                                                                                                                                                                        | The receive function is in the LPI receive mode.                                          | 33       |

| FALSE                                                                                                                                                                                                       | The receive function is not in the LPI receive mode.                                      | 34       |

| 07.00.40.034//                                                                                                                                                                                              | and the second of                                                                         | 35       |

| 97.2.2.12.2 Wher                                                                                                                                                                                            | i generated                                                                               | 36<br>37 |

| The PCS generates                                                                                                                                                                                           | PMA PCS RX LPI STATUS.request messages to indicate a change in the rx lpi ac-             | 38       |

| _                                                                                                                                                                                                           | cribed in 97.3.2.3 and 97.3.6.2.2.                                                        | 39       |

|                                                                                                                                                                                                             |                                                                                           | 40       |

| 97.2.2.12.3 Effec                                                                                                                                                                                           | t of receipt                                                                              | 41       |

| The effect of receip                                                                                                                                                                                        | t of this primitive is specified in 97.3.6.4.                                             | 42<br>43 |

| -                                                                                                                                                                                                           | •                                                                                         | 44       |

| 97.2.2.13 PMA_P                                                                                                                                                                                             | CS_TX_LPI_STATUS.request                                                                  | 45       |

| When the DIIV aun                                                                                                                                                                                           | names the EEE conchility this primitive is concreted by the DCS transmit function to indi | 46       |

| When the PHY supports the EEE capability this primitive is generated by the PCS transmit function to indicate the status of the transmit link at the local PHY. The parameter PMA PCS TX LPI STATUS.request |                                                                                           | 47<br>48 |

|                                                                                                                                                                                                             | S transmit and PMA receive functions information regarding whether the transmit func-     | 49       |

| tion is in the LPI tra                                                                                                                                                                                      |                                                                                           | 50       |

| 1. 1 110                                                                                                                                                                                                    |                                                                                           | 51       |

| 97.2.2.13.1 Sema                                                                                                                                                                                            | intics of the primitive                                                                   | 52       |

|                                                                                                                                                                                                             | •                                                                                         | 53       |

PMA\_PCS\_TX\_LPI\_STATUS.request (tx\_lpi\_active)

The tx lpi active parameter can take on one of two values of the form:

TRUE The transmit function is in the LPI transmit mode.

FALSE The transmit function is not in the LPI transmit mode.

# 97.2.2.13.2 When generated

The PCS generates PMA\_PCS\_TX\_LPI\_STATUS.request messages to indicate a change in the tx\_lpi\_active variable as described in 97.3.5 and 97.3.6.2.2.

# **97.2.2.13.3 Effect of receipt**

The effect of receipt of this primitive is specified in 97.3.6.4.

# 97.3 Physical Coding Sublayer (PCS)

Editor's Note: Text written in italics are not approved baseline and are included only for placeholder information. The text will be change to match approved baseline when selected.

#### 97.3.1 PCS service interface (GMII)

The PCS service interface allows the 1000BASE-T1 PCS to transfer information to and from a PCS client. The PCS Interface is precisely defined as the Gigabit Media Independent Interface (GMII) in Clause 35.

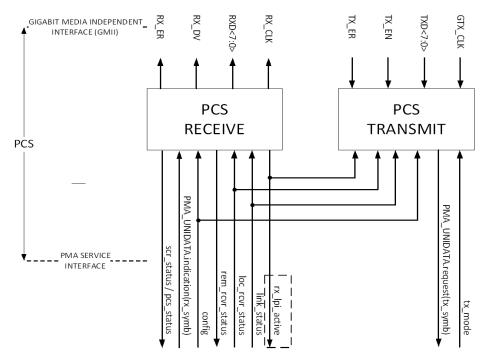

#### 97.3.2 PCS functions

The PCS comprises one PCS Reset function and two simultaneous and asynchronous operating functions. The PCS operating functions are: PCS Transmit and PCS Receive. All operating functions start immediately after the successful completion of the PCS Reset function.

The PCS reference diagram, Figure 97–4, shows how the two operating functions relate to the messages of the PCS-PMA interface. Connections from the management interface (signals MDC and MDIO) to other layers are pervasive and are not shown in Figure 97–4.

Figure 97-4—PCS reference diagram

#### 97.3.2.1 PCS Reset function

PCS Reset initializes all PCS functions. The PCS Reset function shall be executed whenever one of the following conditions occur:

- a) Power on.

- b) The receipt of a request for reset from the management entity.

PCS Reset sets pcs\_reset=ON while any of the above reset conditions hold true (see 97.3.6.2.2). All state diagrams take the open-ended pcs\_reset branch upon execution of PCS Reset. The reference diagrams do not explicitly show the PCS Reset function.

#### 97.3.2.2 PCS Transmit function

The PCS Transmit function shall conform to the PCS 80B/81B Transmit state diagram in Figure 97–14 and the PCS Transmit bit ordering in Figure 97–5 and Figure 97–7.

When communicating with the GMII, the PCS uses an octet-wide, synchronous data path, with packet delimiting being provided by transmit control signals and receive control signals. Alignment to 80B/81B blocks is performed in the PCS. The PMA sublayer operates independently of block and packet boundaries. The PCS provides the functions necessary to map packets between the GMII format and the PMA service interface format.

When the transmit channel is in data mode, the PCS Transmit process continuously generates 81B blocks based upon the TXD <7:0>, TX\_EN and TX\_ER signals on the GMII. The subsequent functions of the PCS Transmit process then pack the resulting blocks plus one OAM symbol, both of which are then processed by a Reed-Solomon (RS) encoder and subsequently 3B2T mapped into a transmit RS frame of PAM3 symbols.

Transmit data-units are sent to the PMA service interface via the PMA\_UNITDATA.request primitive. A symbol period, T, is 4/3 ns.

If a PMA\_TXMODE.indication message has the value SEND\_T, PCS Transmit generates sequences of codes defined in 97.3.4.2 to the PMA via the PMA\_UNITDATA.request primitive. These codes are used for training mode and only transmit the values {-1, +1}.

During training mode an InfoField is transmitted at regular intervals containing messages for startup operation. By this mechanism, a PHY indicates the status of its own receiver to the link partner. (See 97.4.2.5.)

In the data mode of operation, the PMA\_TXMODE.indication message has the value SEND\_N, and the PCS Transmit function uses an 81B-RS coding technique to generate at each symbol period code-groups that represent data or control. During transmission, 45 81B blocks shall be aggregated, encoded by a RS frame encoder, and then scrambled by a PCS scrambler. During data encoding PCS Transmit frames shall be encoded into a sequence of PAM3 symbols and transferred to the PMA.

Dashed rectangles in Figure 97–14 indicate states and state transitions in the transmit process state diagram that shall be supported by PHYs with the EEE capability. PHYs without the EEE capability do not support these transitions.

After reaching the data mode of operation, EEE-capable PHYs may enter the LPI transmit mode under the control of the MAC via the GMII. The EEE Transmit state diagram is contained within the PCS Transmit function. The EEE capability is described in 97.3.2.2.16.

#### 97.3.2.2.1 Use of blocks

The PCS maps GMII signals into 81-bit blocks inserted into an RS frame, and vice versa, using an 81B-RS coding scheme. The *PAM2* PMA training frame synchronization allows establishment of RS frame and 81B boundaries by the PCS Synchronization process. Blocks and frames are unobservable and have no meaning outside the PCS. The PCS functions ENCODE and DECODE generate, manipulate, and interpret blocks and frames as provided by the rules in 97.3.2.2.2.

#### 97.3.2.2.2 81B-RS transmission code

The PCS uses a transmission code to improve the transmission characteristics of information to be transferred across the link and to support transmission of control and data characters. The encoding defined by the transmission code ensures that sufficient information is present in the PHY bit stream to make clock recovery possible at the receiver. The encoding also preserves the likelihood of detecting any RS frame errors that may occur during transmission and reception of information. In addition, the code enables the receiver to achieve PCS synchronization alignment on the incoming PHY bit stream.

The relationship of block bit positions to GMII, PMA, and other PCS constructs is illustrated in Figure 97–5 for transmit and Figure 97–6 for receive. These figures illustrate the processing of a multiplicity of blocks containing 10 data octets. See 97.3.2.2.5 for information on how blocks containing control characters are mapped.

# 97.3.2.2.3 Notation conventions

For values shown as binary, the leftmost bit is the first transmitted bit.

80B/81B encodes 10 data octets or control characters into an 81B block.

Figure 97-5—PCS Transmit bit ordering

# 97.3.2.2.4 Transmission order

The PCS Transmit bit ordering shall conform to Figure 97–5 and Figure 97–7. Note that these figures show the mapping from GMII to 80B/81B block for a block containing ten data characters. The LSB of the OAM symbol is transmitted first.

#### 97.3.2.2.5 Block structure

Blocks consist of 81 bits. The first bit of a block is the data/ctrl header. Blocks are either data blocks or control blocks. The data/ctrl header is 0 for data blocks and 1 for control blocks. The remainder of the block contains the payload.

Data blocks contain ten data octets. Control blocks begin with a 5-bit pointer field that indicates the location of the first control code within the block. Bit 0 to 3 of pointer points to next octet that is a control symbol. Bit 4 of pointer indicates whether the next control symbol is the final control symbol of the block: 0 = final, 1 = more control symbols. If the first octet in the block is a control character, the pointer field is followed by a 3-bit control code. Otherwise the pointer field is followed by one or more data octets until the position of the first control code. Then the 3-bit control code indicates type of control character. The control code is followed by a 5-bit pointer field to the next control character if the prior pointer field value was greater than 15 (i.e. bit 4 = 1). The pointer field may be followed by a data octet or control code depending on the value of

Figure 97-6—PCS Receive bit ordering

the pointer field. In this way any combination of ten data octets and control characters may be encapsulated within an 81B block.

Figure 97-7—PCS detailed transmit bit ordering

The 81B block encoding is defined by the following equations where N = 10.

```

N = number of GMII octets encoded into block

octets numbered n = 0, 1, 2, ..., N-1 octet 0 is the first one presented on GMII.

TC[n] = 0 if octet n is data octet on GMII, 1 if octet n is control octet on GMII

TC[-1] = 1 by definition

TD[n][0:7] = GMII \text{ octet } n \text{ TXD}[0:7] \text{ if } TC[n] = 0

TD[n][5:7] = 000 \text{ or } 010 - IPG, 101 - LPI, 001 - TX Error if <math>TC[n] = 1. TD[n][0:4] is undefined.

B[0:8N] is the 8N+1 block. Bit 0 transmitted first.

OR(n) = Bitwise OR of TC[n:N-1]

NEXT(n)[0:3] = bit position of lowest bit in TC[n:N-1] that is a 1. Bit 3 is MSB.

NEXT(n)[4] = 0 if Bitwise SUM of TC[n:N-1] = 1, else 1

B[0] =

OR(0)

B[8n+1:8n+4] =

TD[n][0:3] - if OR(n) = 0

NEXT(n)[0:3] - if OR(n) = 1 AND TC[n-1] = 1

TD[n-1][3:6] - if OR(n) = 1 AND TC[n-1] = 0

TD[n][4] - if OR(n) = 0

B[8n+5] =

NEXT(n)[4] - if OR(n) = 1 AND TC[n-1] = 1

TD[n-1][7] - if OR(n) = 1 AND TC[n-1] = 0

B[8n+6:8n+8] =

TD[n][5:7] - if OR(n) = 0

TD[n][5:7] - if OR(n) = 1 AND TC[n] = 1

TD[n][0:2] - if OR(n) = 1 AND TC[n] = 0

```

# 97.3.2.2.6 Control codes

A subset of control characters defined at the GMII are supported by the 1000BASE-T1 PCS. When TX\_ER and TX\_EN are both asserted, the 1000BASE-T1 PCS conveys an Error symbol in the 80B81B block code. When TX\_EN is not asserted and no other supported control code is present at the GMII, the 1000BASE-T1 PCS will convey and Idle symbol in the 80B81B block code.

The control characters and their mappings to 1000BASE-T1 control code and GMII control code are specified in Table 97–1. All GMII and 1000BASE-T1 control code values that do not appear in the table shall not be transmitted and shall be treated as an error if received.

Table 97-1—GMII Control Code Mapping

| Control Code[0:2] | GMII Transmit                                 | GMII Receive                                  |

|-------------------|-----------------------------------------------|-----------------------------------------------|

| 000               | Normal Inter-Frame with loc_data_ready=NOT_OK | Normal Inter-Frame with rem data_ready=NOT_OK |

| 001               | Transmit Error<br>Propagation                 | Data Reception Error                          |

| 010               | Normal Inter-Frame with loc_data_ready=OK     | Normal Inter-Frame with rem_data_ready=OK     |

| 101               | Assert Low Power Idle                         | Assert Low Power Idle                         |

| other             | Reserved                                      | Reserved                                      |

The Carrier Extend and Carrier Extend Error, and Reserved transactions, if any occurred, are assigned to the Control Code 0:2 of 010, Normal inter-frame, in the PCS 80B/81B Encoder.

#### 97.3.2.2.7 Valid and invalid blocks

A block is invalid if any of the following conditions exists:

- a) The block contains an invalid pointer.

- b) Any control character contains a value not in Table 97–1.

- c) The RS frame containing this 80B/81B block is uncorrectable.

#### 97.3.2.2.8 Idle

Idle (Normal Inter-frame) control characters are transmitted when TX\_EN is not asserted and no other supported control code is present at the GMII. Idle characters may be added or deleted by the PCS to adapt between clock rates.

# 97.3.2.2.9 LP\_IDLE

The low power idle control characters (LP\_IDLEs) are transmitted when TX\_EN is not asserted, TX\_ER is asserted, and TXD<7:0> = 0x1. A continuous stream of LPI control characters is used to maintain a link in the LPI transmit mode. Idle control characters are used to transition from the LPI transmit mode to the normal mode. EEE compliant PHYs respond to the Assert Low Power Idle condition on the GMII using the procedure outlined in 97.1.2.4.

If EEE is not supported, then LP\_IDLE shall be converted to IDLE.

#### 97.3.2.2.10 Error

The Error control code is sent when TX\_ER and TX\_EN are both asserted. It is also sent when invalid blocks are received. Error allows physical sublayers such as the PCS to propagate received errors.

# 97.3.2.2.11 Transmit process

The transmit process generates blocks based upon the TXD<7:0>, TX\_EN and TX\_ER signals received from the GMII. Ten GMII data transfers are encoded into each block. It takes 2700 PMA\_UNITDATA transfers to send an RS frame of data. Where the GMII and PMA sublayer data rates are not synchronized to that ratio, the transmit process needs to insert idles, or delete idles to adapt between the rates.

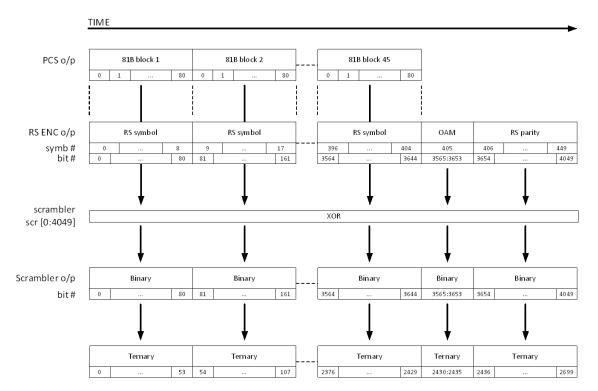

The transmit process generates blocks as specified in the transmit process state diagram. The contents of each block are contained in a vector tx\_coded<80:0>, which is aggregated with 45 81B blocks and OAM, then passed to the Reed Solomon FEC Encoder and then finally passed to the scrambler. tx\_coded<0> contains the data/ctrl header and the remainder of the bits contain the block payload.

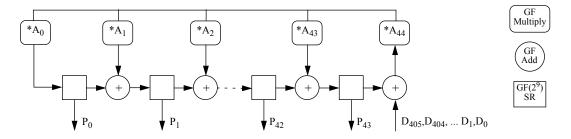

#### 97.3.2.2.12 RS encoder

The 1000BASE-T1 PCS shall encode the transmitted data stream using Reed-Solomon code (450,406). The RS encoder shall follow the notation described in 97.3.2.2.3 where the LSB is the first bit into the RS encoder and the first transmitted bit.

The FEC code used for 1000BASE-T1 links is a shortened Reed-Solomon (450,406) code over the Galois Field of GF(2<sup>9</sup>)—a code operating on 9 bit symbols, as shown in Figure 97–8. The code encodes 406 information symbols and adds 44 parity symbols. The code is systematic, meaning that the information symbols are not disturbed in any way in the encoder and the parity symbols are added separately to each block.

The code is based on the generating polynomial shown in Equation (97–1).

$$G(Z) = \prod_{i=0}^{43} (Z - \alpha^i) = A_{44} Z^{44} + A_{43} Z^{43} + \dots + A_0 Z^0$$

(97-1)

where

$\alpha$  is a root of the binary primitive polynomial  $x^9 + x^4 + 1$  and is represented as 0x002 A is a series representing the resulting polynomial coefficients of G(Z), ( $A_{44}$  is equal to 0x001)

Z corresponds to an 9 bit  $GF(2^9)$  symbol

x corresponds to a bit position in a  $GF(2^9)$  symbol

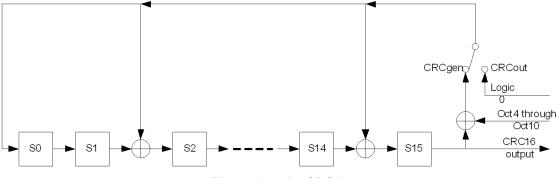

The parity calculation shall produce the same result as the shift register implementation shown in Figure 97–8. Before calculation begins, the shift register shall be initialized to zero. The contents of the shift register are transmitted without inversion.

Figure 97–8—Circuit for generating FEC parity vector

A FEC parity vector is represented by Equation (97–2).

$$P(Z) = D(Z) \bmod G(Z) \tag{97-2}$$

where

D(Z) is the data vector  $D(Z) = D_{405}Z^{449} + D_{404}Z^{448} + ... + D_0Z^{44}$ .  $D_{405}$  is the first 9-bit data symbol and  $D_0$  is the last.

P(Z) is the parity vector  $P(Z) = P_{43}Z^{43} + P_{42}Z^{42} \dots + P_0Z^0 \cdot P_{43}$  is the first 9-bit parity symbol and  $P_0$  is the last

A data symbol  $(d_8, d_7, ..., d_1, d_0)$  is identified with the element:  $d_8\alpha^8 + d_7\alpha^7 + ... + d_1\alpha^1 + d_0$  in GF(2<sup>9</sup>), the finite field with 2<sup>9</sup> elements. The code has a correction capability of up to twenty-two symbols.

The  $d_0$  is identified as the LSB and  $d_8$  is identified as the MSB for all symbols.

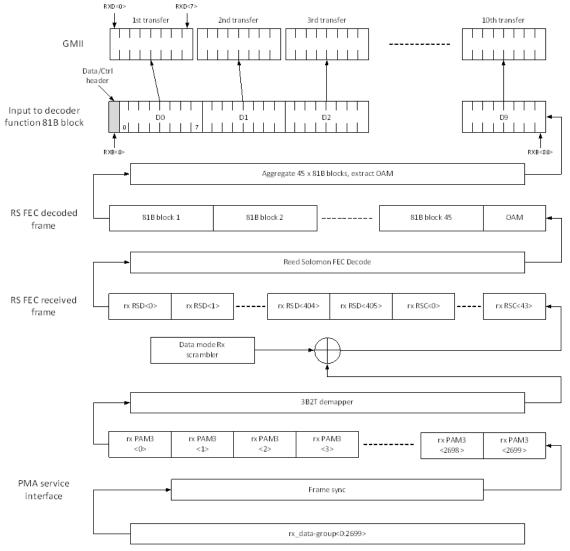

The resulting payload of scrambled 45 81B blocks, followed by the OAM symbol results in a total payload of 3654 bits. The resulting RS block size is 450 9-bit symbols, a total of 4050 bits. Figure 97–9 shows the bit mapping between PCS and FEC.

Figure 97-9—PCS to FEC bit mapping

#### 97.3.2.2.13 PCS scrambler

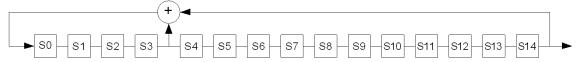

The PCS Transmit function employs side-stream scrambling. The scrambler for the MASTER shall produce the same result as the implementation shown in Figure 97–10. This implements the scrambler polynomial:

$$G(x) = 1 + x^4 + x^{15} (97-3)$$

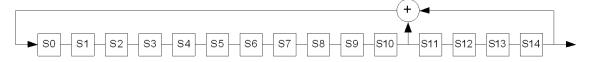

The scrambler for the SLAVE shall produce the same result as the implementation shown in Figure 97–10. This implements the scrambler polynomial:

$$G(x) = 1 + x^{11} + x^{15} (97-4)$$

The initial seed values for the MASTER and SLAVE scramblers are left to the implementor. The seed values shall be non-zero and shall be transmitted during the InfoField exchange. (See 97.4.2.5.5). The scrambler is run continuously on all RS frame output bits.

#### PCS scrambler employed by the MASTER

#### PCS scrambler employed by the SLAVE

Figure 97-10-MASTER and SLAVE PCS scramblers

# 97.3.2.2.14 3B2T to PAM3

The 3B2T mapper generates 2700 PAM3 symbols per RS frame that are sent to the PMA via PMA\_UNIT-DATA.request. Every 9-bit symbol is divided into three 3-bit groups with the LSB bits as the first group. Each 3-bit group is then mapped by the 3B2T into 2 PAM3 symbols. The mapping of 3B2T to PAM3 is illustrated in Table 97–2. B[0] is the LSB and T[0] is the first PAM3 symbol transmitted.

<sup>&</sup>lt;sup>1</sup>The convention here, which considers the most recent bit into the scrambler to be the lowest order term, is consistent with most references and with other scramblers shown in this standard. Some references consider the most recent bit into the scrambler to be the highest order term and would therefore identify this as the inverse of the polynomial in Equation (97–3). In case of doubt, note that the conformance requirement is based on the representation of the scrambler in the figure rather than the polynomial equation.

# Table 97–2—3B2T Mapping to PAM3

| B[2], B[1], B[0] | T[1], T[0] |

|------------------|------------|

| 000              | -1,-1      |

| 001              | 0,-1       |

| 010              | -1,0       |

| 011              | -1,+1      |

| 100              | +1,0       |

| 101              | +1,-1      |

| 110              | +1,+1      |

| 111              | 0,+1       |

#### 97.3.2.2.15 81B-RS framer

The 81B-RS framer adapts between the 81-bit width of the 81B blocks and the PAM3 input to the PMA. When the transmit channel is operating in data mode, the 81B-RS sends one PAM3 symbol of transmit data at a time via PMA UNITDATA.request primitives. The PMA UNITDATA.request primitives are fully packed with bits.

# 97.3.2.2.16 EEE capability

The optional 1000BASE-T1 EEE capability allows compliant PHYs to transition to an LPI mode of operation when link utilization is low. EEE compliant PHYs shall implement the transmit state diagram including the EEE portion, noted by dotted lines in Figure 97–14, within the PCS.

When there is an Assert Low Power Idle while in the SEND DATA state the PHY transmits the sleep signal to indicate to the link partner that it is transitioning to the SEND LPI state. The sleep signal is one RS frame composed entirely of LP IDLE characters. If the LP IDLE character occurs in the last 80B/81B block then the sleep signal is the next RS frame. The PHY shall transmit no RS frames partially filled with LP IDLES.

Following the transmission of the sleep signal, quiet-refresh signaling begins, as described in 97.3.5.

While the PMA asserts SEND N, the lpi tx mode variable shall control the transmit signal through the PMA UNITDATA.request primitive described as follows:

When the PMA TXMODE indication message does not have the value of SEND N, the lpi tx mode variable is ignored.

When the lpi tx mode variable takes the value NORMAL the PCS passes coded data to the PMA via the PMA UNITDATA.request primitive.

When the lpi tx mode variable takes the value QUIET the PCS passes zeros to the PMA through the PMA UNITDATA.request primitive.

When the lpi\_tx\_mode variable takes the value REFRESH, the PCS passes zero data encoded through PCS data path to the PMA via the PMA UNITDATA.request primitive.

The quiet-refresh cycle is repeated until Assert Low Power Idle is not detected at the GMII. This indicates that the local system is requesting a transition back to the normal power mode. At the next RS frame the PCS transmits a wake frame composed of an entire RS frame containing only Idle. The wake frame shall be sent only during alternating RS frame counts.

Due to the wake signal constrained to occur at the beginning of every second RS frame boundary the PHY wake time may range from 3.6  $\mu$ s to 10.8  $\mu$ s (lpi\_wake\_timer= $T_{w\ phy}$  as defined by Clause 78).

#### 97.3.2.3 PCS Receive function

The PCS Receive function shall conform to the PCS 80B/81B receive state diagram in Figure 97–15 and the PCS Receive bit ordering in Figure 97–6 including compliance with the associated state variables as specified in 97.3.6.

The PCS Receive function accepts received code-groups provided by the PMA Receive function via the parameter rx\_symb. The PCS receiver uses knowledge of the PMA training alignment to correctly align the 81B-RS frames. The received 81B-RS frames are decoded with error correction; the framing is checked; and the 80B/81B ordered sets are converted to 10 data octets to obtain the signals RXD<7:0>, RX\_DV and RX ER for transmission to the GMII.

During PMA training mode, PCS Receive checks the received PAM2 framing and signals the reliable acquisition of the descrambler state by setting the parameter scr\_status to OK.

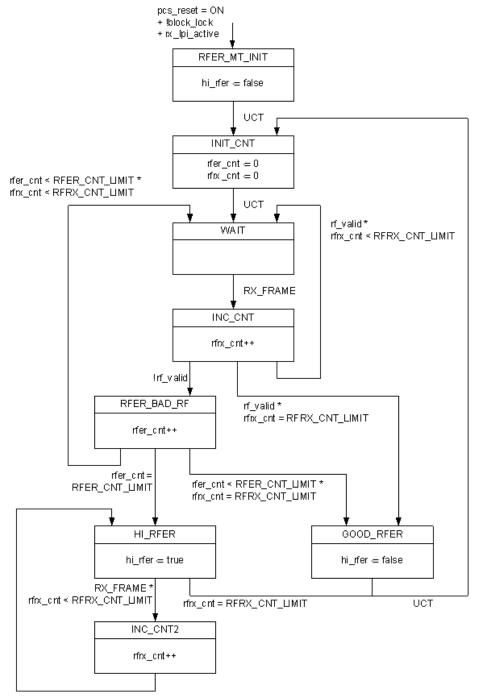

When the PCS Synchronization process has obtained synchronization, the RS frame error rate (RFER) monitor process monitors the signal quality asserting hi\_rfer if excessive RS frame errors are detected (RS parity error). If 40 consecutive RS frame errors are detected, the block\_lock flag is de-asserted. When block\_lock is asserted and hi\_rfer is de-asserted, the PCS Receive process continuously accepts blocks. The PCS Receive process monitors these blocks and generates RXD<7:0>, RX\_DV and RX\_ER for transmission to the GMII.

When the receive channel is in training mode, the PCS Synchronization process continuously monitors PMA\_RXSTATUS.indication (loc\_rcvr\_status). When loc\_rcvr\_status indicates OK, then the PCS Synchronization process accepts data-units via the PMA\_UNITDATA.request primitive. It attains frame and block synchronization based on the PMA training frames and conveys received blocks to the PCS Receive process. The PCS Synchronization process sets the block\_lock flag to indicate whether the PCS has obtained synchronization. The PMA training sequence includes 1 bit pattern every 180 PAM2 symbols, which is aligned with the PCS Partial RS frame boundary, as well as an InfoField which is inserted in the 15th PCS Partial RS frame. When the PCS Synchronization process is synchronized to the RS frame boundary using this pattern, block lock is asserted.

PHYs with the EEE capability support transition to the LPI mode when the PHY has successfully completed training. Transitions to and from the LPI mode are allowed to occur independently in the transmit and receive functions. The PCS receive function is responsible for detecting transitions to and from the LPI receive mode and indicating these transitions using signals defined in 97.3.6.

The link partner signals a transition to the LPI mode of operation by transmitting one frame composed entirely of 80B/81B blocks of LP\_IDLES. When blocks of LP\_IDLES are detected at the output of the 80B/81B decoder, rx\_lpi\_active is asserted by the PCS receive function and the LPI character is continuously asserted at the receive GMII. After the sleep frame the link partner begins transmitting zeros, and it is recommended that the receiver power down receive circuits to reduce power consumption. The receive function uses RS frame counters to maintain synchronization with the remote PHY and receives periodic refresh signals that are used to update coefficients, so that the integrity of adaptive filters and timing loops in the PMA is maintained. LPI signaling is defined in 97.3.5. The quiet-refresh cycle continues until the PHY detects the wake frame. The PHY receive function sends Idles to the GMII for the remainder of the wake frame and then resumes normal power mode operation.

# 97.3.2.3.1 Frame and block synchronization

When the receive channel is operating in data mode, the frame and block synchronization function receives data via PAM3 PMA UNITDATA indication primitive. It shall form a PAM3 stream from the primitive by concatenating requests in order from rx data<0> to rx data<2699> (see Figure 97–6). It obtains block lock to the RS frames during the PAM2 training pattern using synchronization bits provided in the training sequence.

#### 97.3.2.3.2 PCS descrambler

The descrambler processes the payload to reverse the effect of the scrambler using the same polynomial. The PHY shall descramble the data stream and return the proper sequence of code-groups to the decoding process for generation of RXD<7:0> to the GMII. For side-stream descrambling, the MASTER PHY shall employ the receiver descrambler generator polynomial per Equation (97-4) and the SLAVE PHY shall employ the receiver descrambler generator polynomial per Equation (97–3).

# 97.3.3 Test-pattern generators

The test-pattern generator mode is provided for enabling joint testing of the local transmitter, the channel and remote receiver. When the transmit PCS is operating in test-pattern mode it shall transmit continuously as illustrated in Figure 97–5, with the input to the scrambler set to zero and the initial condition of the scrambler set to any non-zero value. When the receiver PCS is operating in test-pattern mode it shall receive continuously as illustrated in Figure 97-6. The output of the received descrambled values should be zero. Any nonzero values correspond to receiver bit errors. This mode is further described as test mode 7 in 97.5.2.

# 97.3.4 PMA training side-stream scrambler polynomials

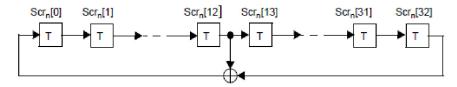

The PCS Transmit function employs side-stream scrambling. If the parameter config provided to the PCS by the PMA PHY Control function via the PMA CONFIG.indication message assumes the value MASTER, PCS Transmit shall employ Equation (97–5).

$$g_M(x) = 1 + x^{13} + x^{33} (97-5)$$

as transmitter side-stream scrambler generator polynomial. If the PMA CONFIG.indication message assumes the value of SLAVE, PCS Transmit shall employ Equation (97–6).

$$g_S(x) = 1 + x^{20} + x^{33} (97-6)$$

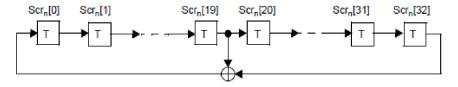

as transmitter side-stream scrambler generator polynomial. An implementation of master and slave PHY side-stream scramblers by linear-feedback shift registers is shown in Figure 97–10. The bits stored in the shift register delay line at time n are denoted by Scr<sub>n</sub>[32:0]. At each symbol period, the shift register is advanced by one bit, and one new bit represented by  $Scr_n[0]$  is generated. The transmitter side-stream scrambler is reset upon execution of the PCS Reset function. If PCS Reset is executed, all bits of the 33-bit

vector representing the side-stream scrambler state are arbitrarily set. The initialization of the scrambler state is left to the implementer. In no case shall the scrambler state be initialized to all zeros.

Side-stream scrambler employed by the MASTER PHY

Side-stream scrambler employed by the SLAVE PHY

Figure 97–11—A realization of side-stream scramblers by linear feedback shift registers

# 97.3.4.1 Generation of $S_n$

During PMA training, the training pattern is embedded with indicators to establish alignment to the RS FEC block and the 15 partial frames that comprise the block. The last partial frame is embedded with an information field used to exchange messages between link partners. PMA training signal encoding is based on the generation, at time n, of the bit S<sub>n</sub>. The first bit is inverted in the first 14 partial frames of each RS FEC block. The first 96 bits of the 15th partial frame is XOR'd with the contents of the Infofield.

$$S_{n} = \begin{cases} Scr_{n}[0] \oplus 1 Infofield_{(nmod180)} 2519 < (nmod2700) < 2616 \\ Scr_{n}[0] \oplus 1 & (nmod180) = 0 \\ Scr_{n}[0] & otherwise \end{cases}$$

(97-7)

# 97.3.4.2 Generation of symbol $T_n$

The bit  $S_n$  is mapped to the transmit symbol  $T_n$  as follows: if  $S_n = 0$  then  $T_n = +1$ , if  $S_n = 1$  then  $T_n = -1$ .

#### 97.3.4.3 PMA training mode descrambler polynomials

The PHY shall acquire descrambler state synchronization to the PAM2 training sequence and report success through scr\_status. For side-stream descrambling, the MASTER PHY shall employ the receiver descrambler generator polynomial same as Equation (97–6) and the SLAVE PHY shall employ the receiver descrambler generator polynomial same as Equation (97–5).

#### 97.3.5 LPI signaling

PHYs with EEE capability have transmit and receive functions that can enter and leave the LPI mode independently. The PHY can transition to the LPI mode when the PHY has successfully completed training. The transmit function of the PHY initiates a transition to the LPI transmit mode when it generates a sleep signal composed of 80B/81B blocks containing only LPI control characters, as described in 97.3.2.2.16.

When the transmitter begins to send the sleep signal, it asserts tx\_lpi\_active and the transmit function enters the LPI transmit mode.

Within the LPI mode PHYs use a repeating quiet-refresh cycle (see Figure 97–12). The first part of this cycle is known as the quiet period and lasts for a time lpi\_quiet\_time equal to 354 partial RS frame periods. The quiet period is defined in 97.3.5.2. The second part of this cycle is known as the refresh period and lasts for a time lpi\_refresh\_time equal to 6 partial RS frame periods. The refresh period is defined in 97.3.5.3. A cycle composed of one quiet period and one refresh period is known as an LPI cycle and lasts for an lpi qr time equal to 24\*15 = 360 partial RS frame periods.

lpi\_offset, lpi\_quiet\_time, lpi\_refresh\_time, and lpi\_qr\_time are timing parameters that are integer multiples of the partial RS frame period. lpi\_offset is a fixed value equal to lpi\_qr\_time/2 + 15. It is used to ensure refresh signals and wake start times are appropriately offset by the link partners.

Figure 97-12—LPI signal timing

PHYs begin the transition from the LPI receive mode when they detect the wake frame.

#### 97.3.5.1 LPI Synchronization

To maximize power savings, maintain link integrity, and ensure interoperability, EEE-capable PHYs must synchronize refresh intervals during the LPI mode. The quiet-refresh cycle is established from the Master Partial Frame Count (PFC24) during PMA Training. At the master, partial frame zero and all multiples of 360 partial frames thereafter denote the start of the cycle.

An EEE-capable PHY in slave mode is responsible for synchronizing its partial frame count to the master's partial frame count during link up. The slave shall ensure that its partial frame count is synchronized to the master's partial frames within 1 partial frame. The start of the slave quiet-refresh cycle is delayed from the master by 13 frames (195 partial frames). This offset ensures that the master and slave wake/sense windows are offset from each other and that the refresh periods are nearly a half cycle offset.

Following the transition to PAM3, the PCS continues to count transmitted partial RS frames (tx\_pfc), and uses the counter to generate refresh and wake control signals for the transmit functions.

Wake frames may be sent at the beginning of every second RS frame boundary starting at the beginning of the refresh RS frame. This sets wake\_period to 30 partial RS frames. The master and slave allowable wake positions do not overlap. The wake frame may start in the same RS frame as a planned refresh and obviate this refresh.

The master and slave shall derive the refresh\_active and wake\_start signals from the transmitted partial RS frames (tx\_pfc) as shown in Table 97-3 and Table 97-4.

Table 97–3—Synchronization logic derived from slave signal partial RS frame count

| Slave-side Variable    | u = tx_pfc                                                       |

|------------------------|------------------------------------------------------------------|

| tx_refresh_active=true | lpi_offset – lpi_refresh_time ≤ mod(u, lpi_qr_time) < lpi_offset |

| tx_wake_start=true     | mod(u, wake_period) = 0                                          |

# Table 97-4—Synchronization logic derived from master signal partial RS frame count

| Master-side variable   | v = tx_pfc                           |

|------------------------|--------------------------------------|

| tx_refresh_active=true | mod(v, lpi_qr_time) ≥ lpi_quiet_time |

| tx_wake_start=true     | mod(v, wake_period) = wake_period/2  |

# 97.3.5.2 Quiet period signaling

During the quiet period the transmitter shall put zeros on to the MDI. During the quiet period the transmitter and may be turned off to save power.

# 97.3.5.3 Refresh period signaling

During the LPI mode 1000BASE-T1 PHYs use staggered, out-of-phase refresh signaling to maximize power savings. PAM3 refresh symbols are generated from the output of the data mode PCS side-stream scrambler polynomials described in 97.3.2.2.13 with PCS transmit data masked to zero. The scramblers run continuously regardless of the transmit mode. The refresh occupies the last 6 partial RS frames of where the RS frame would occur if it were transmitted.

The OAM symbol and its associated parity symbols are XOR'ed with the scrambler stream at the same relative position to the RS boundaries as they occupy during normal power mode. The parity is generated using Equation (97–2) with  $D_{405}$  ...  $D_1 = 0$  and  $D_0 = OAM$ .

# 97.3.6 Detailed functions and state diagrams

# 97.3.6.1 State diagram conventions

The body of this subclause is comprised of state diagrams, including the associated definitions of variables, constants, and functions. Should there be a discrepancy between a state diagram and descriptive text, the state diagram prevails.

The notation used in the state diagrams follows the conventions of 21.5. State diagram timers follow the conventions of 14.2.3.2. The notation ++ after a counter or integer variable indicates that its value is to be incremented.

| 97.3.6.2 State diagram parameters                                                                 | 1   |

|---------------------------------------------------------------------------------------------------|-----|

| 97.3.6.2.1 Constants                                                                              | 2 3 |

| EDLOCK B (00.0)                                                                                   | 4   |

| EBLOCK_R<99:0>                                                                                    | 5   |