### Comment (Clause 33.2.5.9 Page 66 line 39) Jean address it

The variable class\_4PID\_mult\_events\_sec is used in figure 33-21 (Figure 33-21 - Type 3 and Type 4 PSE dual-signature classification state diagram on the <u>Primary Secondary</u> Alternative) but is not defined.

[notes:

- 1. The typo Secondary instead of Primary is addressed in another comment

- 2. The variable class\_4PID\_mult\_events\_sec is missing also in the updated SM in Picard\_03\_0116.pdf]

### Suggested Remedy

# Add at line 39 the following Text:

class\_4PID\_mult\_events\_sec

A variable indicating if the PSE uses the method consisting in generating 3 class events to determine if the dual signature PD is a candidate for 4-pair power. Values:

FALSE: the PSE does not need to generate 3 class events to determine if the PD is a candidate for 4-pair power.

TRUE: the PSE generates at least 3 class events to determine if the PD is a candidate for 4-pair power.

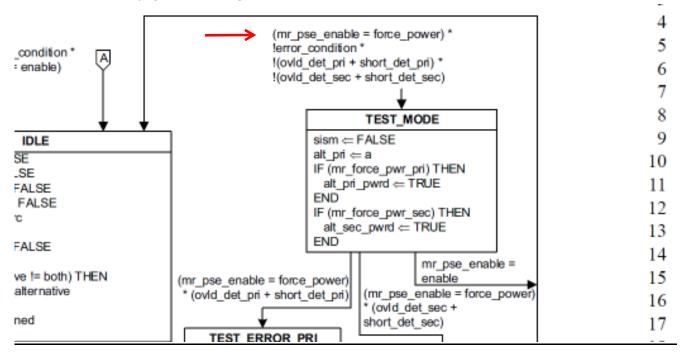

#### Comment (33.2.5.11 page 78 line 7, Figure 33-15)

The input to TEST\_MODE is incorrect since it is not allow to test each pairset individually. In addition, overload is optional.

(mr\_pse\_enable = force\_power) \*!error\_condition \*!(ovld\_det\_pri + short\_det\_pri) \*!(ovld\_det\_sec + short\_det\_sec)

#### Suggested Remedy.

(mr\_pse\_enable = force\_power) \*!error\_condition \*[!(ovld\_det\_pri + short\_det\_pri) + !(ovld\_det\_sec + short\_det\_sec)] [The issue of overload is optional is addressed in separate comment.]

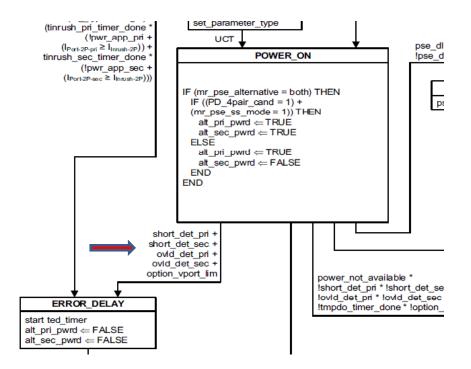

# <u>Comment (clause 33.2.5.12, page 80 line 34</u>, Figure 33-15) [Updates to comment #202]

In the exit from **POWER\_ON to ERROR\_DELAY** Turning off the power due to overload is optional and not mandatory. According to the state machine it is mandatory.

The current text is: short\_det\_pri + short\_det\_sec + ovld\_det\_pri + ovld\_det\_sec + option\_vport\_lim

# Suggested Remedy:

# Task force to discuss the following 3 options:

# Option 1:

[If we remove: + ovld\_det\_pri + ovld\_det\_sec it will fix the problem. The text outside the state machine (in 33.2.8.6 Overload current) allows shutting of the power in case of overload"

So if state machine have the priority to set the requirements, the text will clarify the optional features.

The same is correct for legacy state machine in Figure 33-13 page 63 line 51]

1. Change the text to:

short\_det\_pri + short\_det\_sec + option\_vport\_lim

# [Consider to apply the concept of this option for Type 1 and 2 SM. ]

- 2. Apply the same solution to legacy state machine in Figure 33-13 page 63 line 51:

- Change to: short\_detected+ option\_vport\_lim

[it doesn't considered changing legacy since the feature is optional]

PSE and PD state machine comments and baseline. Rev 001

# Option 2:

1. To add to the list of Type 3, 4 variables the variables option\_ovld\_pri and option\_ovld\_sec with the following values:

# option\_ovld\_pri

A variable that controls the circuitry that the PSE Primary Alternative uses to go to ERROR\_DELAY state in case of overload conditions.

Values: FALSE: The PSE is not turning off the Primary Alternative under overload conditions.

TRUE: The PSE is turning off the Primary Alternative under overload conditions.

# option\_ovld\_sec

A variable that controls the circuitry that the PSE Secondary Alternative uses to go to ERROR\_DELAY in case of overload conditions.

Values: FALSE: The PSE is not turning off the Secondary Alternative under overload conditions. TRUE: The PSE is turning off the Secondary Alternative under overload conditions.

1.1 Change the list of conditions to:

short\_det\_pri + short\_det\_sec + option\_ovld\_pri\*ovld\_det\_pri + option\_ ovld \_sec \*ovld\_det\_sec +

option\_vport\_lim

# [Consider to apply the concept of this option for Type 1 and 2 SM. ]

2. Update the legacy state machine in Figure 33-13 page 63 line 51:

2.1 To add to the list of Type 1, 2 variables the variable option\_ovld with the following values:

option\_ovld A variable that controls the circuitry that the PSE uses to go to ERROR\_DELAY state in case of overload conditions.

Values: FALSE: The PSE is not turning off the power under overload conditions.

TRUE: The PSE is turning off the power under overload conditions.

2.2 Change the list of conditions to:

short\_detected+ option\_ovId \*ovId\_detected + option\_vport\_lim

# Option 3:

To keep the state machine as it is and to add the following text at the beginning of the state machine clause:

"State machine has priority over text unless a waver is explicitly specified." or equivalent wording. [This will allow simplifications of state machine description in many cases including PD section.]

#### Comment (33.2.5.12, page 85 line 22, Figure 33-19):

#### [Updates to comment #200]

### [This comment addresses comment #181 as well.]

The objective of this comment is to allow PSE to do class reset any time within Tpon to generate 1<sup>st</sup> classification sequence to do some testing such:

- a) Checking unbalance with classification voltage

- b) In addition to other ways to know if single-signature PD is 4-pairs capable i.e. the 4PID check, we can positively know it by finding the PD class code by generating 3 classifications events and if there just power for Type 1 the PSE can redo classification by issuing one class event.

Allowing doing class reset during Tpon doesn't supported in Figure 33-19 as it does in dual-signature classification state diagram in figures 33-20 and 33-21.

In addition, there is a need to allow generate 1 class event if PSE knows that the power available in Type 1 without the need to know what is the PD requested power.

The above was meant to increase PSE design flexibility.

#### Suggested Remedy:

To add the following text to classification section page 97 line 30:

"PSE is allowed to reset the PD classification during class event sequence and redo its classification sequence at any time between the end of detection and POWER\_UP time duration (Tpon) without redoing connection check and detection."

or equivalent wording.

#### To add the following Editor Notes:

"Editor Note: To add in Figure 33-19 the ability to reset classification after at least 1 classification events with long first class event or with short first class event without doing connection check and detection again when Tpon is still not done."

"Editor Note: To add in Figure 33-19 the ability generate 1 class event if PSE knows that the power available is Type 1 without the need to know what is the PD requested power."

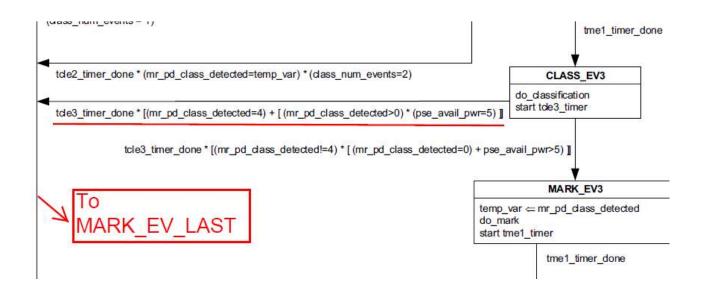

#### Comment (33.2.5.12, page 85 line 22, Figure 33-15)

In the exit from CLASS\_EV3 to MARK\_EV\_LAST:

tcle3\_timer\_done \* [(mr\_pd\_class\_detected=4) + [ (mr\_pd\_class\_detected>0) \* (pse\_avail\_pwr=5) ]]

The statement is true if:

- a) tcle3\_timer\_done \*(mr\_pd\_class\_detected=4) +

- b) tcle3\_timer\_done \*(mr\_pd\_class\_detected>0) \* (pse\_avail\_pwr=5)

According to Table 33-11, for pse\_avail\_pwr=5, the number of classification events is 4 and this exist is coming from CLASS\_EV3.

The suggested fix is:

The statement is true if:

tcle3\_timer\_done \*(mr\_pd\_class\_detected=4) +

tcle3\_timer\_done \*(mr\_pd\_class\_detected>0) \* (pse\_avail\_pwr=4)

Suggested Remedy

tcle3\_timer\_done \*(mr\_pd\_class\_detected=4) +

tcle3\_timer\_done \*(mr\_pd\_class\_detected>0) \* (pse\_avail\_pwr= 4)=

=tcle3\_timer\_done \* [(mr\_pd\_class\_detected=4) + [ (mr\_pd\_class\_detected>0) \* (pse\_avail\_pwr=4) ]]

PSE and PD state machine comments and baseline. Rev 001

Page 6 of 8

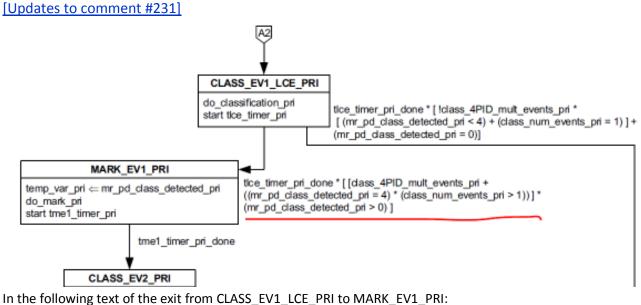

### Comment (clause 33.2.5.12, page 86 line 10, , Figure 33-20)

tice\_timer\_pri\_done \* [ [class\_4PID\_mult\_events\_pri +((mr\_pd\_class\_detected\_pri = 4) \* (class\_num\_events\_pri > 1)) ]

\*(mr\_pd\_class\_detected\_pri > 0) ]

The conditions are true if:

- a) tlce\_timer\_pri\_done \* class\_4PID\_mult\_events\_pri \*(mr\_pd\_class\_detected\_pri > 0) which means tlce timer is done and PSE uses 3 class event for 4PID and it has to be true when the first class signature>0 since it is dual-signature PD that starts with class signature 1 to 5.

- b) tlce\_timer\_pri\_done \*((mr\_pd\_class\_detected\_pri = 4) \* (class\_num\_events\_pri > 1)) \*(mr\_pd\_class\_detected\_pri > 0)

There are 2 issues:

1. Redundant round parenthesis in the part: +((mr\_pd\_class\_detected\_pri = 4) \* (class\_num\_events\_pri > 1)) 2. Why in part (b) we need (mr\_pd\_class\_detected\_pri > 0) if we have (mr\_pd\_class\_detected\_pri = 4).

#### Suggested Remedy:

Change from:

tlce\_timer\_pri\_done \* [ [class\_4PID\_mult\_events\_pri +( (mr\_pd\_class\_detected\_pri = 4) \*

(class\_num\_events\_pri > 1)) ] \*(mr\_pd\_class\_detected\_pri > 0) ]

To:

tlce\_timer\_pri\_done \* class\_4PID\_mult\_events\_pri \*(mr\_pd\_class\_detected\_pri > 0)+

tlce\_timer\_pri\_done \*(mr\_pd\_class\_detected\_pri = 4) \* (class\_num\_events\_pri > 1) =

= tlce\_timer\_pri\_done\*

[class\_4PID\_mult\_events\_pri \*(mr\_pd\_class\_detected\_pri > 0) +(mr\_pd\_class\_detected\_pri =

4)\*(class\_num\_events\_pri > 1)]

PSE and PD state machine comments and baseline. Rev 001

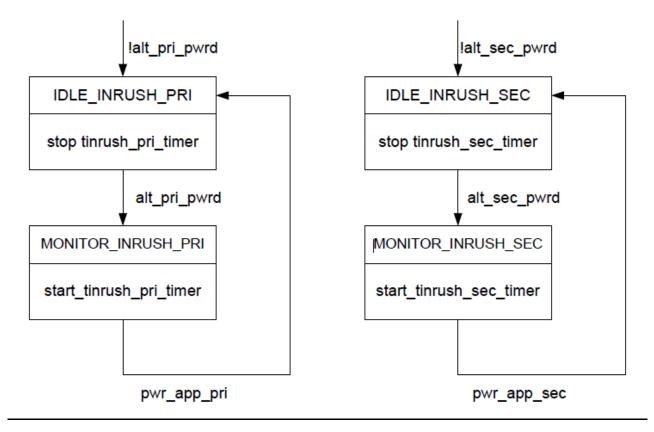

#### Comment (clause 33.2.5.12, page 88 line 25, Figure 33-23)

### [Comment #229]

See darshan\_08\_0316.pdf for new Figure 33-23.

Figure 33–23—Type 3 and Type 4 inrush monitor state diagram does not reflect the case where POWER\_UP for ALT A and ALT B may be done in different time and not simultaneously.

#### Suggested Remedy:

Replace Figure 33–23 as proposed in darshan\_08\_0316.pdf for new Figure 33-23.