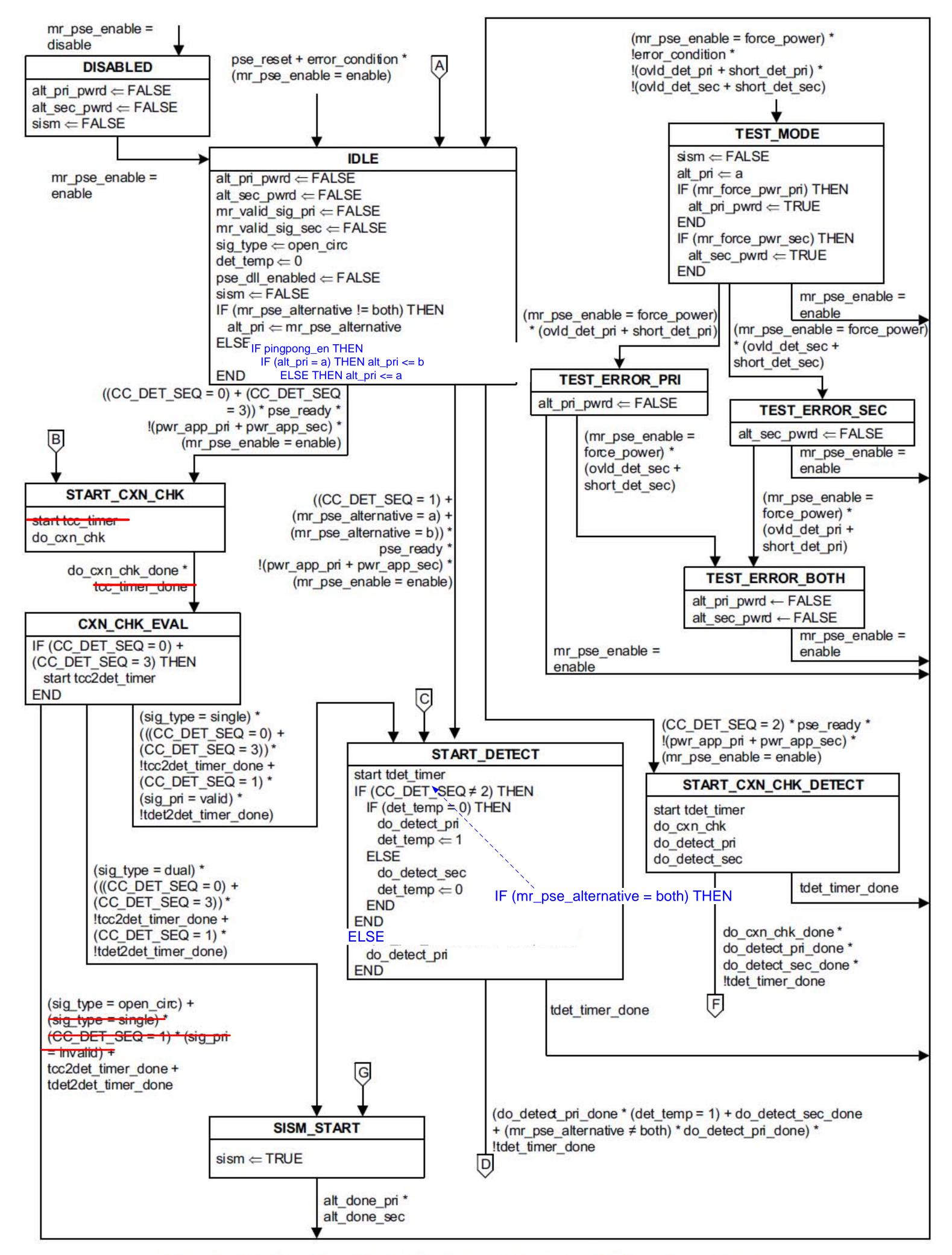

Figure 33–15—Type 3 and Type 4 top level PSE state diagram

# (mr\_pse\_alternative = both) \* ((det\_temp = 1)\*(sig\_pri ≠ valid) + (det\_temp = 0)\*(sig\_sec ≠ valid) + ((CC\_DET\_SEQ = 0)+(CC\_DET\_SEQ = 3)\*(det\_temp = 1)\*tdet2det\_timer\_done)) + (mr\_pse\_alternative ≠ both)\*(sig\_pri ≠ valid)

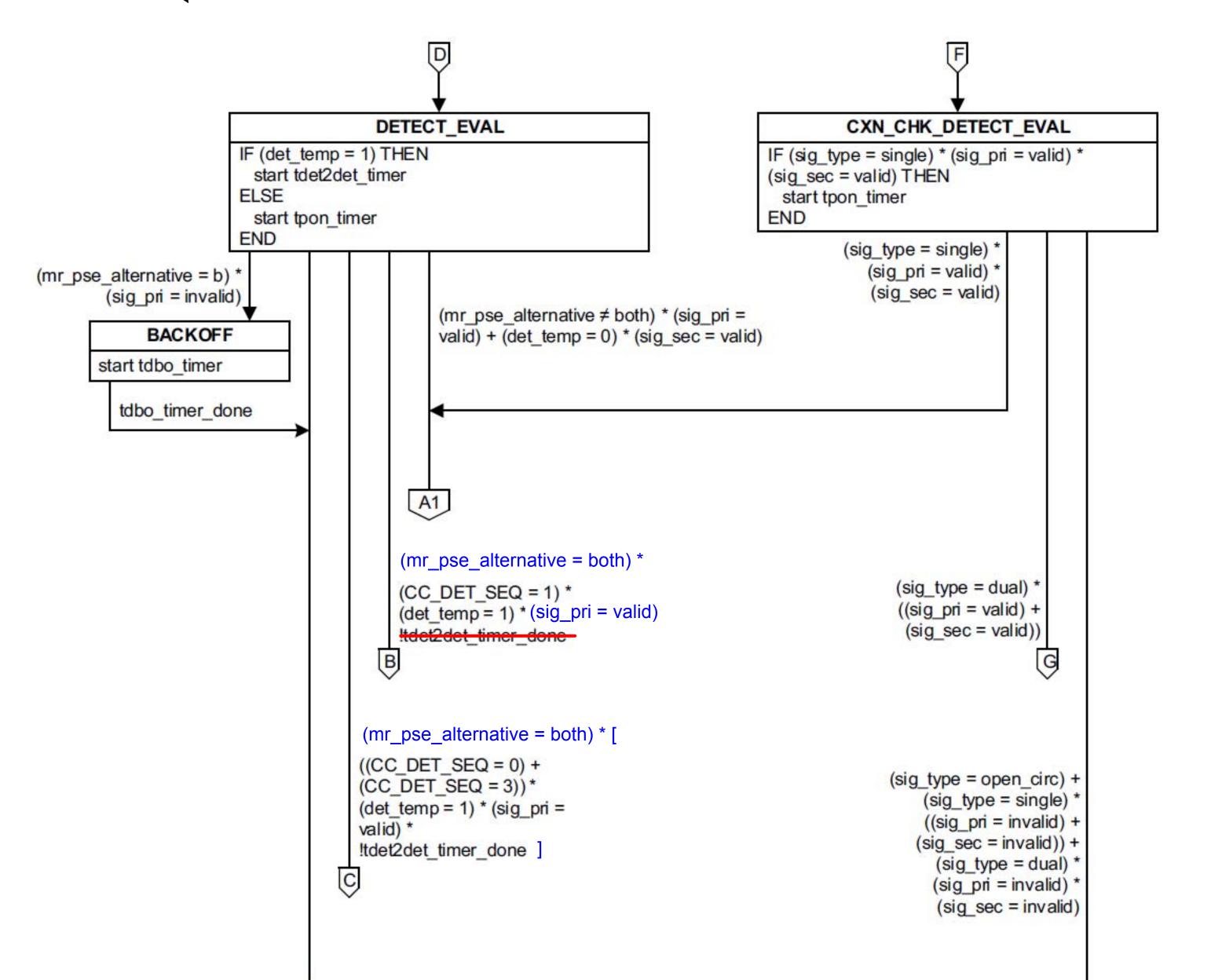

### Figure 33–15—Type 3 and Type 4 top level PSE state diagram (continued)

Figure 33–15—Type 3 and Type 4 top level PSE state diagram (continued)

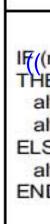

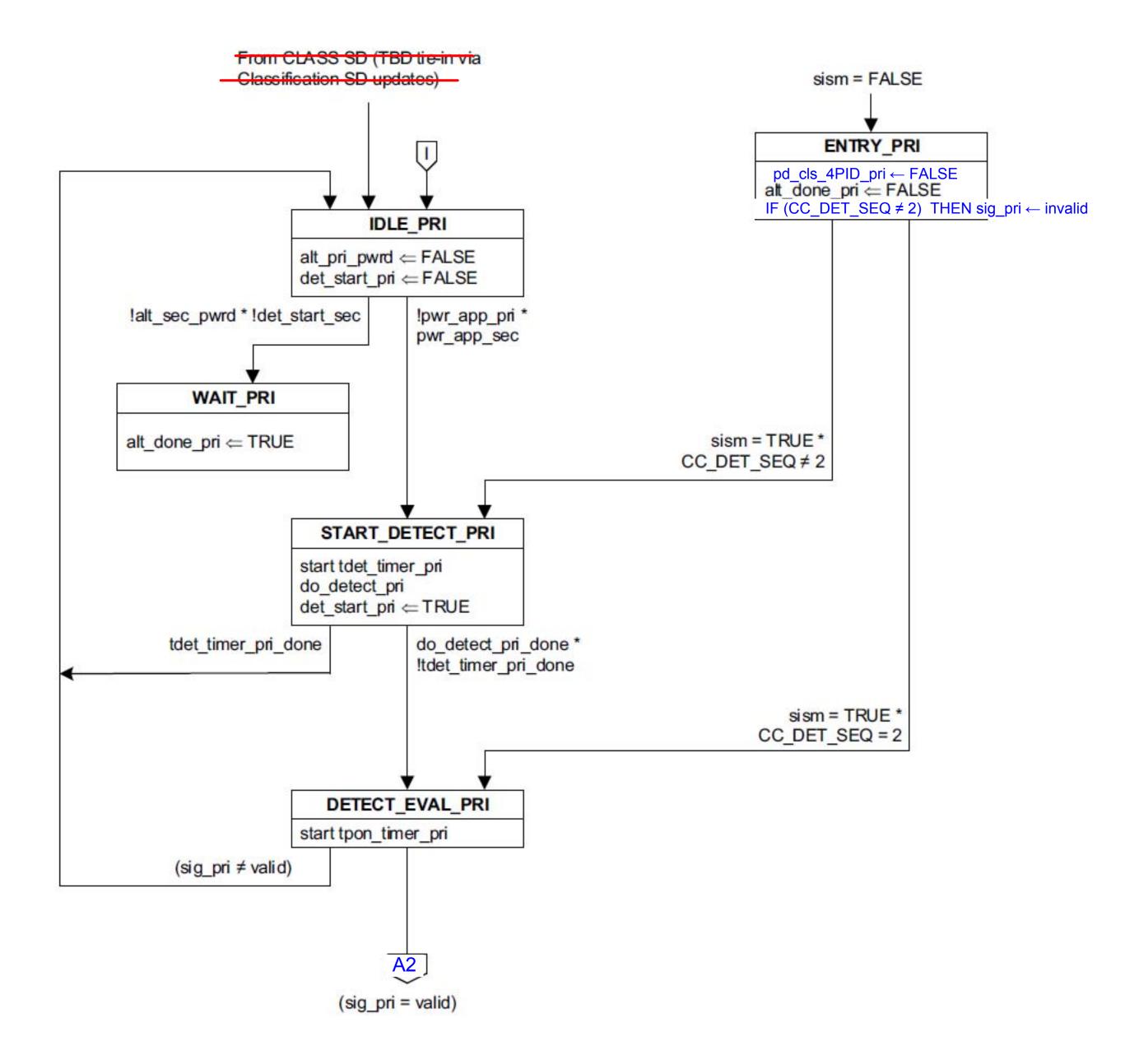

Figure 33–16—Type 3 and Type 4 Primary Alternative dual-signature semi-independent PSE state diagram

**C**2

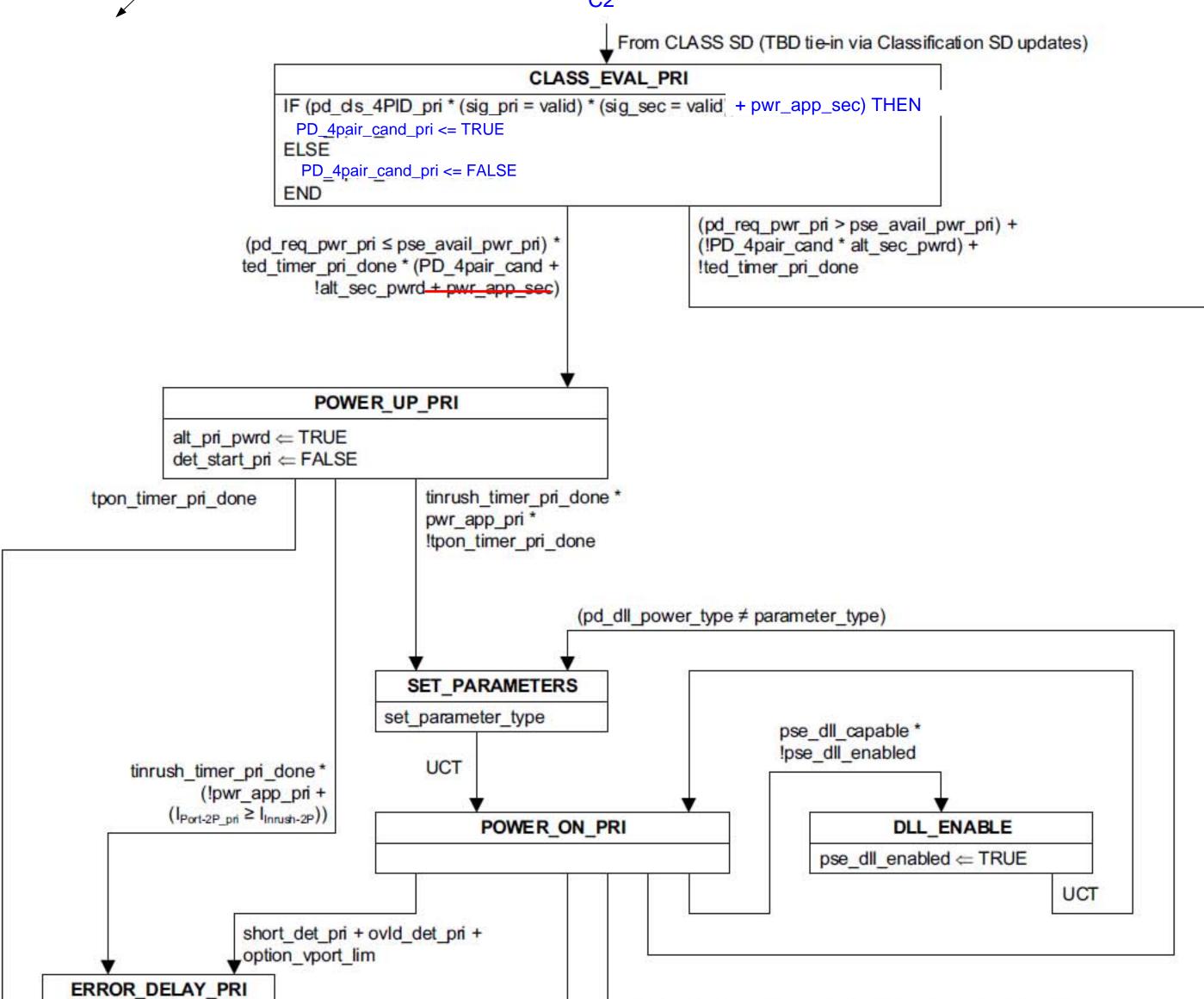

Figure 33–17—Type 3 and Type 4 Primary Alternative dual-signature semi-independent PSE state diagram (continued)

PD\_4pair\_cand <= TRUE

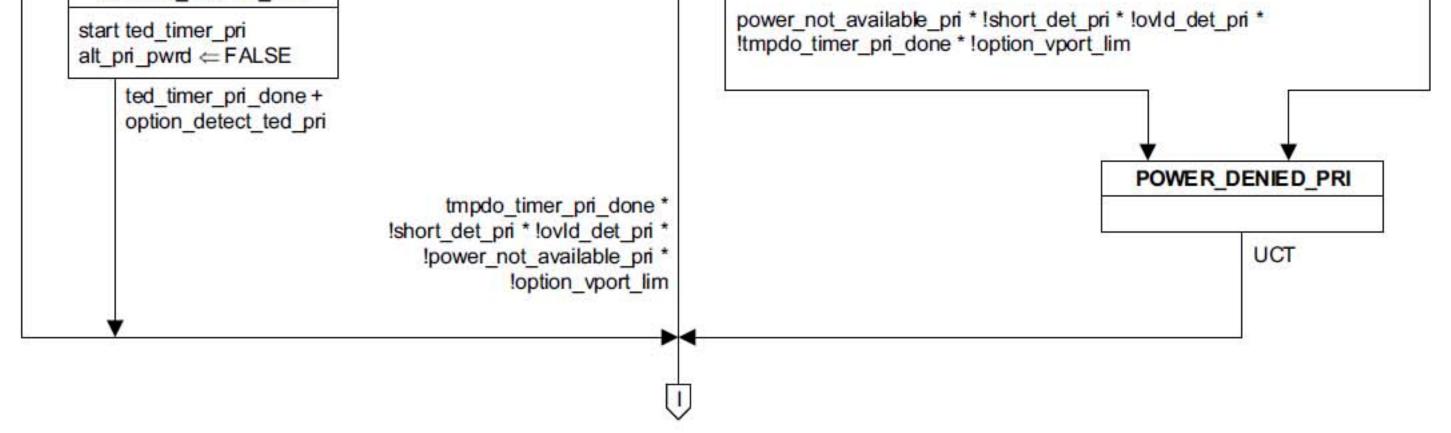

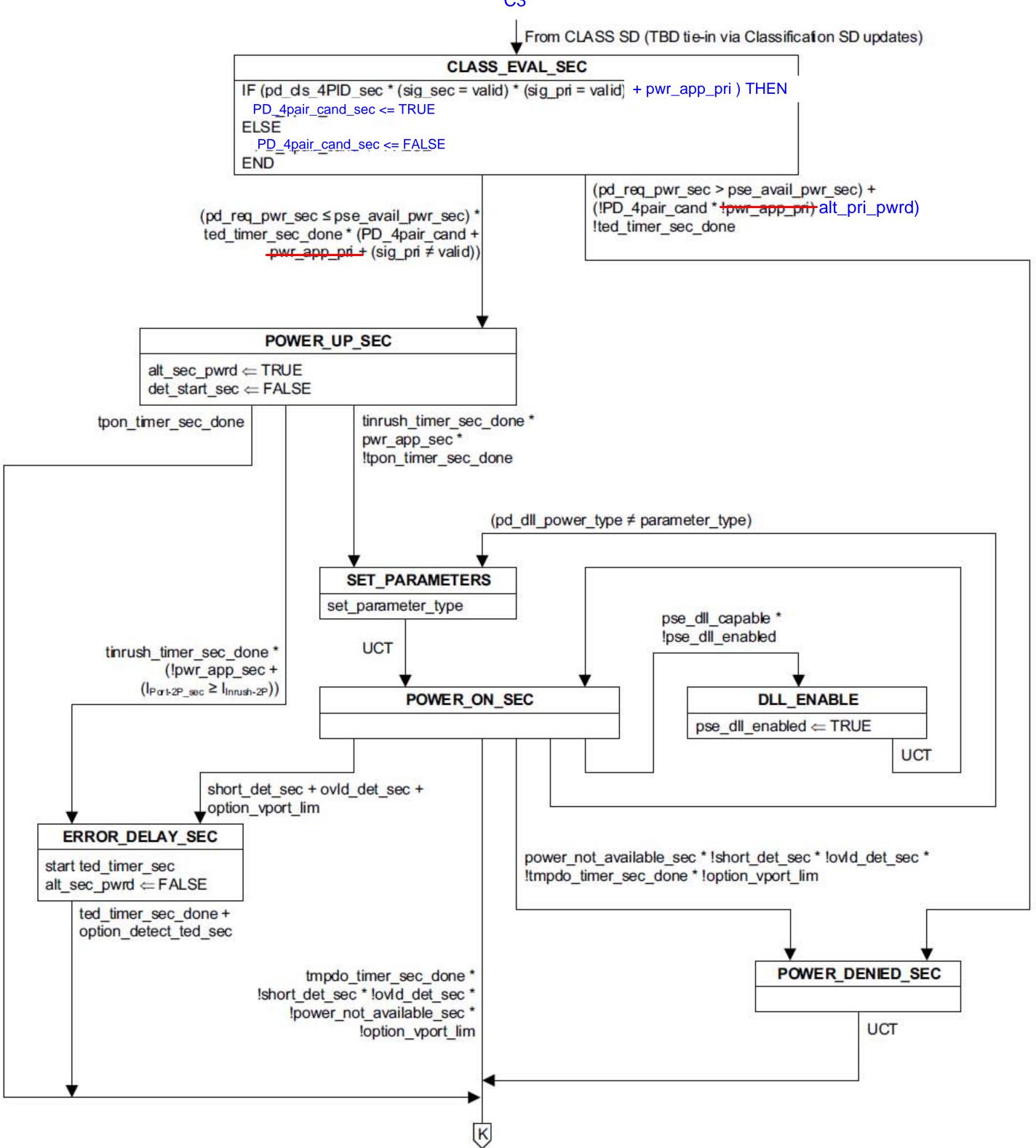

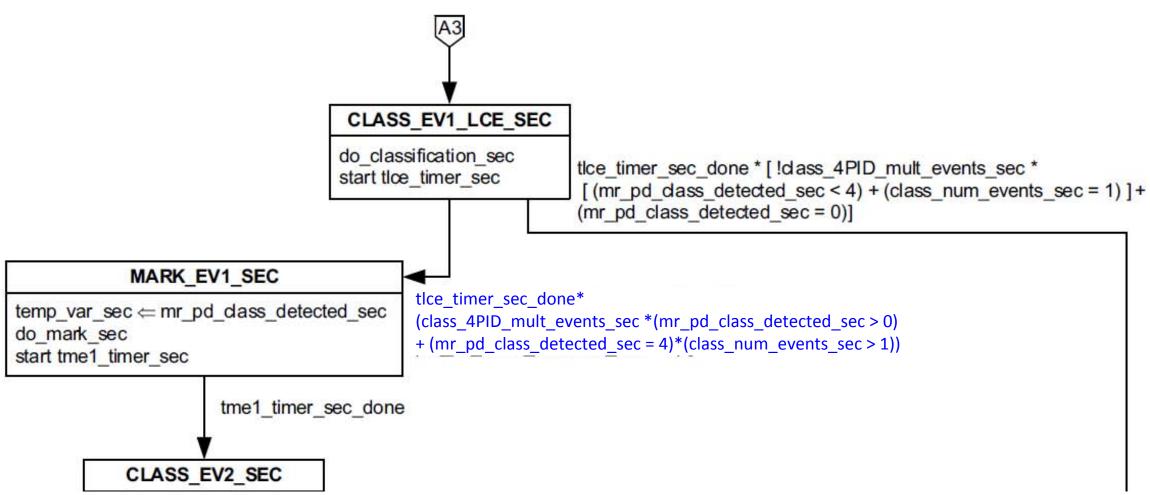

Figure 33–18—Type 3 and Type 4 Secondary Alternative dual-signature semi-independent PSE state diagram

**C3**

Figure 33–18—Type 3 and Type 4 Secondary Alternative dual-signature semi-independent PSE state diagram (continued)

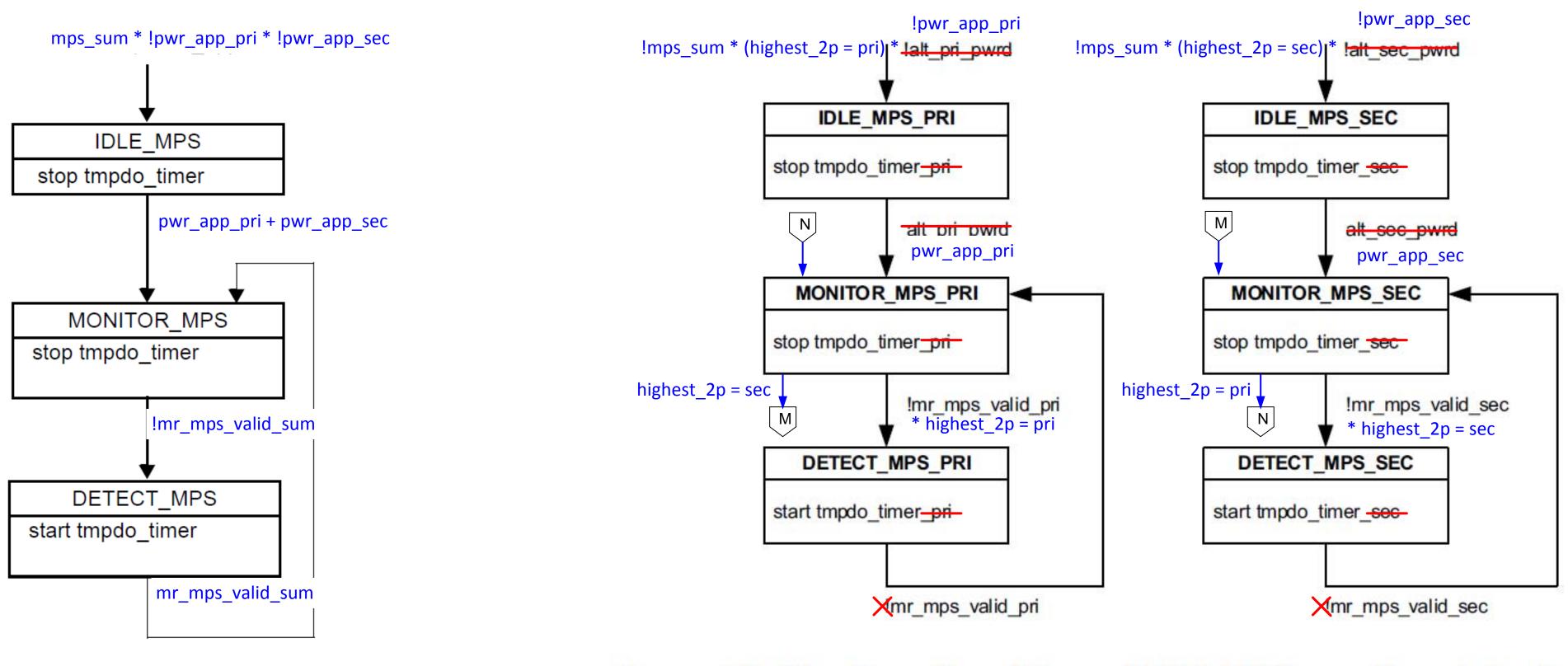

Figure 33–22—Type 3 and Type 4 PSE MPS monitor state diagram for SS PD

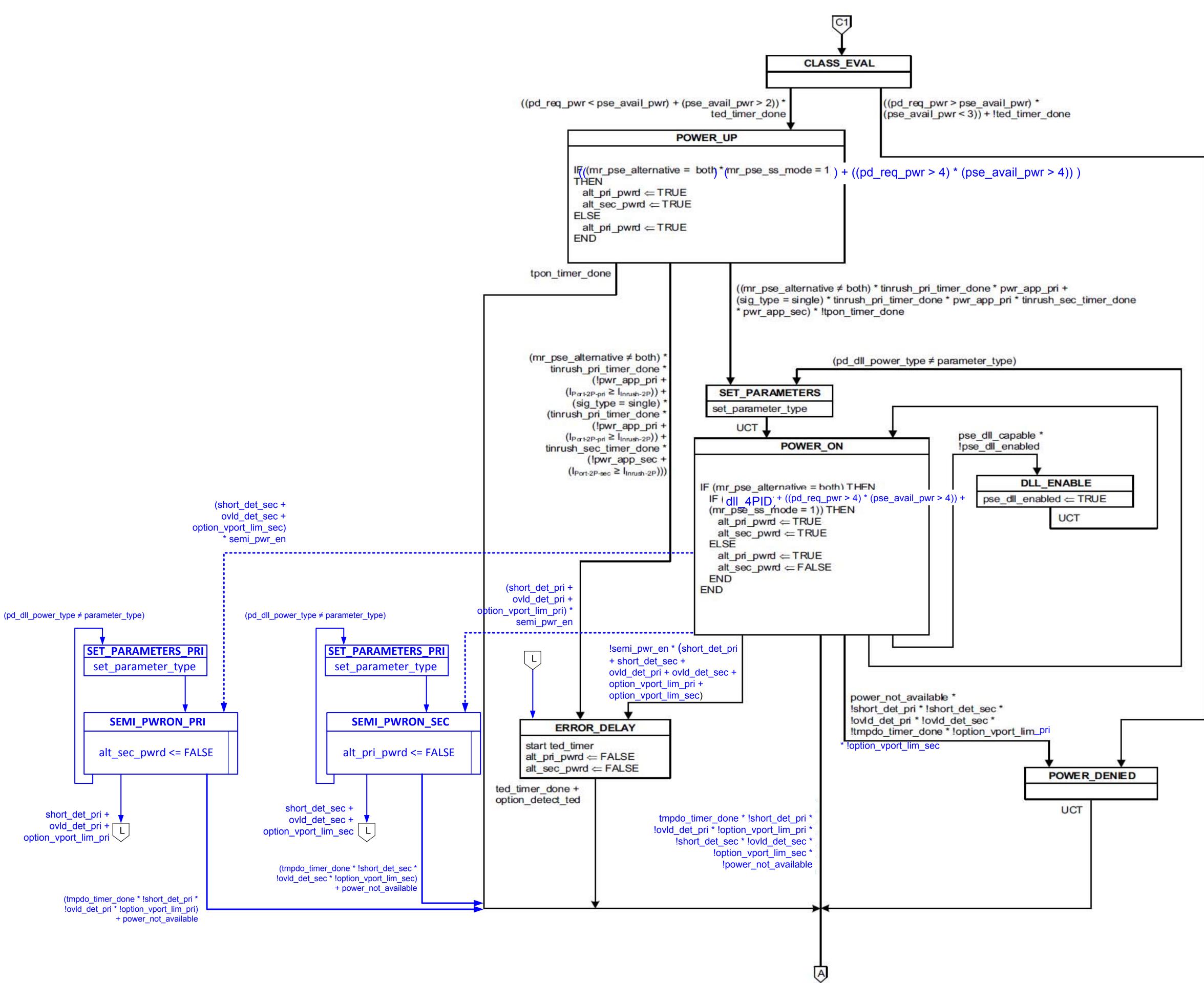

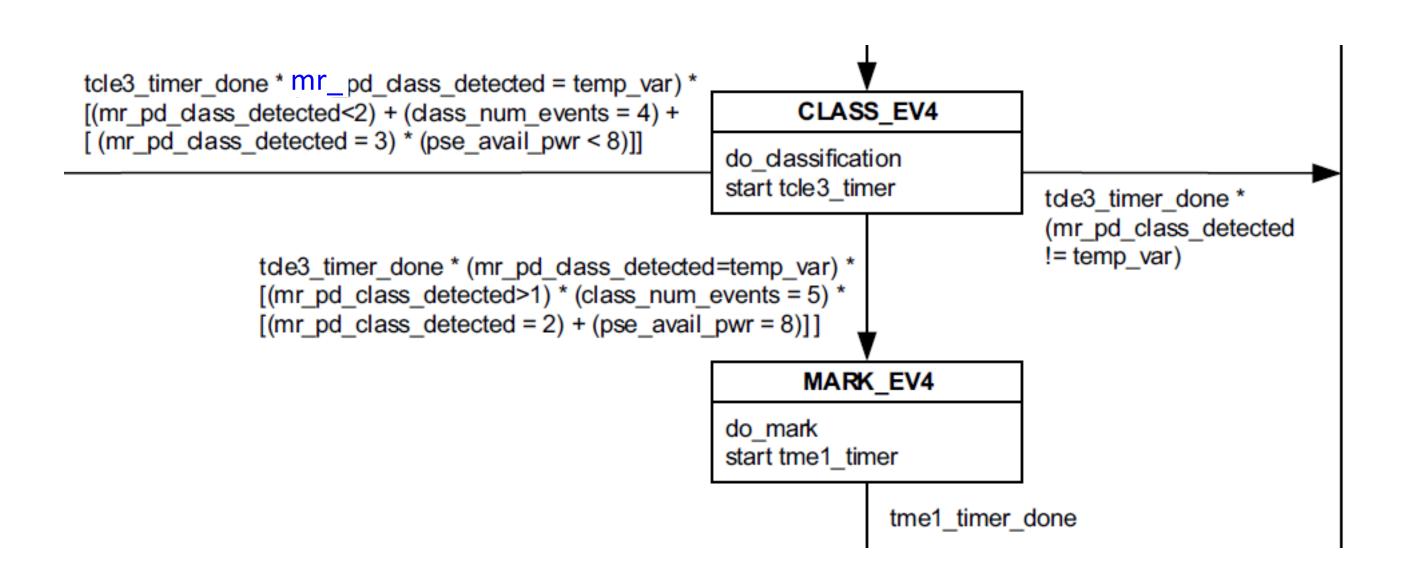

Figure 33–19—Type 3 and Type 4 PSE single-signature classification state diagram

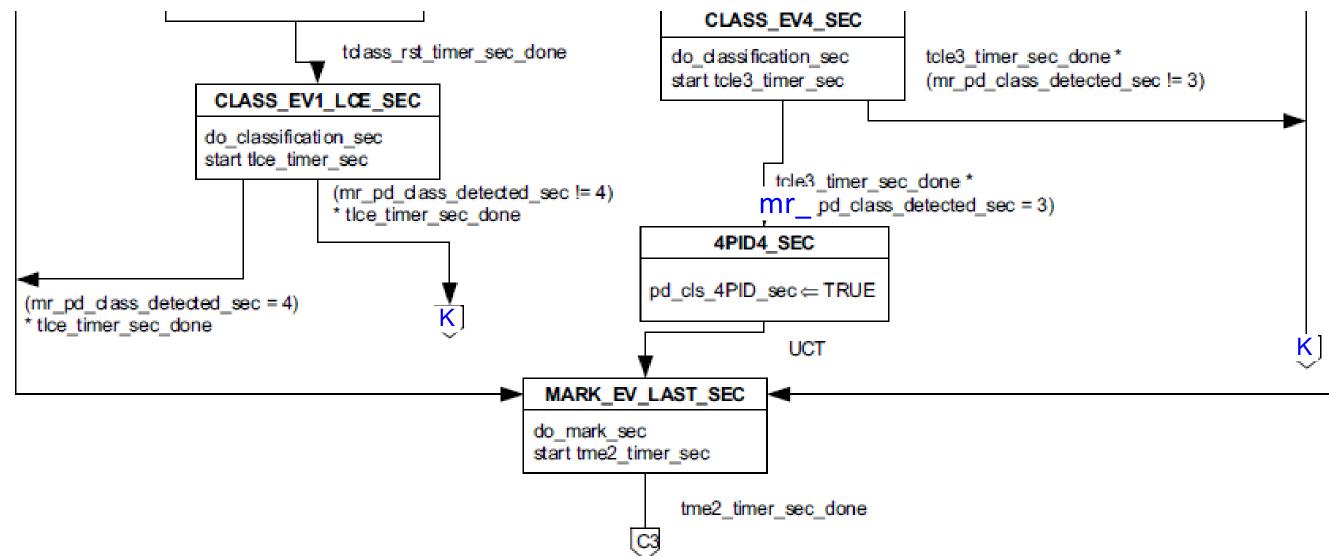

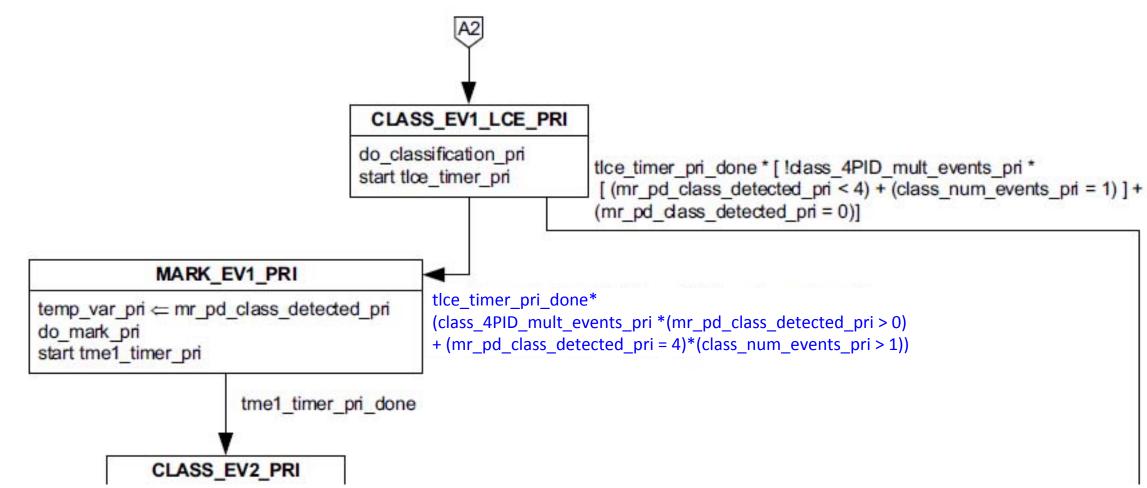

### Figure 33–20—Type 3 and Type 4 PSE dual-signature classification state diagram on the Primary Alternative

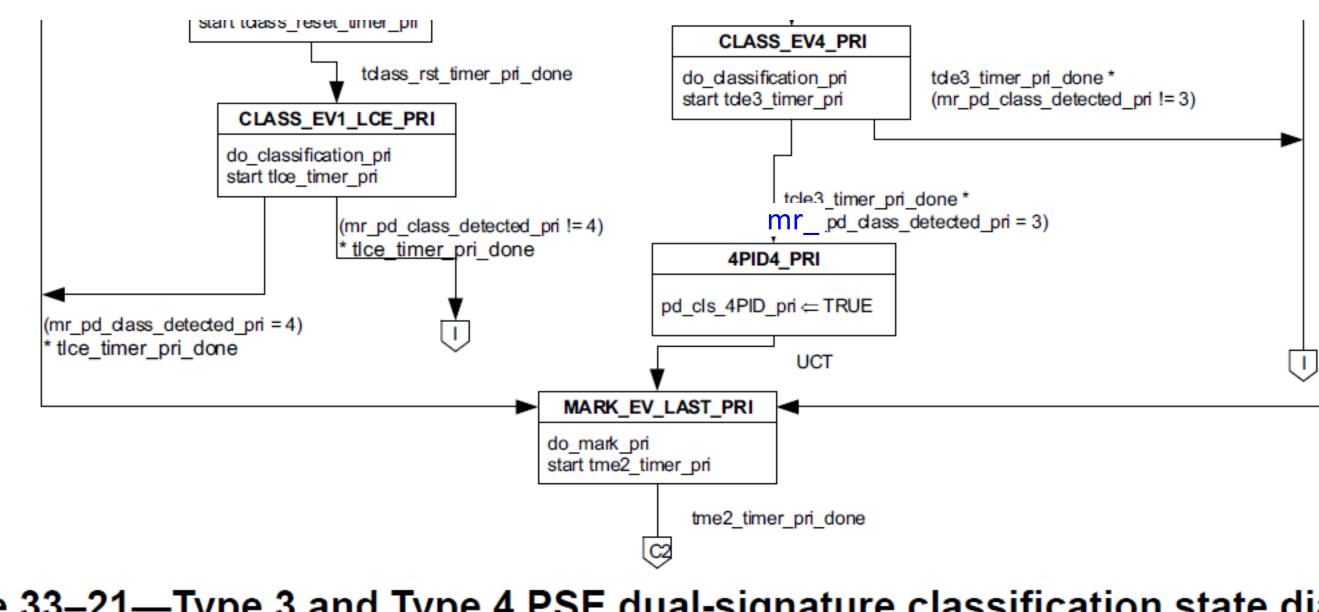

## Figure 33–21—Type 3 and Type 4 PSE dual-signature classification state diagram on the Primary Alternative

### Figure 33–21—Type 3 and Type 4 PSE dual-signature classification state diagram on the Primary Alternative

Figure 33–20—Type 3 and Type 4 PSE dual-signature classification state diagram on the Primary Alternative