#### Unbalance Rev. 3

MICHAEL PAUL

### Summary

- A new variable "I<sub>Unbalance-2p</sub>" was introduced in Draft 3.1 and is used in place of I<sub>Con-2p-unb</sub> in some areas

- ► In Draft 3.1, I<sub>Con-2p-unb</sub> has the same value as I<sub>Unbalance-2p</sub>

- Unbalance interoperability has been compromised

- I<sub>Con-2p-unb</sub> limits were increased in Draft 3.1 in such a way that both the PSE and PD may now be more unbalanced and *interoperability is not guaranteed*

- Fix I<sub>Con-2p-unb</sub> limits

### **Class 5 Case Study**

- I<sub>Unbalance-2p</sub> (550mA) based on worst case cable/connection/diode model delivering 40W

- System Unbalance system models are calibrated with:

- Diode area mismatch of 10

٢

- R<sub>PSE\_alpha</sub> = 2.182 (R<sub>PSE\_alpha</sub> is the gain factor in Eqn. 145-13)

- I<sub>Con-2p,max</sub> was measured as 550mA and this was used as the I<sub>Con-2p-unb</sub> limit until Draft 3.1

$$0 < R_{\text{PSE}_{\text{max}}} \leq \begin{cases} 2.182 \times R_{\text{PSE}_{\text{min}}} - 0.04 & \text{for Class 5} \\ 1.999 \times R_{\text{PSE}_{\text{min}}} - 0.04 & \text{for Class 6} \\ 1.904 \times R_{\text{PSE}_{\text{min}}} - 0.03 & \text{for Class 7} \\ 1.832 \times R_{\text{PSE}_{\text{min}}} - 0.03 & \text{for Class 8} \end{cases}$$

(145–13)

٦

where

$R_{PSE\_max}$ is, given  $R_{PSE\_min}$ , the highest allowable common mode effective resistance in<br/>the powered pairs of the same polarity $R_{PSE\_min}$ is the lower PSE common mode effective resistance in the powered pairs of the<br/>same polarity

## **Class 5 Case Study**

- ▶ Draft 3.1 I<sub>Unbalance-2p</sub> was changed to 560mA to provide margin.

- Now, using the PSE test from table 145-18, R<sub>PSE\_alpha</sub> can be changed to 2.67 and pass the compliance test

- That is the PSE can be more unbalanced and pass the hardware compliance test

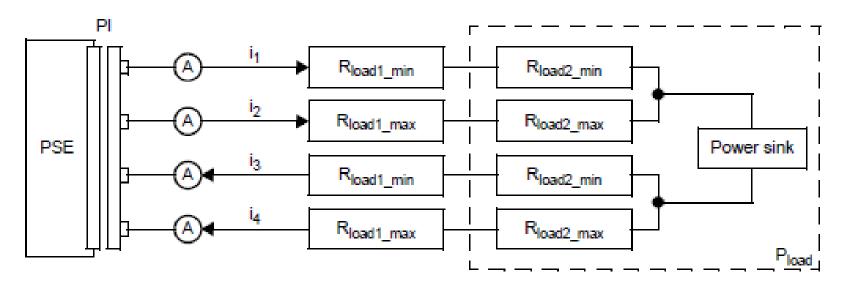

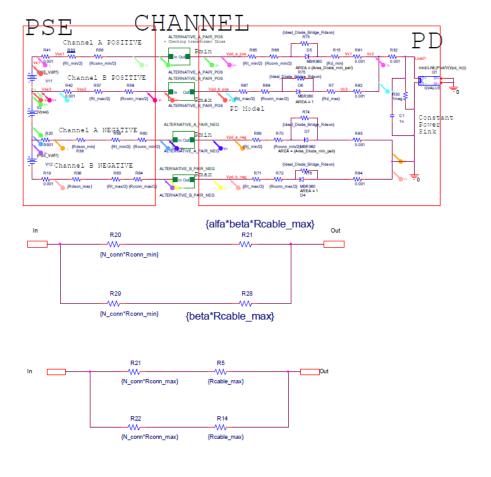

Figure 145–22—PSE PI unbalance specification and system resistance unbalance

### **Class 5 Case Study**

- Plugging R<sub>PSE\_alpha</sub> = 2.67 back into the System Unbalance model gives I<sub>con-2p,max</sub> = 571mA

- This PSE passes the compliance test but may fail to interoperate

Credit: darshan\_01\_0317

# How do we add margin?

- We need two unbalance numbers

- I<sub>Unbalance-2p</sub> for the hardware unbalance test (component unbalance contribution)

- I<sub>Con-2p-unb</sub> for the system at runtime (software-controlled current threshold)

- The hardware test limit must be less than the runtime unbalance limit to ensure margin

- ► I<sub>Unbalance-2p</sub> is the hardware unbalance test

- PSEs and PDs should not exceed I<sub>Unbalance-2p</sub> when connected to the test load/source

- I<sub>Unbalance-2p</sub> should use the I<sub>Con-2p-unb</sub> numbers from Draft 3.0

- Draft 3.0 I<sub>Con-2p-unb</sub> numbers define system performance given PSE, cable and PD unbalance allocations

- ► I<sub>Con-2p-unb</sub> is the runtime test

- A PSE should not remove power from a PD until at least I<sub>Con-2p-unb</sub> is drawn from a pairset

- I<sub>Con-2p-unb</sub> should maintain the numbers specified in Draft 3.1