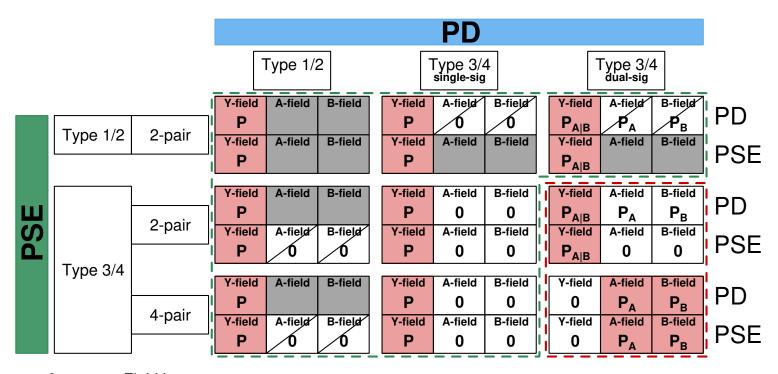

**0** Field is set to zero

P Power for a single-signature or legacy device

P<sub>A</sub> Power for Mode A on a dual-signature PD

**P**<sub>B</sub> Power for Mode B on a dual-signature PD

**P**<sub>AlB</sub> Power for Mode A or Mode B on a dual-signature PD (whichever is powered on)

Y-field Fields PSEAllocatedPower and PDRequestedPower

A-field Fields PSEAllocatedPower\_ModeA and PDRequestedPower\_ModeAB-field Fields PSEAllocatedPower ModeB and PDRequestedPower ModeB

Fields the PSE will use for power allocation

Unsupported field (will not be sent out)

Supported field, but not understood by link partner

# P802.3bt D3.0 – Dual-signature LLDP v153

# Info (not part of baseline)

#### **Purpose**

This is an overhaul for the LLDP specification in Clause 79, specifically addressing dual-signature operation. It aims to address the issues raised in comments #130, #293, #294, #296, and #297.

All of the requirements we currently have in Clause 79 regarding which fields to set to which value depending on the PD Type and such really don't belong there. Clause 79 defines the format of the PoE TLV. How that TLV is to be used must be defined in Clause 33 and Clause 145. Therefore this baseline scraps all of the requirements that were added to subclauses 79.3.2.5, 79.3.2.6, and it's dual-signature brethren.

# Changelog

- v100 First full proposal

- v110 Moved DLL requirements to Clause 145 from Clause 79

- v111 Comments Heath Stewart (editorial)

- v120 4PID bit + restrict new fields to Type 3/4 devices only

- v130 Back to using a single pd\_dll\_enable / pse\_dll\_enable variable for the dual-mode DLL diagrams + big renaming (single-mode and dual-mode DLL)

- v131 Review Yair: ...

- v140 Implemented state diagram changes per (original) concept LLDP adhoc

- v141 Address comment i-391, review Yair, define twopairmode and fourpairmode

- v142 Updated PSE maximum available power description for dual-signature

- v150 Major review by Heath (update state diagrams, define PD\_REQUESTED\_VALUE\_mode(X), update to 145.5.3.7.2

- v151 Setting 'Mirrored\_\*' variables prior to using them

- v152 Remind people in the descriptions of PSE allocated power value field (and also on the PD) that there are additional restrictions.

- v153 Added status bits to discover the powering mode.

# 145.5.3 Power control state diagrams

The power control state diagrams for PSEs and PDs specify the externally observable behavior of a PSE and PD Data Link Layer classification respectively.

# **Info (not part of baseline)**

Type 3/4 PSEs need to always 'run' both the single-signature and the dual-signature state diagrams. These state diagram control the logic needed to set the values of the respective fields correctly.

Data Link Layer classification of PSEs connected to a single-signature PD, shall provide the behavior in the state diagram defined in Figure 145–39 and Figure 145–40. Data Link Layer classification of PSEs connected to a dual-signature PD, shall provide the behavior in the state diagram defined in Figure 145–43.

Data Link Layer classification of PSEs shall provide the behavior in the state diagrams defined in Figure 145–39, Figure 145–40, Figure 145–43, and Figure 145–43a.

#### **Info (not part of baseline)**

For PDs it's different. Single-signature PDs only need to run the single-signature state diagram, dual-signature PDs run both a 2-pair and 4-pair version of their DLL state diagrams.

Single-signature PD Data Link Layer classification shall provide the behavior of the state diagram defined in Figure 145–41 and Figure 145–42. Dual-signature PD Data Link Layer classification shall provide the behavior of the state diagram defined in Figure 145–44, and Figure 145–44a.

Insert new subclause 145.5.3a before 145.5.4 as follows:

# 145.5.3a Power requests and allocations

The variables PDRequestedPowerValue and PDRequestedPowerValue\_mode(X) allow a PD to request an amount of power from the PSE. The variables PSEAllocatedPowerValue and PSEAllocatedPowerValue\_alt(X) allow the PSE to allocate an amount of power to the PD.

PSEs shall use values in the range defined in Table 145–41 for PSEAllocatedPowerValue and PSEAllocatedPowerValue\_alt(X) where X can be A or B. PDs shall use the values in the range defined in Table 145–42 for PDRequested-PowerValue and PDRequestedPowerValue\_mode(X) where X can be A or B.

Table 145-41 — Permitted values for PSEAllocatedPowerValue and PSEAllocatedPowerValue\_alt(X)

| Powering mode | PD configuration | PSEAllocatedPowerValue | PSEAllocatedPowerValue_alt(X) |

|---------------|------------------|------------------------|-------------------------------|

| 2-pair        | _                | $1 - 255^a$            | 0                             |

| 4-pair        | single-signature | 1 – 999                | 0                             |

|               | dual-signature   | 0                      | 1 – 499                       |

a NOTE—A PSE that has encountered a fault that requires to operate in 2-pair mode, may use values 1–499 for this variable.

# Table 145–42 — Permitted values for PDRequestedPowerValue and PDRequestedPowerValue\_mode(X)

| Powering mode | PD configuration | PDRequestedPowerValue | PDRequestedPowerValue_mode(X) |

|---------------|------------------|-----------------------|-------------------------------|

| _             | single-signature | 1 – 999               | 0                             |

| 2-pair        | dual-signature   | $1 - 255^a$           | 1 – 499                       |

| 4-pair        |                  | 0                     | 1 – 499                       |

WOTE—A PD that has encountered a fault that requires to operate in 2-pair mode, may use values 1–499 for this variable.

# 145.5.3 Power control state diagrams

Editor to add/remove to the variable lists such that they match with what is used in the state diagrams.

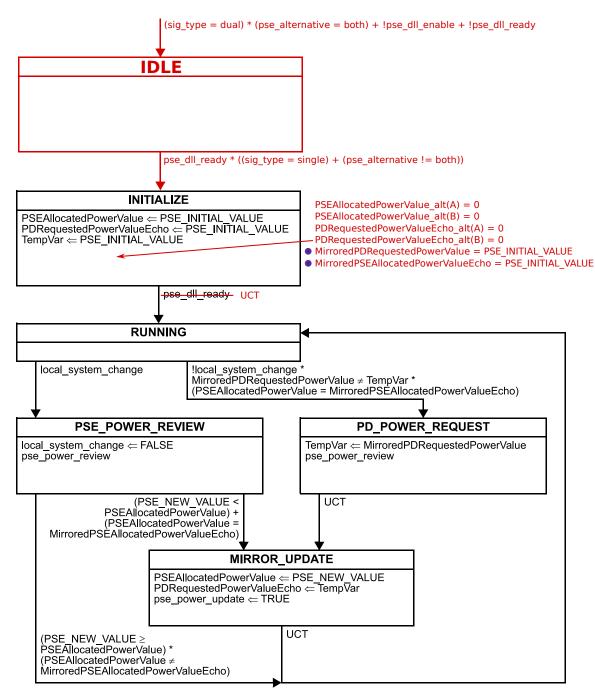

# 145.5.3.3 PSE power control state diagrams (single-signature)

This subclause contains the variables and state diagrams the PSE uses when connected to a single-signature PD, or when it is providing power over 2 pairs.

This state diagram controls the PSEAllocatedPowerValue variable, which is used to allocate power to a PD. This variable and the corresponding LLDPDU field is used for power allocation when the PSE is connected to a single-signature PD, or when the PSE is only capable of supplying power over 2-pair.

#### **145.5.3.3.3 State diagrams**

#### Info (not part of baseline)

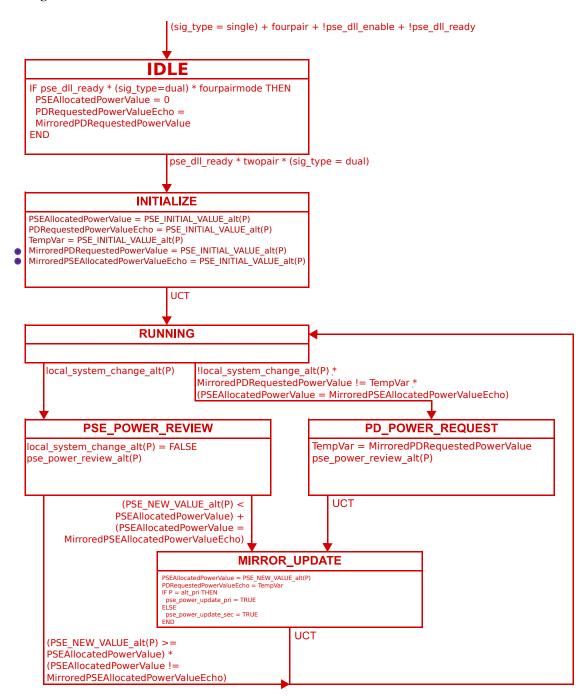

This is one of the three state diagrams that the PSE needs to run. It sits in IDLE whenever DLL isn't enabled or not ready, or when the other state diagrams need to be in control (dual-signature detected). It proceeds to INITIALIZE when DLL is ready and the PD is a single-signature, or the PSE is restricted to 2-pair operation.

Also fixed is the issue where Mirrored\_\* variables are read before they are set. Mirrored variables contain the contents of incoming LLDPDUs and get set only when a frame is received. During the time between the first frame being received and DLL being enabled, their value is undefined. Fixes related to this issue are marked with a purple circle.

# Change Figure 145–39 as follows:

Figure 145-39—PSE power control state diagram for single-signature PDs

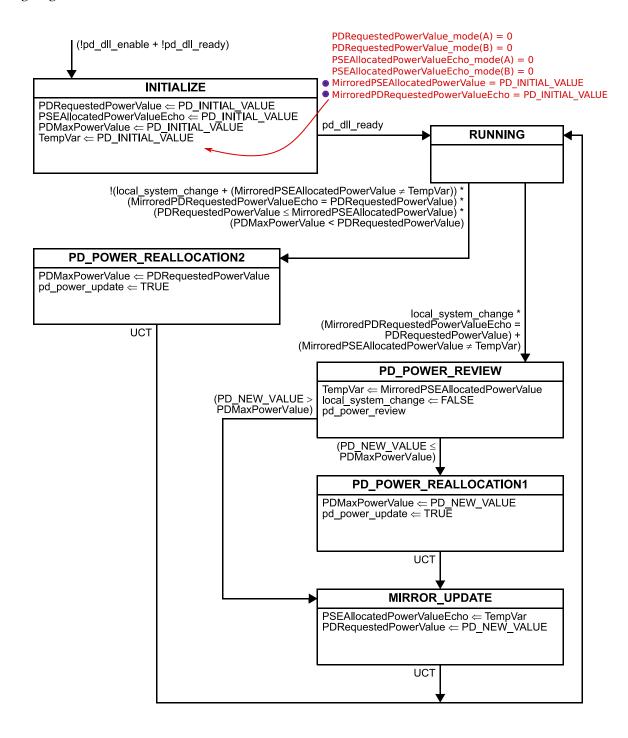

# 145.5.3.4 Single-signature PD power control state diagram

#### Add the following text to this empty subclause:

This state diagram controls the PDRequestedPowerValue variable, which is used to request power from a PSE, when the PD is a single-signature PD.

#### **145.5.3.4.5** State diagrams

#### Info (not part of baseline)

This is the state diagram for single-signature PDs. By setting the A/B fields to zero in INITIALIZE we have made this state diagram self-sufficient for single-signature. The other state diagrams intended for dual-signature do not need to run (as reflected in the text earlier).

#### Change Figure 145-41 as follows:

Figure 145-41—Single-signature PD power control state diagram

# 145.5.3.6 PSE power control state diagrams (dual-signature)

# Add the following text to this empty subclause:

This state diagram controls the PSEAllocatedPowerValue\_alt(X) variables, which are used to allocate power to the

individual Modes of a dual-signature PD. These variables and the corresponding fields in the LLDPDU are used for power allocation when the connected PD is a dual-signature PD that is supplied in 4-pair mode.

#### Insert new subclause 145.5.3.6.0a below 145.5.3.6 as follows:

#### 145.5.3.6.0a Alternative designation

PSEs providing power to a dual-signature PD operate over two semi-independent state diagrams, one for Alternative A, another for Alternative B. Alternative information is obtained by replacing the X in the desired variable or function with the letter of the Alternative of interest. Alternatives are referred to in general as follows:

X

Generic Alternative designator. When X is used in a state diagram, its value is local to that state diagram and not global to the set of state diagrams.

Values:

A: Alternative A B: Alternative B

P

Powered Alternative designator. When P is used in a state diagram, its value is local to that state diagram and not global to the set of state diagrams. "P" refers to the Alternative that is currently powered. It's value is only defined when the PSE operates in 2-pair mode.

Values:

A: Alternative A B: Alternative B

# 145.5.3.6.1 Variables

. . .

Dual-signature PSEs provide the behavior of the state diagram shown in Figure 145–39 over each pairset independently unless otherwise specified. All the parameters that apply to Alternative A and Alternative B are denoted with the suffix " $_{alt}(X)$ " where "X" can be "A" or "B", as defined in 145.5.3.6.0a. A parameter that ends with the suffix " $_{alt}(X)$ " may have different values for Alternative A and Alternative B.

#### **Info** (not part of baseline)

We are using the shorthands 'twopairmode' and 'fourpairmode' in the PSE state diagrams. These are defined below. Note that the  $\land$  symbol denotes boolean XOR as defined in 21.5.4.

# Add the variable / alias to the variable list as follows:

- twopairmode: Alias for the following term: (alt\_pwrd\_pri ∧ alt\_pwrd\_sec)

- fourpairmode: Alias for the following term: (alt\_pwrd\_pri \* alt\_pwrd\_sec)

#### **Info** (not part of baseline)

There are a bunch of statements "When a PD mode is not active, the value is set to zero." and "When a PD mode is not active, the value shall be set to zero." that do not belong in the variable section.

# Remove the following statements from 145.5.3.6.1:

- When a PD mode is not active, the value is set to zero.

- When a PD mode is not active, the value shall be set to zero.

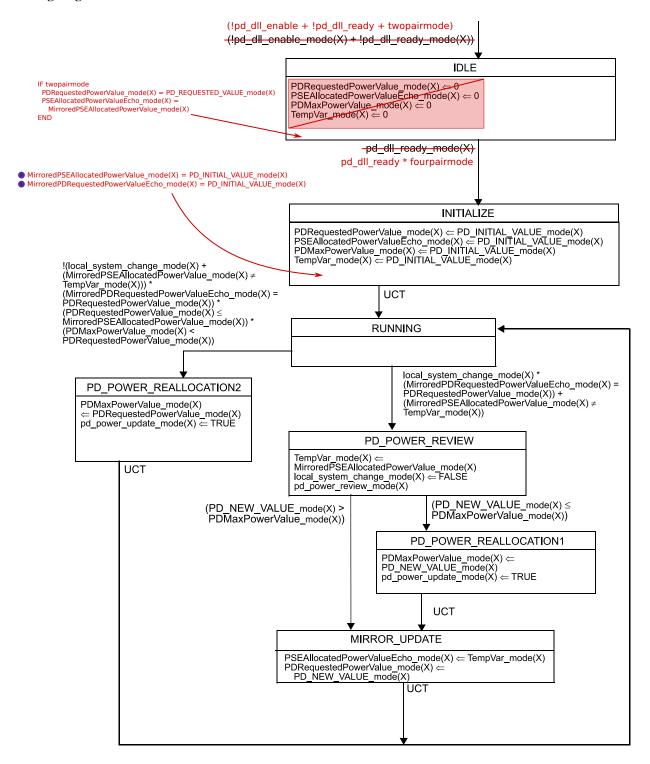

#### **145.5.3.6.3** State diagrams

#### Change Figure 145-43 as follows:

Figure 145-43—PSE power control state diagram for dual-signature PDs in 4-pair mode

Figure 145-43a-PSE power control state diagram for dual-signature PDs in 2-pair mode

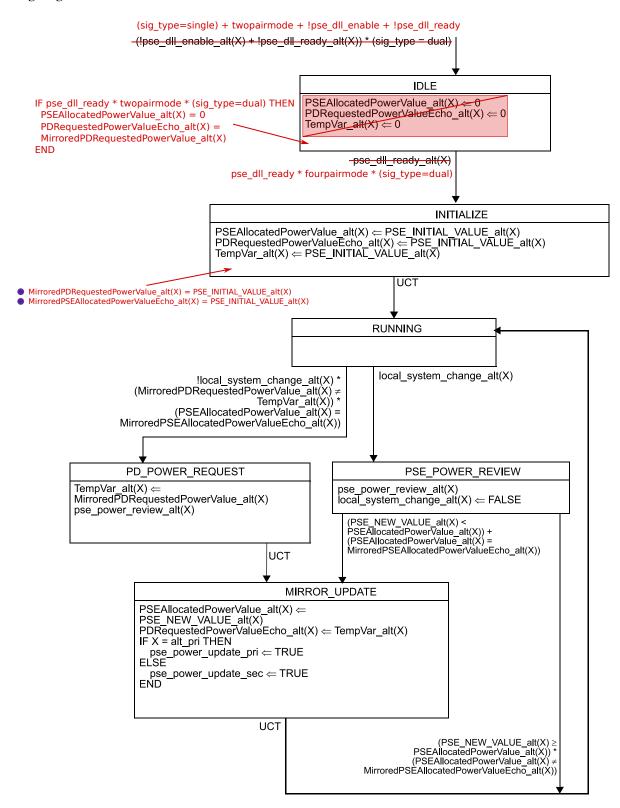

# 145.5.3.7 Dual-signature PD power control state diagrams

# Add the following text to this empty subclause:

This state diagram controls the PDRequestedPowerValue\_mode(X) variables, which are used to allocate power to the individual Modes of a dual-signature PD. It is applicable when the PD is a dual-signature PD that is supplied in 4-pair mode.

#### Insert new subclause 145.5.3.7.0a below 145.5.3.7 as follows:

#### 145.5.3.7.0a Mode designation

Dual-signature PDs are implemented on Mode A and Mode B as defined in 145.3.2. Mode information is obtained by replacing the X in the desired variable or function with the letter of the Mode of interest. Modes are referred to in general as follows:

X

Generic Mode designator. When X is used in a state diagram, its value is local to that state diagram and not global to the set of state diagrams.

Values:

A: Mode A

B: Mode B

P

Powered Mode designator. When P is used in a state diagram, its value is local to that state diagram and not global to the set of state diagrams. "P" refers to the Mode that is currently powered. It's value is only defined when the PD is powered over 2-pair.

Values:

A: Mode A

B: Mode B

#### 145.5.3.7.2 Variables

# Info (not part of baseline)

We are using the shorthands 'twopairmode' and 'fourpairmode' in the PD state diagrams. These are defined below. Note that the  $\land$  symbol denotes boolean XOR as defined in 21.5.4. Unlike for the PSE there is no easy method to derive if a Mode is powered. The best method is to check that present\_mps\_mode(X) is set to TRUE to determine if a Mode is powered.

# Add the variable / alias to the variable list as follows:

- twopairmode: Alias for the following term: (present\_mps\_mode(A) ∧ present\_mps\_mode(B))

- fourpairmode: Alias for the following term: (present\_mps\_mode(A) \* present\_mps\_mode(B))

# Add the PD\_REQUESTED\_VALUE\_mode(X) variable to the variable list as follows:

#### PD\_REQUESTED\_VALUE\_mode(X)

The value of this variable is used by the dual-signature to indicate the amount of power it requires on Mode A and Mode B, while it is being powered in 2-pair mode.

Values: 1 through 499

# Info (not part of baseline)

There are a bunch of statements "When a PD mode is not active, the value is set to zero." and "When a PD mode is not active, the value shall be set to zero." that do not belong in the variable section.

#### Remove the following statements from 145.5.3.7.2:

- When a PD mode is not active, the value is set to zero.

- When a PD mode is not active, the value shall be set to zero.

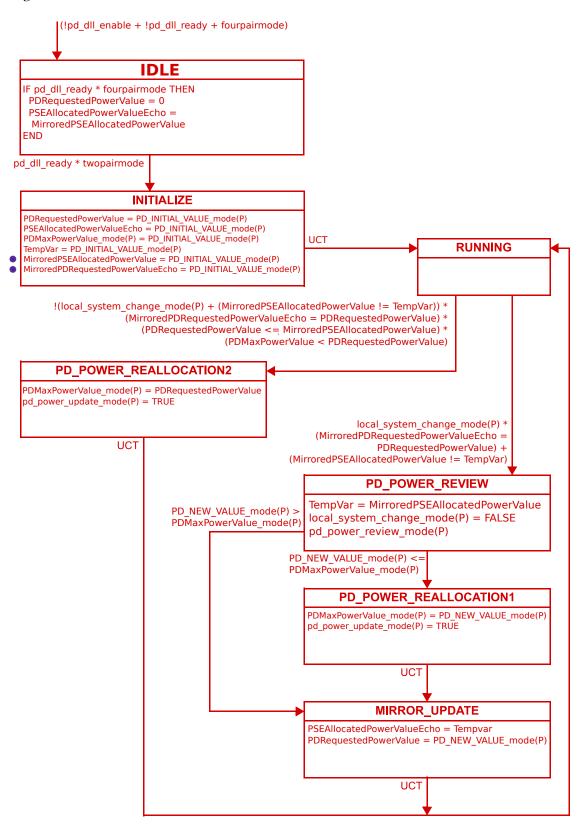

#### **145.5.3.7.4** State diagrams

#### Change Figure 145-44 as follows:

Figure 145-44—Dual-signature PD power control state diagram for 4-pair mode

# Insert Figure 145-44a as follows:

Figure 145-44a --- Dual-signature PD power control state diagram for 2-pair mode

# 145.5.5 State change procedure across a link (dual-signature)

Add new subclause under 145.5.5 as follows:

# 145.5.5.1a Transitions between 2-pair and 4-pair mode (dual-signature)

When a PSE, connected to a dual-signature PD, transitions from 4-pair to 2-pair operation, it shall assign the value of PSEAllocatedPowerValue\_alt(X), where X is the powered Alternative, to PSEAllocatedPowerValue. The purpose of this is that the PD can continue operating over the remaining powered Mode.

When a PSE, connected to a dual-signature PD, transitions from 2-pair to 4-pair operation, it shall assign the value of PSEAllocatedPowerValue to PSEAllocatedPowerValue\_alt(X), where X is the Alternative that was initially powered. A dual-signature PD that is switched from 4-pair to 2-pair mode requests the amount of power it needs for 2-pair operation in the PDRequestedPowerValue variable. Per Table 145–42 this is the requested power for the active Mode.

# 79.3.2 Power via MDI TLV

. . .

The Power via MDI TLV shown in Figure 79–3 was originally defined in IEEE Std 802.1AB-2005 Annex G.3. This original TLV only supported the first three fields of Figure 79–3, labeled basic fields, enabling discovery and advertisement of Power via MDI capabilities. The Power via MDI TLV was revised by IEEE Std 802.3at-2009 to add a further three fields, labeled DLL classification extension, to provide Data Link Layer (DLL) classification capabilities. The Power via MDI TLV was revised again by IEEE Std 802.3bt-201x to add a further nine fields, labeled Type 3 and Type 4 extension to support additional capabilities offered by Type 3 and Type 4 PSEs and PDs.

Type 1 and Type 2 devices shall not support the Type 3 and Type 4 extension.

٠..

#### Append to the following paragraph as follows:

If a Type 1 or Type 2 power entity implements Data Link Layer classification, it shall support the Power Via MDI TLV DLL classification extension fields shown in Figure 79–3 after the PI has been powered. If a Type 3 or Type 4 power entity implements Data Link Layer classification, it shall support both the DLL classification extension fields and Type 3 and Type 4 extension fields shown in Figure 79–3 after the PI has been powered. Type 1 and Type 2 devices shall not include the Type 3 and Type 4 extension fields in transmitted LLDPDU's.

# **Info** (not part of baseline)

Out of all the fields and bits in the "Type 3 and Type 4 extensions", there is one bit that is specifically intended for Type 1 and Type 2 PDs. The PD 4PID bit allows such a PD to assert that it is 4-pair capable. By having this bit in the "Type 3 and Type 4 extensions" fields, we open up Pandora's box of having the define ALL of the fields for Type 1 and Type 2 devices.

The proposed solution is to move this bit into a reserved bit of the existing fields. That way, the "Type 3 and Type 4 extensions" can be restricted to Type 3 and Type 4 devices only.

# 79.3.2.4.1 Power type

Move the PD 4PID bit from Table 79–6d (System setup field) to bit position 2 in Table 79-4 (Power type/source/priority field) as follows:

Table 79-6d-System setup field

| Bit | Function            | Value/meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6 | Reserved            | Transmit as zero. Ignore on receive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 5:2 | Power typex PD 4PID | 5         4         3         2           1         1         1         1         = Type 4 dual-signature PD           1         1         0         1         = Type 3 dual-signature PD           1         1         0         1         = Reserved/Ignore           1         0         1         1         = Reserved/Ignore           1         0         1         = Type 4 single-signature PD           1         0         0         = Type 4 PSE           0         1         1         = Type 3 single-signature PD           0         1         1         = Type 3 PSE           0         1         0         = Type 2 PD           0         1         0         = Type 2 PSE           0         0         1         = Type 1 PSE           0         0         1         = Reserved/Ignore           0         0         0         = Reserved/Ignore |  |

| 1   | PD 4PID             | 1 = PD supports powering of both Modes simultaneously 0 = PD does not support powering of both Modes simultaneously                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 0   | PD Load             | 1 = PD is dual-signature and power demand on Mode A and Mode B are electrically isolated. 0 = PD is single-signature or dual-signature and power demand on Mode A and Mode B are not electrically isolated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

Table 79-4—Power type/source/priority field

| Bit | Function                | Value/meaning                                                                                                                    |

|-----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | power type              | 7 6<br>1 1 = Type 1 PD<br>1 0 = Type 1 PSE<br>0 1 = Type 2 PD<br>0 0 = Type 2 PSE                                                |

| 5:4 | power source            | Where power type = PD $ \frac{5}{1}  \frac{4}{1} = PSE \text{ and local} $ $1  0 = Reserved $ $0  1 = PSE $ $0  0 = Unknown $    |

| (   | Move 4PID<br>to bit 2   | Where power type = PSE $\frac{5}{1}$ $\frac{4}{1}$ = Reserved $1$ 0 = Backup source $0$ 1 = Primary power source $0$ 0 = Unknown |

| 3:2 | Reserved power priority | Transmit as zero, ignore on receive     1                                                                                        |

#### **Info** (not part of baseline)

Restore sections on PD requested power and PSE allocated power. The new subclause in Clause 145 above will deal with what needs to be filled out in particular circumstances.

# 79.3.2.5 PD requested power value

#### Info (not part of baseline)

We have now changed this legacy field to include 0 as a valid value. For Type 1/2 this was an illegal value, which now becomes a legal value, which leads to undefined behavior if used. This would not be a problem, were it not that Clause 33, by mistake, allows the value 0 in the variable that is linked to this field. We will need to file an MR to change the DLL state diagram in Clause 33, to restrict the value PDRequestedPowerValue from 1 through 255. Both changes together do not result in a change in legacy requirements.

#### Replace content above the dashed line with content below the dashed line as follows:

The PD requested power value field shall contain the PDs requested power value defined in Table 79–5, for Type 1, Type 2, and single-signature Type 3 and Type 4 PDs. The fields for PD requested power value shall be set to the sum of PD requested power value Mode A and PD requested power value Mode B in Table 79–6a, for Type 3 and Type 4 dual-signature PDs.

The PD requested power value field shall contain the PDs requested power value defined in Table 79–5. See 33.6.3.3 and Table 145–42 for permitted value ranges.

#### Change Table 79–5 as follows:

Table 79–5 — PD requested power value field

| Bit  | Function     | Value/meaning                                                                                     |

|------|--------------|---------------------------------------------------------------------------------------------------|

| 15:0 | PD requested | $Power = 0.1 \times (decimal value of bits) Watts.$                                               |

|      | power value  | Power expressed in units of 0.1 W.                                                                |

|      |              | Valid values for these bits are decimal $\frac{1}{2}$ 0 through $\frac{255}{2}$ $\frac{999}{2}$ . |

# 79.3.2.6 PSE allocated power value

#### **Info (not part of baseline)**

We have now changed this legacy field to include 0 as a valid value. For Type 1/2 this was an illegal value, which now becomes a legal value, which leads to undefined behavior if used. This would not be a problem, were it not that Clause 33, by mistake, allows the value 0 in the variable that is linked to this field. We will need to file an MR to change the DLL state diagram in Clause 33, to restrict the value PSEAllocatedPowerValue from 1 through 255. Both changes together do not result in a change in legacy requirements.

# Replace content above the dashed line with content below the dashed line as follows:

The PSE allocated power value field shall contain the PSE's allocated power value defined in Table 79–6 <u>for</u> PSEs connected to single-signature PDs and Type 1 and Type 2 PDs.

The sum of the PSE allocated power value Alternative A field and the PSE allocated power value Alternative B field, as defined in Table 79–6a, shall be provided in the PSE allocated power value field for Type 3 and Type 4 PSEs connected to a dual-signature PD. The sum of the PSE allocated power value Alternative A field and the PSE allocated power value Alternative B field may be provided in the PSE allocated power value field for Type 1 and Type 2 PSEs when connected to a dual-signature PD.

The PSE allocated power value field shall contain the PSEs allocated power value defined in Table 79–6. See 33.6.3.3 and Table 145–41 for permitted value ranges.

Table 79–6 — PSE allocated power value field

| Bit  | Function      | Value/meaning                                                                     |

|------|---------------|-----------------------------------------------------------------------------------|

| 15:0 | PSE allocated | Power = $0.1 \times$ (decimal value of bits) Watts.                               |

|      | power value   | Power expressed in units of 0.1 W.                                                |

|      |               | Valid values for these bits are decimal $\frac{4}{0}$ through $\frac{255}{999}$ . |

# 79.3.2.6a Dual-signature PD requested power value Mode A and Mode B

The "Dual-signature PD requested power value Mode A and Mode B" fields shall contain the PD requested power value defined in Table 79–6a and Table 79–6aa for Mode A and for Mode B of a dual-signature PD.

If Mode (X) is non-active while the other mode is active, the inactive PD requested power value Mode (X) field value shall be set to 0.

Single-signature PDs shall set the PD requested power value Mode A and Mode B fields to 0.

"Dual-signature PD requested power value Mode A" and "Dual-signature PD requested power value Mode B" are the maximum input average power levels (see 145.3.8.2) the PD is requesting for the respective Mode.

# Info (not part of baseline)

Each field has its own Table in Clause 79. Table 79–6a and 79–6b are the only exception where two fields share a Table. I'm splitting them into two Tables to be consistent.

Change Table 79-6a as follows and create new Table 79-6aa:

Table 79-6a — Dual-signature PD requested power value field for Mode A

| Bit  | Function                                | Value/meaning                                                |

|------|-----------------------------------------|--------------------------------------------------------------|

| 15:0 | Dual-signature PD requested power value | Power expressed in units of 0.1 W.                           |

|      | Mode A                                  | Valid values for these bits are decimal $\pm 0$ through 499. |

Table 79–6aa — Dual-signature PD requested power value field for Mode B

| Bit  | Function                                | Value/meaning                                                |

|------|-----------------------------------------|--------------------------------------------------------------|

| 15:0 | Dual-signature PD requested power value | Power expressed in units of 0.1 W.                           |

|      | Mode B                                  | Valid values for these bits are decimal $\pm 0$ through 499. |

# 79.3.2.6b PSE allocated power value Alternative A and Alternative B

The "PSE allocated power value Alternative A field" and the "PSE allocated power value Alternative B" field shall contain the values in Table 79–6b and Table 79–6ba. for Type 3 and Type 4 PSEs operating over both pairsets when connected to a dual-signature PD.

Change Table 79-6b as follows and create new Table 79-6ba:

Table 79-6b - PSE allocated power value field for Alternative A

| Bit  | Function                      | Value/meaning                                           |

|------|-------------------------------|---------------------------------------------------------|

| 15:0 | PSE allocated power value for | Power expressed in units of 0.1 W.                      |

|      | Alternative A                 | Valid values for these bits are decimal ±0 through 499. |

Table 79-6ba — PSE allocated power value field for Alternative B

| Bit  | Function                      | Value/meaning                                           |

|------|-------------------------------|---------------------------------------------------------|

| 15:0 | PSE allocated power value for | Power expressed in units of 0.1 W.                      |

|      | Alternative B                 | Valid values for these bits are decimal ±0 through 499. |

#### Move the paragraph below (with changes) to above Table 79-6b in this subclause.

The "PSE allocated power value Alternative A" and "PSE allocated power value Alternative B" fields are the maximum input average power levels (see 145.3.8.2) the PSE expects the dual-signature PD to draw on the respective Alternatives, when the PSE provides power over 4-pair. "PSE allocated power value Alternative A" and "PSE allocated power value Alternative B" These fields are the power levels at the dual-signature PD PI. The PSE uses this value these values to compute P<sub>Class-2P</sub> as defined in 145.2.7. A PSE providing power to a Type 1, Type 2, or single signature Type 3 or Type 4 PD, places 0 in the "PSE allocated power value Alternative A" and "PSE allocated power value Alternative B" fields defined in Table 79–6b.

# Change Table heading for Table 79-6a and Table 79-6aa as follows:

Table 79-6a—Dual signature PD requested power value field for Mode A

Table 79-6aa — Dual-signature PD requested power value field for Mode B

# In 79.3.2.6c Power status section, add:

# 79.3.2.6c.1 PSE Powering Status

The PSE Powering Status field is used to indicate the existing powering configuration as shown in Table 145-41, and thus indicate that the PSE is using the PSE allocated power value field or is using the PSE allocated power value Alternative A field and PSE allocated power value Alternative B field as specified in Table 79-6b and Table 79-6ba. A PD shall set the field to 0.

#### 79.3.2.6c.2 PD Powered Status

The PD Powered Status field is used to indicate the existing powered configuration of the PD as shown in Table 145.42; and thus indicate that the PD is using the PD requested power value field or is using the PD requested power value Mode A field and the PD requested power value Mode B field as specified in Table 79-6a and 79-6aa. A PSE shall set the field to 0.

# Change Table 79-6c as follows:

Table 79-6c—Power status field

| Bit             | Function                              | Value/meaning                                                                                                                                                                             |

|-----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:1 <u>4</u> 2 | Reserved PSE Powering Status          | Transmit as zero. Ignore on receive.  15 14  1                                                                                                                                            |

| 13:12           | PD Powered Status                     | 13 12 1 1 = 4-pair powered Dual-Signature 1 0 = 2-pair powered Dual-Signature 0 1 = Powered Single-Signature 0 0 = Reserved/Ignore                                                        |

| 11:10           | PSE power pairsx                      | 11 10<br>1 1 = Both Alternatives<br>1 0 = Alternative B<br>0 1 = Alternative A<br>0 0 = Reserved/Ignore                                                                                   |

| 9:7             | Dual-signature<br>power Classx Mode A | 9 8 7<br>1 1 1 = Single-signature PD<br>1 1 0 = Reserved/Ignore<br>1 0 1 = Class 5<br>1 0 0 = Class 4<br>0 1 1 = Class 3<br>0 1 0 = Class 2<br>0 0 1 = Class 1<br>0 0 0 = Reserved/Ignore |

# 79.3.2.6e PSE maximum available power

Power via MDI

The PSE maximum available power field shall contain the highest power the PSE can grant as defined in Table 79–6e. The PSE shall set the value of this field taking available power budget and hardware capabilities into account. For dual-signature PDs this value refers to the total amount of power available at the PI, even though power is allocated separately on a per pairset basis.

# 79.4.2 IEEE 802.3 Organizationally Specific TLV/LLDP Local and Remote System group managed object class cross references

| Info (not part                 | Info (not part of baseline)               |                                                         |  |  |

|--------------------------------|-------------------------------------------|---------------------------------------------------------|--|--|

| This addresses                 | This addresses comment i-319 against D3.0 |                                                         |  |  |

| Add to Table 79–9              | as follows:                               |                                                         |  |  |

| TLV name                       | TLV variable                              | LLDP Local System Group managed object class attribute  |  |  |

| Power via MDI                  | Dual-signature power Classx Mode A        | aLldpXdot3LocPowerClassxA                               |  |  |

|                                | Dual-signature power Classx Mode B        | aLldpXdot3LocPowerClassxB                               |  |  |

|                                |                                           |                                                         |  |  |

| Add to Table 79–10 as follows: |                                           |                                                         |  |  |

| TLV name                       | TLV variable                              | LLDP Remote System Group managed object class attribute |  |  |

aLldpXdot3RemPowerClassxA

aLldpXdot3RemPowerClassxB

Dual-signature power Classx Mode A

Dual-signature power Classx Mode B