# Detection, Inrush, and Over-Current Loose Ends

**Andy Gardner**

#### **Presentation Objectives**

• Review and propose remedies for the portions of D1.3 pertaining to detection, inrush and output current that missing.

### **Detection and Inrush**

- Total time from start of detection to end of the PD's t<sub>power\_delay</sub> needs to be consistent with automotive fast start-up time requirement (less than 10ms).

- If possible, the standard should allow a class of PDs to exist with up to  $10\mu$ F C<sub>in</sub> during inrush in order to minimize cost and complexity.

- The PSE slew rate and maximum current during inrush need to be large enough to allow  $C_{PD}$  to be fully in-rushed during fast start-up.

•Example 0.2A/10 $\mu$ F = 20V/ms or ~3ms to ramp up V<sub>PD</sub> to 60V.

- In order for detection to be compatible with fast start-up, the minimum probe current may need to be increased in order to ramp from V<sub>sleep</sub> to V<sub>signature</sub> in a time that is consistent with the fast start-up requirement.

- •Need to define minimum  $V_{\text{signature}}$  hold time and maximum time for detection,  $t_{\text{DET}}$  max.

- •May need to consider shorter hold time for  $T_{Wakeup}$  (currently 1ms min).

#### Proposed Changes to Baseline Text for Detection and Power-Up

- 104.3.4.2 Detection criteria

- A PSE shall accept as a valid PD signature a link segment with a constant voltage in the range of V<sub>good\_PSE</sub> in response to a probing current in the range I<sub>valid</sub> for at least T<sub>vsig\_hold</sub> min as specified in Table 104–2.

- The PSE shall complete detection in less than  $T_{det}$  max when the PSE PI is pre-biased at  $V_{Sleep}.$

#### **Proposed Changes to Baseline Text for Detection and Power-Up Cont'd**

#### • 104.3.5 PSE classification of a PD and mutual identification

A PSE with SCCP enabled shall attempt to complete classification and mutual identification after detection and prior to applying application of full operating voltage power to the PI in a time less than T<sub>class</sub> as specified in Table 104-3. If classification is not completed before the T<sub>class</sub> timer expires, a new detection cycle shall be initiated before any subsequent application of full operating voltage.

#### • 104.3.6.5 Turn on time

The specification for T<sub>inrush</sub> T<sub>inrush\_max</sub> in Table 104–3 applies to the maximum PSE power up time for a PD after completion of detection. If power is not applied as specified, a new detection cycle shall be initiated before any subsequent application of power of full operating voltage.

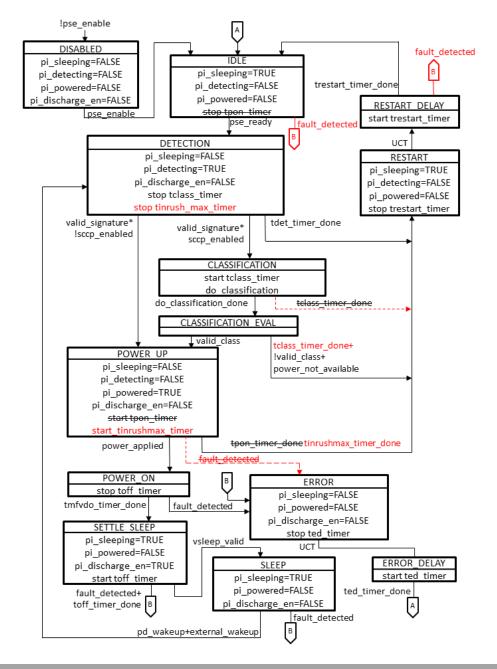

#### **Proposed State Diagram Changes for Detection, Classification, and Power-Up**

- Rename T<sub>pon</sub> as T<sub>inrush\_max</sub> and define it as the longest time POWER\_UP can last.

- Add fault\_detected arcs to the IDLE and RESTART\_DELAY states in order to force removal of sleep bias if the PSE is limiting current outside of the POWER\_ON state for longer than t<sub>LIM</sub>.

- Delete the tclass\_timer\_done exit arc from CLASSIFICATION state and add it as an additional OR'd condition to the exit arc out of the CLASSIFICATION\_EVAL state.

- Propose 300ms to 366ms as the maximum amount of time CLASSIFICATION and CLASSIFICATION\_EVAL can last before re-detection is required.

- Define do\_classification function to be the proposed classification function command sequence proposed in heath\_3bu\_1\_1015.pdf.

# Proposed PSE state diagram changes

- $T_{pon} \rightarrow T_{inrush\_max}$

- tclass\_timer\_done moves to arc to RESTART exiting CLASSIFICATION\_EVAL

- Arcs added for fault detected when not in POWER\_ON state

# V<sub>on</sub> and T<sub>powerdly</sub>

- T<sub>powerdly</sub> must be long enough to guarantee that the PD does not enable MDI\_POWER before inrush is complete.

- $\bullet$  T  $_{powerdly}$  begins when V  $_{PD}$  rises through V  $_{on}.$

- The draft currently defines V<sub>on</sub> max but not V<sub>on</sub> min!

- •Propose setting  $V_{on}$  min to 90% of  $V_{on}$  max as currently defined in the draft.

- T<sub>powerdly</sub> min must be long enough to ensure that inrush is complete before PD enables MDI power

- •Worst case spread occurs for 24V unregulated class where  $V_{on}$  min is 10.26V and  $V_{\text{PSE}}$  max is 36V.

- •Propose setting  $T_{powerdly}$  max = 1.22 ×  $T_{powerdly}$  min and making it uniform for all power classes

# Proposed Changes to Baseline Text for $V_{\text{on}}$ and $T_{\text{powerdly}}$

#### • 104.4.6.1 PD input voltage

- The PD shall turn on at a voltage less than or equal to V<sub>On</sub> after a delay in the range of t<sub>power\_dly</sub> as specified in Table 104–6. The PD shall turn off at a voltage greater than or equal to V<sub>Off</sub>.

- The PD shall turn on or off without startup oscillation and within the first trial for any valid load value when fed by V<sub>Port\_PSE</sub> min to V<sub>Port\_PSE</sub> max (as defined in Table 104-1) with a series resistance within the range of valid channel resistance.

## What's currently in the draft for I<sub>CUT</sub> and I<sub>LIM</sub>?

#### • $I_{CUT}$ and $T_{CUT}$

- +  $I_{\text{CUT}}$  range is  $P_{\text{Class}}/V_{\text{PSE}}$  to 2PClass/V\_{\text{PSE}}

- $\bullet~T_{CUT}$  range is 50ms to 75ms

- The cumulative duration of  $T_{CUT}$  is measured using a uniform sliding window of at least 1s width

- $\bullet$  Power shall be removed if the PSE current exceed  $I_{\text{CUT}}$  for longer than  $T_{\text{CUT}}$

#### • I<sub>LIM</sub>

- $\bullet~I_{\rm LIM}$  is listed in the Table 104-3 with a TBD limit.

- $\bullet$  There is no sub-clause which describes  $I_{\text{LIM}}.$

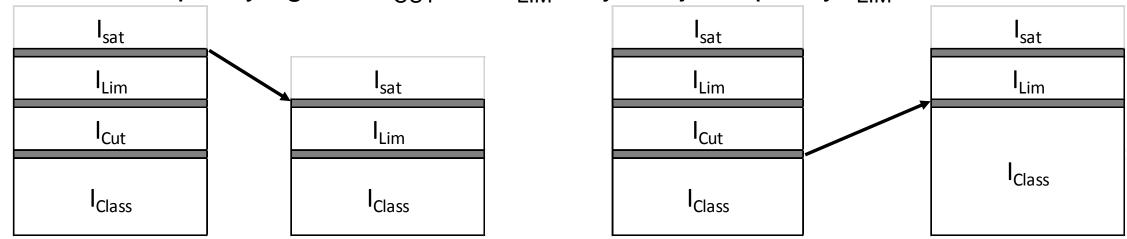

### What do we really need for overcurrent protection?

- For PoDL, class current comes at premium because of the technical challenges and relative cost associated with higher saturation current in the coupling inductors.

- Consequently, we want to minimize any overhead pertaining to over-current protection.

- Instead of specifying both  $I_{\text{CUT}}$  and  $I_{\text{LIM}}$  why not just specify  $I_{\text{LIM}}?$

Lower  $I_{Sat}$  for a given  $I_{Class}$  or...

...more  $I_{Class}$  for a given  $I_{Sat}$

# **Proposed Changes to Baseline Text for Output Current cont'd**

#### • Add 104.3.6.2.3 - Output current – at short circuit condition

- During operation in the POWER\_ON state, the PSE shall limit the current to  $I_{LIM}$  for a duration of up to  $T_{LIM}$  in order to account for PSE dV/dt transients at the PI as specified in Table 104-3.

- If I<sub>Port</sub> exceeds I<sub>LIM</sub> min during the POWER\_ON state, the PSE output voltage may drop below  $V_{PSE(PON)}$  min.

- During operation in any other state when the PSE is enabled, the PSE shall limit  $I_{Port}$  to less than  $I_{SC}$  as specified in Table 104-2 for a duration of up to  $T_{LIM}$ .

- If the PSE is limiting current in the POWER\_ON state or any state when  $V_{Sleep}$  is applied at the PI, power removal from the PI shall begin within  $T_{LIM}$ .

- Measurements of I<sub>Port</sub> during a short circuit condition shall be made 1ms after the initial transient to allow for settling.

#### • 104.3.6.4 Overload current

If I<sub>PORT</sub>, the current supplied by the PSE to the PI, exceeds I<sub>CUT</sub> for longer than T<sub>CUT</sub>, the PSE may remove power from the PI. The cumulative duration of T<sub>CUT</sub> is measured using a uniform sliding window of at least 1 second width.

## **Proposed Changes to Table 104-2**

| Item | Parameter                                                          | Symbol                    | Unit | Min   | Max          | Additional<br>Information |

|------|--------------------------------------------------------------------|---------------------------|------|-------|--------------|---------------------------|

| 3    | Valid test probe current                                           | <b>I</b> <sub>valid</sub> | mA   | 4-TBD | 10           |                           |

| 5    | Output<br>capacitance<br>during detection<br>and<br>classification | C <sub>out</sub>          | nF   |       | <b>4 200</b> |                           |

| 6    | Detection timing                                                   | T <sub>det</sub>          | ms   |       | TBD          |                           |

| 10   | Signature hold time                                                | T <sub>vsig_hold</sub>    | ms   | TBD   |              |                           |

### **Proposed Changes to Table 104-3**

| ltem | Parameter                                   | Symbol                  | Unit         | Min                                          | Мах                                                 | Class | Туре | Additional<br>Information        |

|------|---------------------------------------------|-------------------------|--------------|----------------------------------------------|-----------------------------------------------------|-------|------|----------------------------------|

| 3    | Output voltage dV/dt                        | dV <sub>PSE</sub> /dt   | V/ms         |                                              | <del>20</del> TBD                                   | All   | А    | See 104.3.6.1                    |

| 5    | Overload current<br>detection range         | <b>Ι</b> <sub>CUT</sub> | A            | ₽ <sub>Class</sub> /<br>∀ <sub>PSE</sub>     | <del>2xP<sub>Class</sub>/</del><br>∀ <sub>PSE</sub> |       |      | See 104.3.6.4                    |

| 6    | Overload time limit                         | ₽ <sub>CUT</sub>        | <del>S</del> | <del>0.050</del>                             | <del>0.075</del>                                    |       |      | See 104.3.6.4                    |

| 75   | Output current – at short circuit condition | I <sub>LIM</sub>        | A            | <del>TBD</del><br>I <sub>PI_Class(max)</sub> | TBD<br>1.22×I <sub>PI_Class(max)</sub>              |       |      | See 104.3.6.4<br>See 104.3.6.2.3 |

| 6    | Short circuit time limit                    | T <sub>LIM</sub>        | S            | 0.050                                        | 0.075                                               |       |      | See 104.3.6.2.3                  |

| 6    | Inrush time                                 | ∓ <sub>inrush</sub>     | <del>S</del> | ŦBD                                          |                                                     |       |      | See 104.3.6.6                    |

| 8    | Maximum inrush time                         | T <sub>inrush_max</sub> | S            | TBD                                          | TBD                                                 |       |      | See 104.3.6.2.2                  |

| 10   | Maximum<br>classification time              | T <sub>class</sub>      | ms           | 300                                          | 366                                                 |       |      | See 104.3.5                      |

| 17   | Wakeup current hold time for validity       | T <sub>Wakeup</sub>     | ms           | 4 <i>TBD</i>                                 |                                                     |       |      | See 104.3.6.5.1                  |

### **Proposed changes to Table 104-6**

| Item            | Parameter                                                  | Symbol                | Unit | Min  | Max             | PD Type | Additional<br>Information |

|-----------------|------------------------------------------------------------|-----------------------|------|------|-----------------|---------|---------------------------|

| 4a              | Power supply turn on voltage (unregulated 12 V classes)    | V <sub>on</sub>       | V    | 5.18 | 5.75            |         | See<br>104.4.6.1          |

| 4b              | Power supply turn on voltage (regulated 12 V classes)      |                       |      | 12.2 | 13.6            |         |                           |

| 4c              | Power supply turn on voltage (unregulated 24 V classes)    |                       |      | 10.3 | 11.4            |         |                           |

| 4d              | Power supply turn on voltage (regulated 24 V classes)      |                       |      | 17.8 | 24.7            |         |                           |

| 4 <del>e</del>  | Power supply turn on voltage<br>(unregulated 48 V classes) |                       |      |      | <del>22.8</del> |         |                           |

| 4 <del>fe</del> | Power supply turn on voltage (regulated 48 V classes)      |                       |      | 38.4 | 45.6            |         |                           |

| 7               | Inrush enable delay time                                   | t <sub>powerdly</sub> | ms   | 1.46 | 1.78            |         |                           |

### Proposed changes to Table 104-6 con'td

| lte<br>m         | Parameter                                                                               | Symb<br>ol      | Unit | Min | Max | PD<br>Type | Addition<br>al<br>Informati<br>on |

|------------------|-----------------------------------------------------------------------------------------|-----------------|------|-----|-----|------------|-----------------------------------|

| 6 <mark>a</mark> | Input capacitance<br>during detection and<br><del>classification states</del><br>inrush | C <sub>PD</sub> | uF   |     | TBD |            |                                   |

| 6b               | Input capacitance<br>during classification                                              |                 | μF   |     | 0.2 |            |                                   |

### Conclusion

- Remedies for missing portions in draft 1.3 pertaining to detection, inrush, and current limit were presented.

- Remaining TBDs need to be addressed by gardner\_3bu\_2\_1015.

#### **Questions?**

18