# 802.3cb Test Points Proposal

Anthony Calbone 1/20/2016

#### Supporters

- Rich Mellitz, Intel

- William Lo, Marvell

- Peter Wu, Marvell

- Thomas Skaar, Seagate

- Dan Smith, Seagate

#### Introduction

#### The goal is to adopt a baseline for test point definition

- These will be used as a baseline reference to build upon. The loss budgets and tests associated with each test

point will be based on these test points.

- There are two different models shown in the presentation that use 802.3bj as a starting point

- A backplane reference model that is a generic model that could be a closed and/or proprietary system in which the only loss budget is ball-to-ball

- A storage reference model that is more focused and allows for insertion loss budgeting of the HDD since it's an external interface

- The ball-to-ball budgets are equivalent between the two models

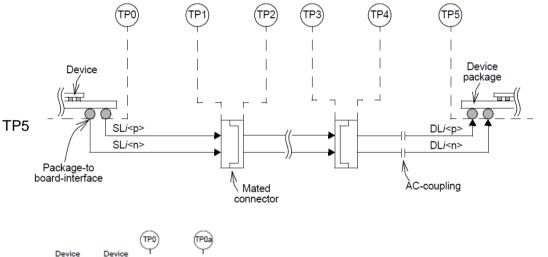

# Chip Spec

- Channel is measured from TP0 to TP5

- Package ball to package ball

- Device Tx is measured at TP0a

- TP0 is not observable in an implemented system

- Device Rx is measured at TP5a

- TP5 is not observable in an implemented system

- Receiver Interference Tolerance Test is calibrated at TP5

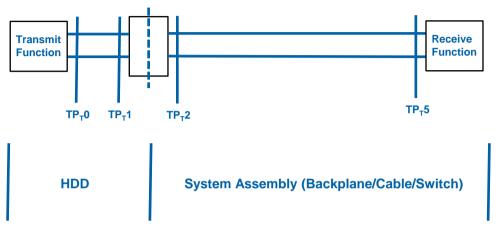

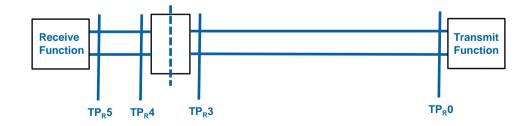

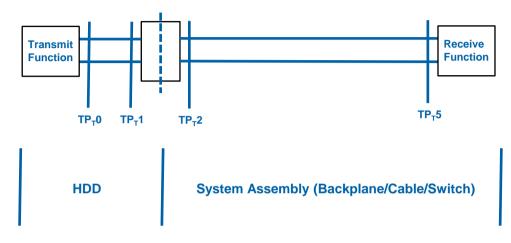

# **Storage Device Spec**

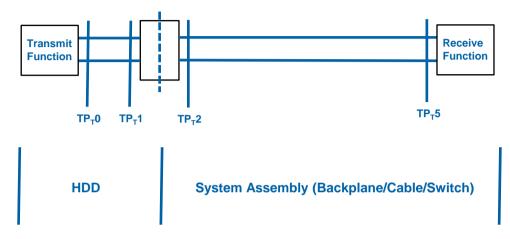

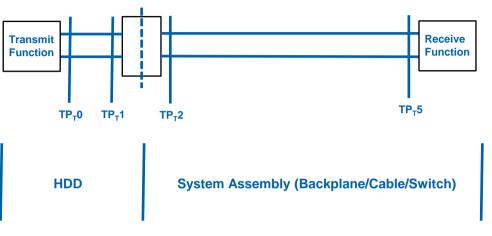

- For the storage application, it's important to budget the drive loss since it's an external component.

- The rest of the "box" is vender specific and can be any combination of cable and backplane

- This implies a Storage Reference Model with an asymmetric loss budget

- Informative insertion loss would be the same as in the backplane reference model

- For storage device (HDD)

- Tx is measured at TP<sub>T</sub>2, after the mated connecter

- Receiver Interference Tolerance Test is calibrated at TP<sub>T</sub>4

- For host chip

- Use pin to pin spec for compliance

- Tx is measured at TP0a

- Receiver Interference Tolerance Test is calibrated at TP5

### Storage Device Spec Cont'd

#### Channel

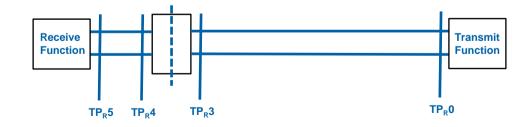

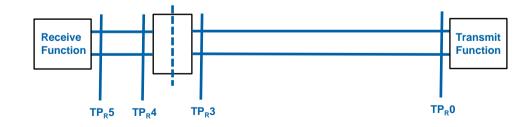

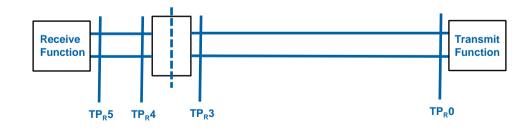

- Informative storage device loss from  $TP_T0$  to  $TP_T1$  and  $TP_R4$  to  $TP_R5$

- Informative system loss from  $TP_T1$  to  $TP_T5$  and  $TP_R0$  to  $TP_R4$

- Channel is measured from  $TP_T 1$  to  $TP_T 5$  and  $TP_R 0$  to  $TP_R 4$

- Channel loss is extrapolated from  $TP_T1$  to  $TP_T0$  and from  $TP_R4$  to  $TP_R5$  using COM

# **Storage Device Test Point Definitions**

- $TP_T0$  to  $TP_T5$  and  $TP_R0$  to  $TP_R5$

- The channel including all insertion loss between package balls

- This includes the HDD and system loss

- This loss would be equivalent to the chip spec loss

- $TP_T1$  to  $TP_T5$  and  $TP_R0$  to  $TP_R4$

- Measurement of storage system is done between these points.

- $TP_T0$  to  $TP_T1$  and  $TP_R4$  to  $TP_R5$

- Recommended maximum insertion loss of the storage device PCB traces

- TP<sub>T</sub>2

- Storage device transmitter compliance point

- TP0a is not applicable to a storage device

- TP<sub>T</sub>2 is observable in an implemented storage device

- TP<sub>R</sub>3

- Storage device receiver compliance point

- TP5a is not applicable to a storage device

- TP<sub>R</sub>3 is observable in an implemented storage device

# Storage Device Test Point Definitions Cont'd

- TP<sub>R</sub>4

- Receiver Interference Tolerance Test calibration point

- The storage device must be compliant with the delivered signal at  $\ensuremath{\mathsf{TP}_\mathsf{R}}4$

- $TP_R1$  to  $TP_T2$  and  $TP_R3$  to  $TP_R4$

- Recommended mated connector pair fixture loss