# PreFEC BER Signaling Features

David Ofelt – Juniper Networks Pete Anslow – Ciena Mark Gustlin – Xilinx Gary Nicholl – Cisco 2016-07 : San Diego, CA

### Supporters

### Background

- We added PreFEC BER monitoring features to 802.3bs

- History:

- maki 3bs 01a 1115.pdf Background and Justification

- ofelt 3bs 01a 0116.pdf Initial proposal

- ofelt 3bs 01 0316.pdf

- ofelt 3bs 01 0416 logic.pdf

- ofelt 3bs 01 0516.pdf

- The features are interesting for many of the usecases in 802.3cd

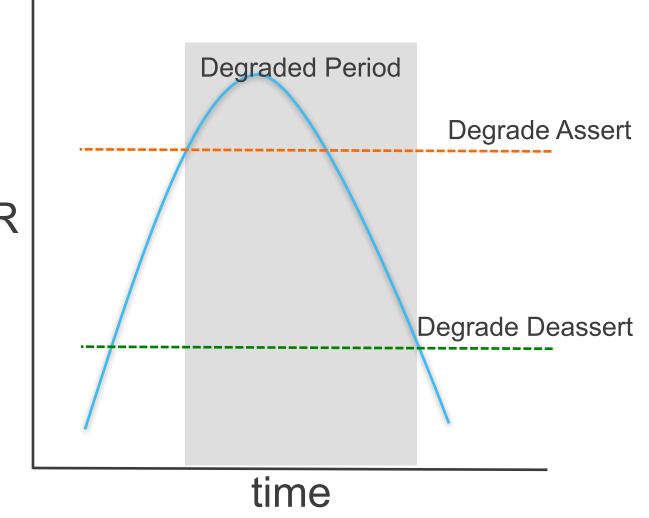

### PreFEC Degrade

- Degrade

- Separate activate and de-activate threshold with shared interval

- Set if corrected symbols in Period is more than the Assert threshold

BER

- Cleared if corrected symbols in Period is less than the Deassert threshold

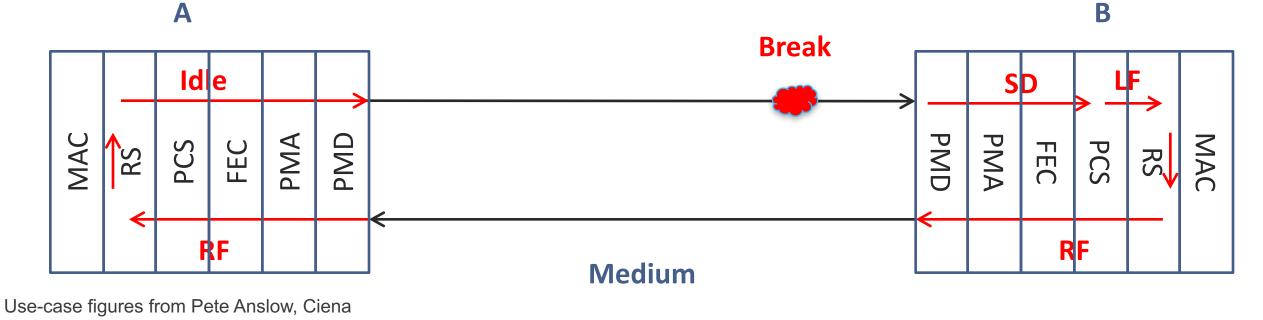

### Existing local fault / remote fault

- PMD Rx at B sets SIGNAL\_DETECT (SD) to FAIL

- PCS at B sends local fault (LF) to RS at B

- RS at B sends remote fault (RF) to A

- RS at A receives RF and sends all idle characters

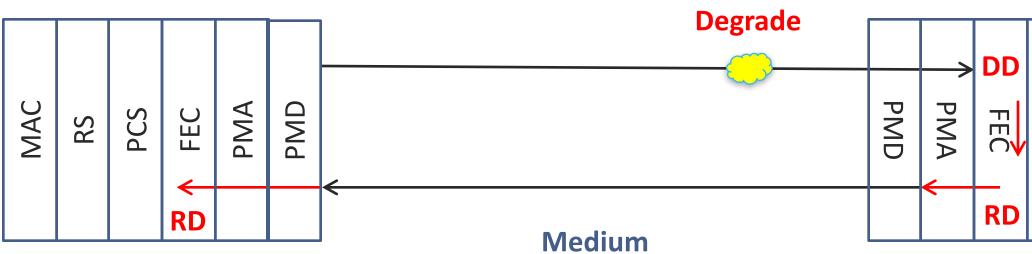

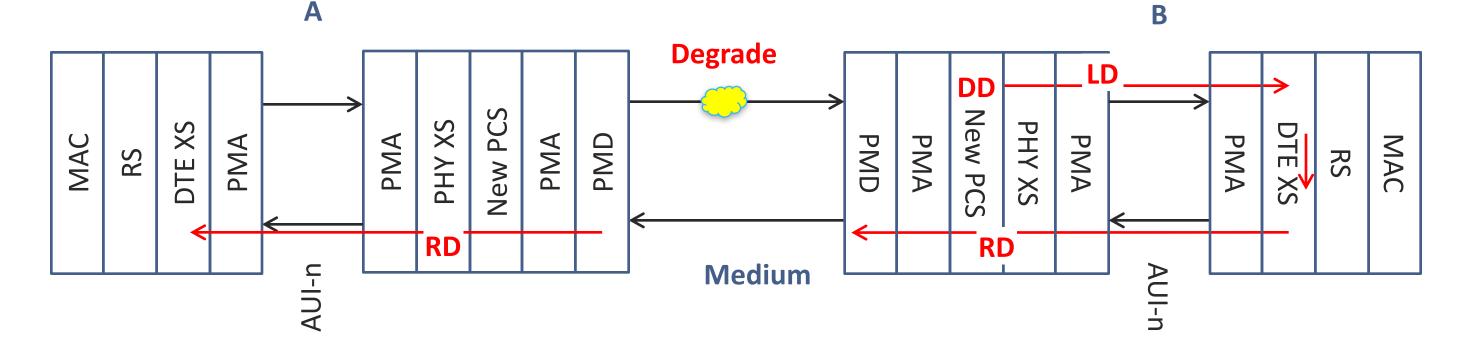

### Pre-FEC degrade FEC integrated in host ASIC Α B

- FEC at B exceeds pre-FEC symbol error ratio (SER) threshold and detects degrade (DD)

- FEC at B sends remote degrade (RD) to PCS at A

- Traffic unaffected

- Is the PCS involved at all?

| PCS | RS | MAC |

|-----|----|-----|

|-----|----|-----|

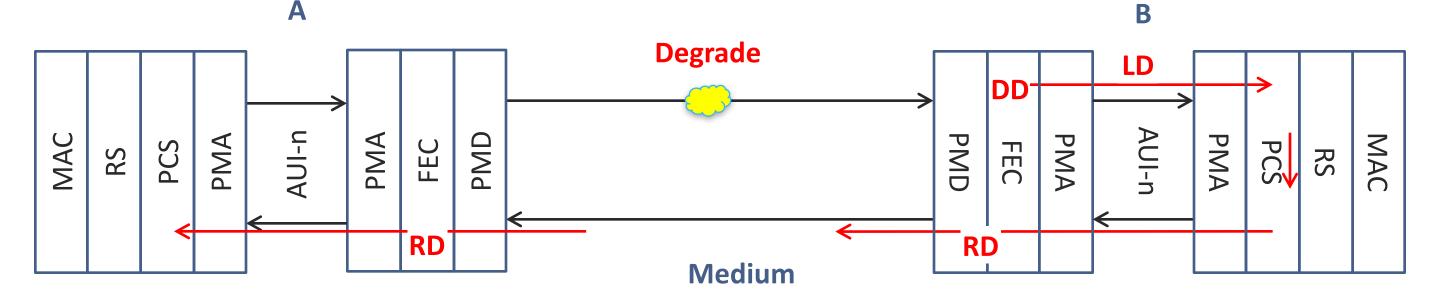

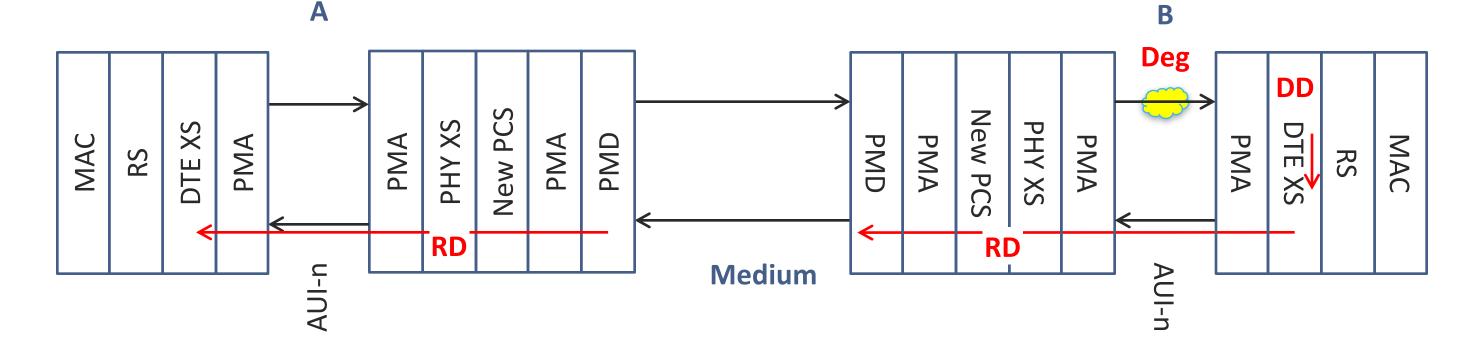

## Pre-FEC degrade legacy host ASIC

- External FEC at B exceeds pre-FEC symbol error ratio (SER) threshold and sends local degrade (LD) to PCS at B

- DTE XS at B sends remote degrade (RD) to PCS at A

- Traffic unaffected

- Unclear how to signal over the AUI since legacy is defined

- Punt?

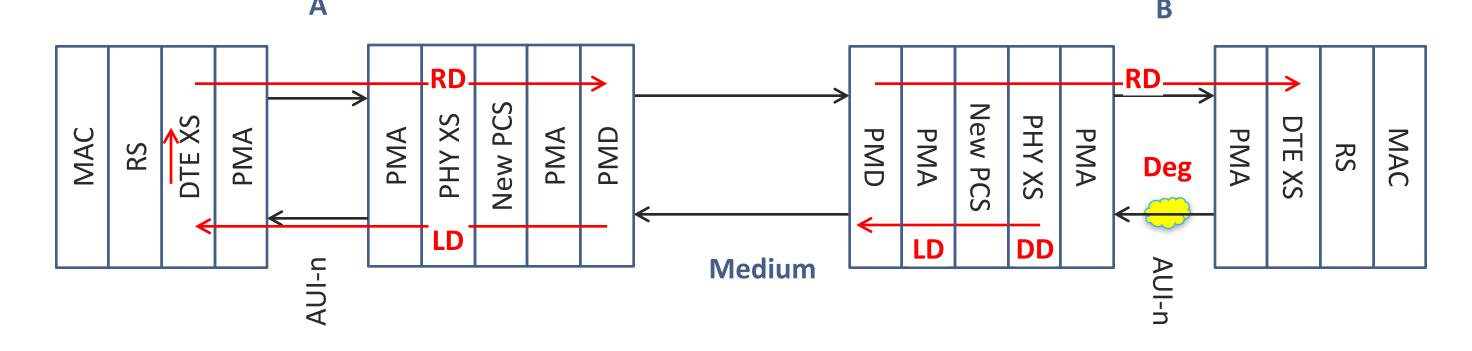

## .3bs Pre-FEC degrade with extender sublayer 1

- New PCS at B exceeds pre-FEC symbol error ratio (SER) threshold and sends local degrade (LD) to DTE XS at B

- DTE XS at B sends remote degrade (RD) to DTE XS at A

- Traffic unaffected

## .3bs Pre-FEC degrade with extender sublayer 2

- DTE XS at B exceeds pre-FEC symbol error ratio (SER) threshold and sends remote degrade (RD) to DTE XS at A

- Traffic unaffected

## .3bs Pre-FEC degrade with extender sublayer 3

- PHY XS at B exceeds pre-FEC symbol error ratio (SER) threshold and sends local degrade (LD) to DTE XS at A

- Traffic unaffected

Α

### Scope of the changes

- 802.3bs Changed:

- PCS clause (119)

- Extender Sublayer Clause (118)

- Added Management registers & bits (45)

- For 802.3cd:

- Propose adding the same PreFEC features to appropriate .3cd clauses

- Open questions on what the separate FEC sublayer does for this feature

- External FEC sublayer with legacy ASIC hard to support, since host is by definition done

- Extender sublayer may still be interesting for future PMDs or transport handoff

- Need a place to put the LD/RD bits in the alignment markers

- 3 bits total LD, RD, and a bit allowing for future expansion

### d clauses his feature s by definition done rt handoff

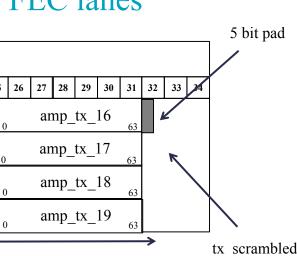

### 100GbE in-band LD/RD bits

- Can use last 3 bits of existing 5 bit pad

- Assuming no clock content issues as we did in .3bs

### NG 100GbE - Alignment Marker mapping to FEC lanes

| FEC<br>Lane | Reed-Solomon symbol index, k (10-bit symbols) |   |     |      |   |   |      |             |     |      |          |    |    |  |    |

|-------------|-----------------------------------------------|---|-----|------|---|---|------|-------------|-----|------|----------|----|----|--|----|

|             | 0                                             | 1 | 2   | 3    | 4 | 5 | 6    | 7           | 8   | 9    | 10       | 11 | 12 |  | 25 |

| Lane 0      | amp_tx_0 63                                   |   |     |      |   |   | 63 0 | amp_tx_4 63 |     |      |          |    |    |  |    |

| Lane 1      | amp_tx_1                                      |   |     |      |   |   | 3 0  |             | amj | p_tx | <u>5</u> |    | 63 |  |    |

| Lane 2      | amp_tx_2 63                                   |   |     |      |   |   | 53 0 | amp_tx_6    |     |      |          |    |    |  |    |

| Lane 3      | 0                                             | a | mp_ | _tx_ | 3 | 6 | 53 0 |             | amj | p_tx | ĸ_7      |    | 63 |  |    |

|             | /                                             |   |     |      |   |   |      |             |     |      |          |    |    |  |    |

start of FEC codeword

5 x 257-bit alignment marker block (including 5 bit pad)

- Based on Clause 91. Exact AM mapping still TBD

- Initial analysis indicates that Clause 91 AM mapping needs to be modified to avoid clock content issues with repeating AM0 and AM16 patterns when bit muxing FEC lanes.

From nicholl 3cd 01 0716.pdf

### 50GbE in-band LD/RD bits

- Not enough pad bits to make things easy

- BIP is not useful with FEC

- Should we harvest BIP bits?

- If so- which ones?

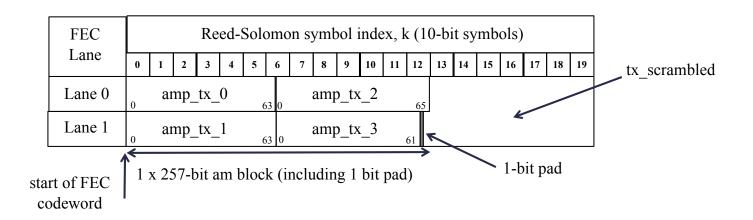

50GbE - Alignment Marker mapping to FEC lane

- Based on Clause 91 mapping, but modified to support 4 PCS lanes, 2 FEC lanes and to enable bit muxing of FEC lanes

- Exact AM mapping still TBD

- Note: amp tx 0, amp tx 1 = 64 bits, amp tx 2 = 66 bits, amp tx 3 = 62 bit

From nicholl 3cd 01 0716.pdf

15

### Summary

- Proposed adding the PreFEC BER feature from .3bs to .3cd

- Most details should be easily ported

- Questions about impact of separate FEC layer and if we need/want an extender sublayer.

- Signaling bits

- 100GbE has a natural place for the new signaling bits

- Some work needed to find signaling bits for 50GbE

# Thanks