IEEE 802.3cg Unbalanced PLCA Issue September 2018

#### Unbalanced PLCA Issue

#### **Contributors**

Michael Rentschler, Microchip Venkat Iyer, Microchip Dixon Chen, Microchip

**Supporters**Piergiorgio Beruto, Canova Tech

## Introduction

#### PLCA test environment:

- 2 nodes (A and B) with PLCA enabled

- MACs (A and B) keep sending back to back

#### The issue we see:

- Sometimes, the pattern is ABB instead AB

- Results in a 1:2 bandwidth ratio instead 1:1

- unbalanced bandwidth distribution w/ PLCA

### **Unbalanced Bandwidth**

#### The pattern we expect to see:

| Bus cycle | 1   |     | 2   |     | 3   |     | 4   |     | 5   |     | 6   |     | 7   |     | 8   |     |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ТО        | Α   | В   | Α   | В   | Α   | В   | Α   | В   | Α   | В   | Α   | В   | Α   | В   | Α   | В   |

| Node A    | TX  | COL |

| Node B    | COL | TX  |

#### What we see instead, is:

| Bus cycle | 1   |    | 2 |     | 3   |    | 4 |     | 5   |    | 6 |     | 7   |    | 8 |     |

|-----------|-----|----|---|-----|-----|----|---|-----|-----|----|---|-----|-----|----|---|-----|

| ТО        | Α   | В  | A | В   | Α   | В  | A | В   | Α   | В  | A | В   | Α   | В  | A | В   |

| Node A    | TX  | -  | - | COL |

| Node B    | COL | TX | - | TX  |

→ An unevenly balanced bandwidth distribution like this would circumvent the usability of PLCA for many fields, even if collisions will still be avoided!

## **Root Cause**

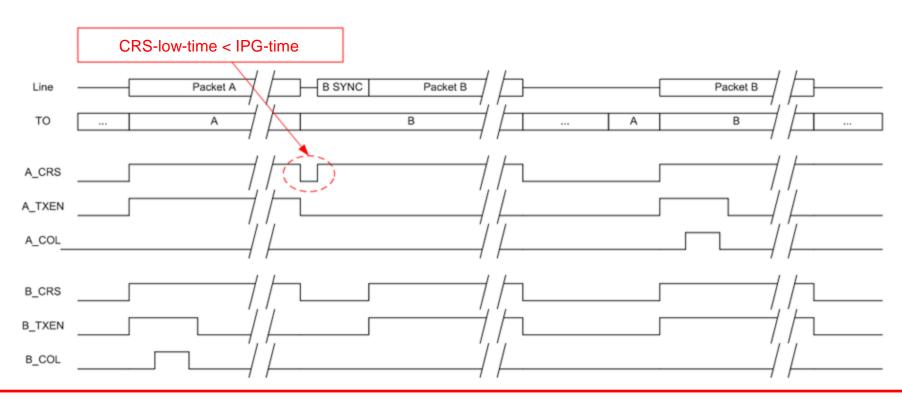

- According to the current spec, PLCA RS will de-assert CRS only for a short time, smaller than the required minimal IPG time

- MAC of node A will not be capable to start transmission of its next pending packet during this period, and may lose its next TO

# **Proposal**

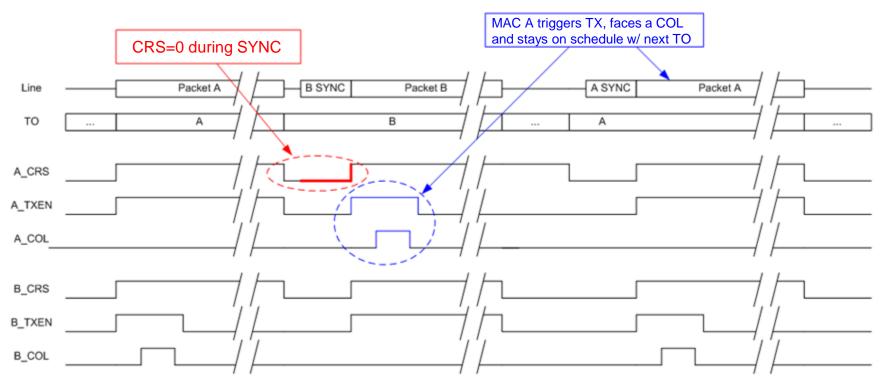

- Always de-assert CRS between two adjacent packets for at least the min. IPG time

- We can achieve this by keeping CRS de-asserted also during the PLCA SYNC period

# Resulting Spec Change

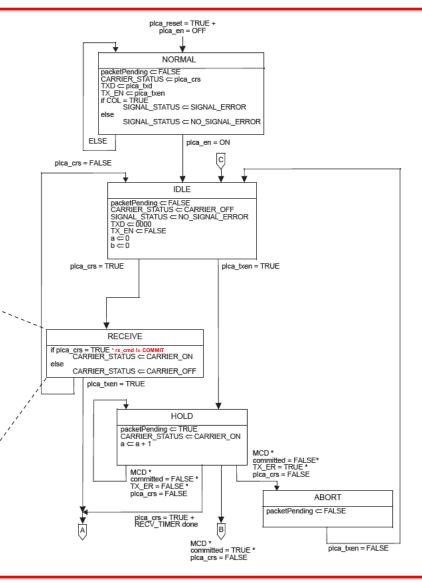

- In Figure 148-6 (IEEE Draft P802.3cg/D2.0)

- Change "if plca\_crs = TRUE"

- to "if plca\_crs = TRUE \* rx\_cmd != COMMIT"

- Also see comment #613

####

## Conclusion

We were able to validate that the proposed solution will fix the unbalanced behavior of PLCA

This issue was also seen by Canova Tech and they agreed on the proposed spec change

# **Thank You!**