## PIERGIORGIO BERUTO ANTONIO ORZELLI

IEEE 802.3cg

PLCA Burst mode fixes

November 28th, 2018

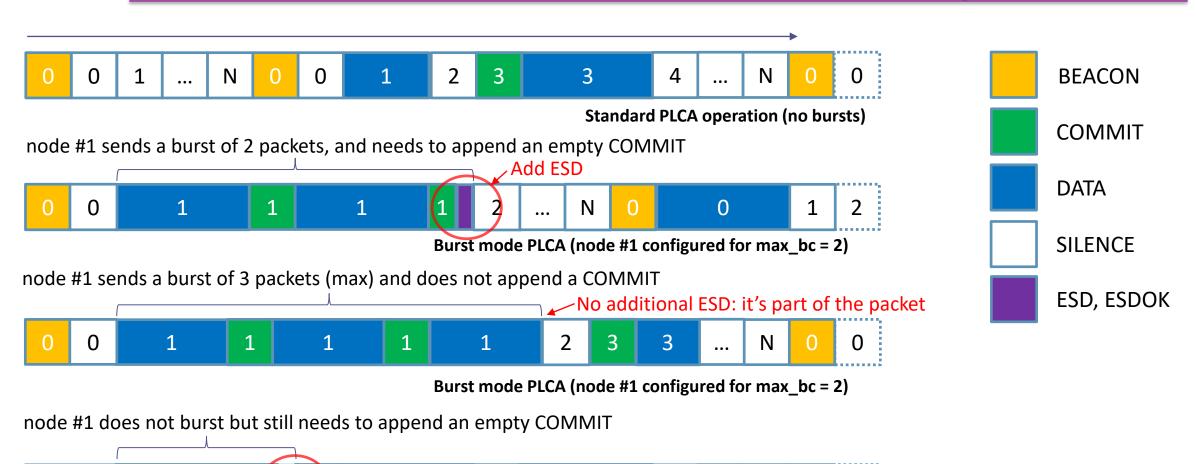

- PLCA burst mode has been added to Clause 148 in draft 2.2 as per <a href="http://www.ieee802.org/3/cg/public/Nov2018/beruto-3cg-PLCA-burst-mode-revB%20.pdf">http://www.ieee802.org/3/cg/public/Nov2018/beruto-3cg-PLCA-burst-mode-revB%20.pdf</a>.

- The addition of this new feature created a (minor) problem in Clause 147

- A COMMIT (coded as 'J' in 4B/5B) is added at the end of a packet when burst mode is enabled

- Such COMMIT can be followed by either a packet or silence.

- In the latter case the PCS RX signals a "False carrier" on the MII

- This is not supposed to happen since it's normal burst mode behavior

Slide 2

- Besides, there was one missing change for Clause 148

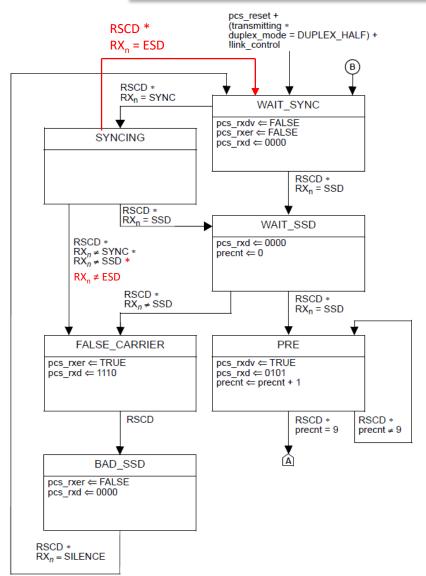

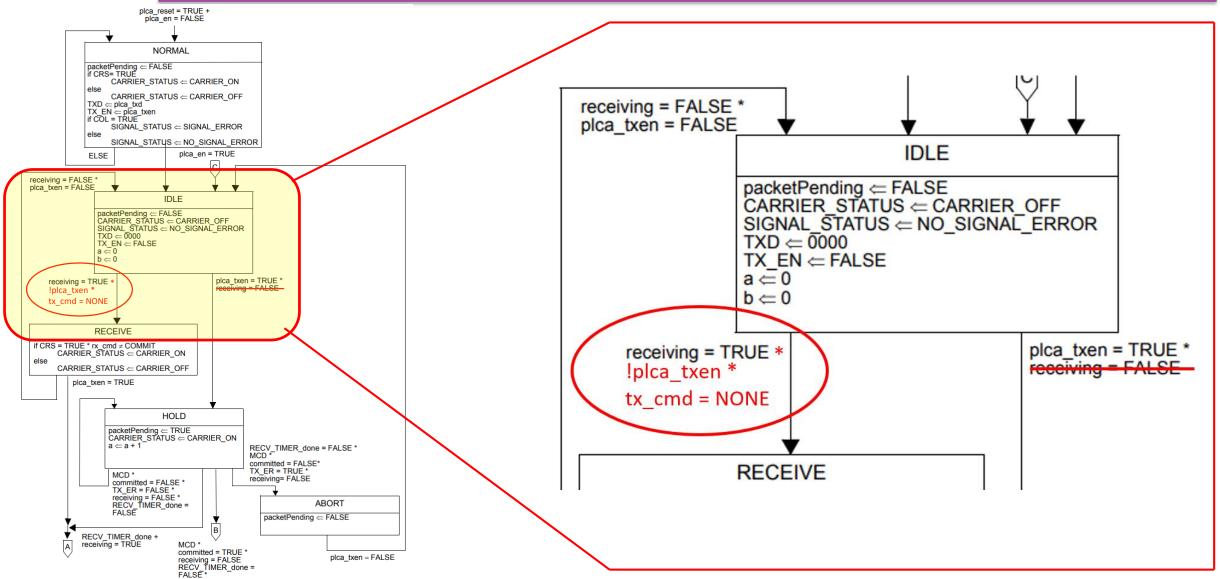

- Depending on implementation (internal delays), PLCA DATA State Diagram could detect a false reception when filling the IPG with idle.

- Use explicit ESD, ESDOK 5B symbol sequence to end a COMMIT request when the MAC has no more packets to send in a burst

- This prevents the spurious "FALSE carrier" indication

- Increase minimum DME silence period to guarantee at least one full 5B symbol of silence afterwards

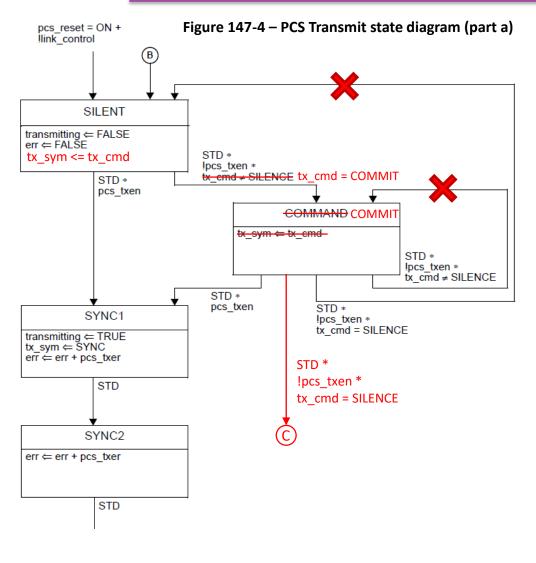

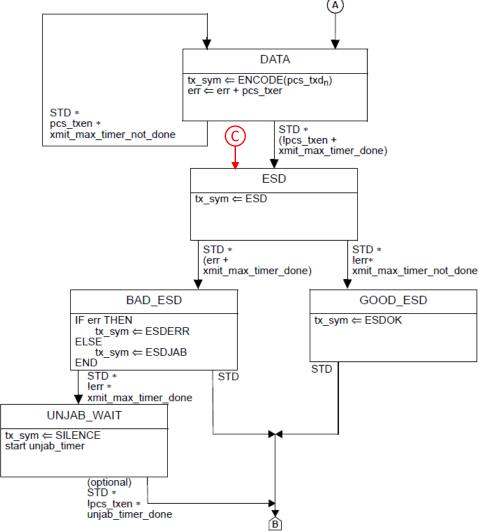

- State diagram fix to Clause 147

- The number of changes may look significant but the actual *—functional—* modification is very limited

- State diagram fix to Clause 148

#### Proposed solution

3

4

Burst mode PLCA (node #1 configured for max\_bc = 2)

Ν

0

0

Add ESD

3

### PCS TX state diagram changes

Figure 147-4—PCS Transmit state diagram (part b)

#### PMA and PCS RX state diagram changes

Figure 147-7—PCS Receive state diagram (part a)

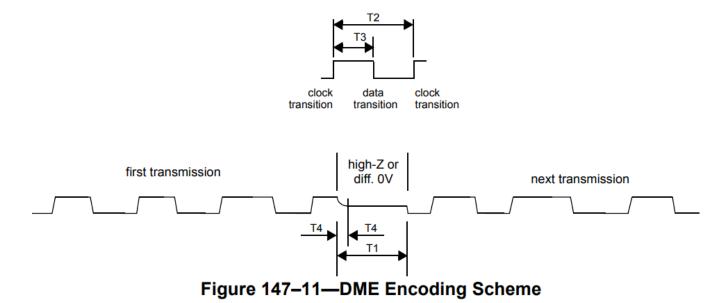

Table 147–2—DME Timings

| Parameter<br>name | Description                                    | Minimum<br>value    | Nominal<br>value | Maximum<br>value | Unit of<br>measure |

|-------------------|------------------------------------------------|---------------------|------------------|------------------|--------------------|

| T1                | Delay between transmissions                    | <del>-200</del> 480 | _                | _                | ns                 |

| T2                | Clock transition to clock transition           | -100 ppm            | 80               | +100 ppm         | ns                 |

| T3                | Clock transition to data transition (data = 1) | 38                  | 40               | 42               | ns                 |

#### 480 ns is one 5B symbol + 1 DME encoded bit

#### PLCA DATA state diagram changes

Figure 148-5—PLCA DATA state diagram

# THANK YOU!