# Baseline for 149.4.2.4

# Start from 97.4.2.4

### 97149.4.2.4 PHY Control function

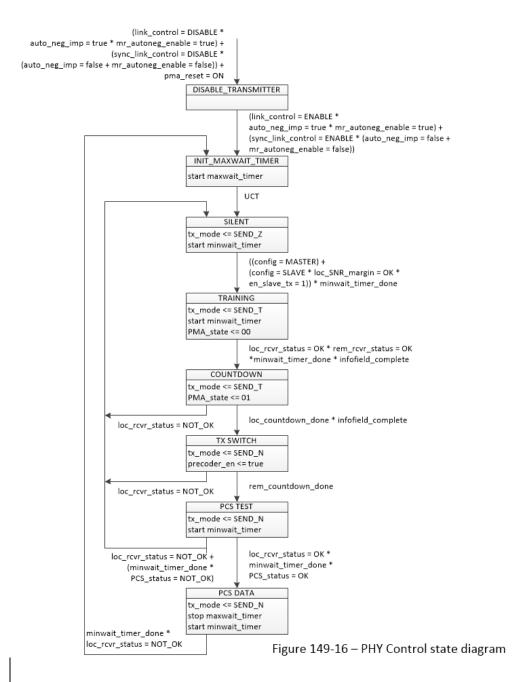

PHY Control generates the control actions that are needed to bring the PHY into a mode of operation during which frames can be exchanged with the link partner. PHY Control shall comply with the state diagram description given in Figure 97–26149-16.

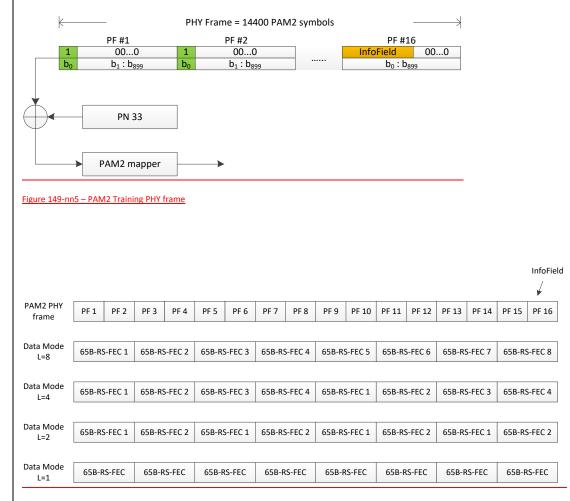

During PMA training (TRAINING and COUNTDOWN states in Figure 97–26149-16), PHY Control information is exchanged between link partners with a 12-octet InfoField, which is XORed with the first 96 bits of the <u>15th-16th</u> partial PHY frame (bits <u>2520-13500</u> to <u>261513595</u>) of the PHY frame. The InfoField is also denoted IF. The link partner is not required to decode every IF transmitted but is required to decode IFs at a rate that enables the correct actions prior to the PAM2 to <u>PAM3-PAM4</u> transition.

The 12-octet InfoField shall include the fields in 97149.4.2.4.2 through 97149.4.2.4.8, also shown in the overview Figure 97-20149-nn1, and the more detailed Figure 97-21149-nn2 and Figure 97-22149-nn3. Each InfoField shall be transmitted at least 256 times to ensure detection at link partner.

#### [Editor note: Copy Figure 97-20 as Figure 149-nn1, Figure 97-21 as Figure 149-nn2, and Figure 97-22 as Figure 149-nn3.]

| octet 1 | octet 2 | octet 3 | octet 4/5/6 | octet 7       | c | octet 8/9/10 | D     | octet 11/12 |  |  |  |  |

|---------|---------|---------|-------------|---------------|---|--------------|-------|-------------|--|--|--|--|

| 0xBB    | 0xA7    | 0x00    | PFC24       | Message MSG24 |   | MSG24        | MSG24 | CRC16       |  |  |  |  |

Figure 149-nn1 – InfoField format

| octet 1 | octet 2 | octet 3 | octet 4/5/6 | octet 7 | octet 8/9/10 | octet 11/12 |

|---------|---------|---------|-------------|---------|--------------|-------------|

| 0xBB    | 0xA7    | 0x00    | PFC24       | Message | UsrCfgCap    | CRC16       |

Figure 149-nn2 – InfoField TRAINING format

|   | octet 1 | octet 2 | octet 3 | octet 4/5/6 | octet 7 | octet 8/9/10 | octet 11/12 |

|---|---------|---------|---------|-------------|---------|--------------|-------------|

| [ | 0xBB    | 0xA7    | 0x00    | PFC24       | Message | DataSwPFC24  | CRC16       |

Figure 149-nn3 - InfoField COUNTDOWN format

#### 97149.4.2.4.1 InfoField notation

For all the InfoField notations in the following subclauses, Reserved<bit location> represents any unused values and shall be set to zero on transmit and ignored when received by the link partner. The InfoField is transmitted following the notation described in 97.3.2.2.3 where the LSB of each octet is sent first and the octets are sent in increasing number order (that is, the LSB of Oct1 is sent first).

## 97149.4.2.4.2 Start of Frame Delimiter

The start of Frame Delimiter consists of 3 octets [Oct1<7:0>, Oct2<7:0>, Oct3<7:0>] and shall use the hexadecimal value 0xBBA700. 0xBB corresponds to Oct1<7:0> and so forth.

#### 97149.4.2.4.3 Partial PHY frame Count (PFC24)

The start of partial PHY frame Count consists of 3 octets [Oct4<7:0>, Oct5<7:0>, Oct6<7:0>] and indicates the running count of partial PHY frames sent LSB first. There are <u>15-16</u> partial PHY frames per PHY frame and the InfoField is embedded within the <u>15th-16th</u> partial PHY frame. The first partial PHY frame is zero, thus the first partial PHY frame count field after a reset is <u>1415</u>.

#### 97149.4.2.4.4 Message Field

Message Field (1 octet). For the MASTER, this field is represented by Oct7{PMA\_state<7:6>, loc\_rcvr\_status<5>, en\_slave\_tx<4>, reserved<3:0>}. For the SLAVE, this field is represented by Oct7{PMA\_state<7:6>, loc\_rcvr\_status<5>, timing\_lock\_OK<4>, reserved<3:0>}.

The two state-indicator bits PMA\_state<7:6> shall communicate the state of the transmitting transceiver to the link partner. PMA\_state<7:6> = 00 indicates TRAINING, and PMA\_state<7:6> = 01 indicates COUNTDOWN.

All possible Message Field settings are listed in Table 97–7149-tt1 for the MASTER and Table 97–8149-tt2 for the SLAVE. Any other value shall not be transmitted and shall be ignored at the receiver. The Message Field setting for the first transmitted PMA frame shall be the first row of Table 97–7149-tt1 for the MASTER and the first or second row of Table 97–8149-tt2 for the SLAVE. Moreover, for a given Message Field setting, the next Message Field setting shall be the same Message Field setting or the Message Field setting corresponding to a row below the current setting. When loc\_rcvr\_status = OK the InfoField variable is set to loc\_rcvr\_status<5> = 1 and set to 0 otherwise.

[Editor note: Copy Table 97-7 as Table 149-tt1, and Table 97-8 as Table 149-tt2.]

#### Table 149-tt1 - InfoField message field valid MASTER settings

| PMA_state<7:6> | loc_rcvr_status | en_slave_tx | reserved | reserved | reserved | reserved |

|----------------|-----------------|-------------|----------|----------|----------|----------|

| 00             | 0               | 0           | 0        | 0        | 0        | 0        |

| 00             | 0               | 1           | 0        | 0        | 0        | 0        |

| 00             | 00 1            |             | 0        | 0        | 0        | 0        |

| 01 1           |                 | 1           | 0        | 0        | 0        | 0        |

#### Table 149-tt2 - InfoField message field valid SLAVE settings

|  | PMA_state<7:6> | loc_rcvr_status | timing_lock_OK | reserved | reserved | reserved | reserved |

|--|----------------|-----------------|----------------|----------|----------|----------|----------|

|  | 00 0<br>00 0   |                 | 0              | 0        | 0        | 0        | 0        |

|  |                |                 | 1              | 0        | 0        | 0        | 0        |

|  | 00             | 1               | 1              | 0        | 0        | 0        | 0        |

|  | 01             | 1               | 1              | 0        | 0        | 0        | 0        |

### 97<u>149</u>.4.2.4.5 PHY Capability Bits<del>, User Configurable Register,</del> and Data Mode Scrambler Seed

When PMA\_state<7:6> = 00, then [0ct8<7:0>, 0ct9<7:0>, 0ct10<7:0>] contains the two PHY capability bits, the user configurable register bits, and the 15-bit data mode scrambler seed (Seed). Each octet is sent LSB first.

As shown in Figure 149-nn4, Fthe format of PHY capability bits is Oct9<7> = EEEen, -and-Oct10<0> = OAMen, Oct10<2:1> = InterleaverDepth, and Oct10<4:3> = PrecodeSel.

EEEen and OAMen indicate ing EEE and 1000BASE-T1 OAM capability enable, respectively. The PHY shall indicate the support of these two optional capabilities by setting the corresponding capability bits.

InterleaveDpeth indicates the requested data mode interleaving depth and PrecodeSel indicates the requested data mode precoder.

The data mode scrambler seed contains bits S14 (sent first) to S0 (sent last) to indicate the initial state of the data mode transmit scrambler of the local device upon reaching the data switch partial PHY frame count. The state of the scrambler in Figure  $\frac{97-9149-nn5}{97-9149-nn5}$  shall be S14:S0 at the first bit of the first PHY frame when the partial PHY frame counter equals to the DataSwPFC24 value, see  $\frac{97.4.2.4.6149.xyz}{97-9149-nn5}$ . The format of Seed is Oct8<7:0> = S<7:14> and Oct9<6:0> = S<0:6>. Seed S<14:0> shall not be all zeros.

The remaining 73-bit Oct10<7:15> form a user-configurable register. See 97.4.2.4.11 for details shall be reserved and set to 0.

| octet 8     | octet 9 |      |   |   |   |   | octet 10 |   |       |       |      |             |   |            |          |          |          |

|-------------|---------|------|---|---|---|---|----------|---|-------|-------|------|-------------|---|------------|----------|----------|----------|

| 0 1 2 3 4 5 | 6 7     | 0    | 1 | 2 | 3 | 4 | 5        | 6 | 7     | 0     | 1    | 2           | 3 | 4          | 5        | 6        | 7        |

| (0          |         | Seed |   |   |   |   |          |   | EEEen | OAMen | epth | InterleaveD |   | DrecodeCel | Reserved | Reserved | Reserved |

Figure 149-nn4 – PHY Capability Bits and Data Mode Scrambler Seed

#### 97149.4.2.4.6 Data Switch partial PHY frame Count

When PMA\_state<7:6> = 01, then [Oct8<7:0>, Oct9<7:0>, Oct10<7:0>] contains the data switch partial PHY frame count (DataSwPFC24) sent LSB first. DataSwPFC24 indicates the partial PHY frame count when the transmitter switches from PAM2 to PAM3PAM4, which occurs at the start of an RS-FEC superframeblock. The last value of PFC24 prior to the transition is DataSwPFC24 - 1. DataSwPFC24 shall be set to an integer multiple of 1516. This value of DataSwPFC24 guarantees that the switch from PAM2 to PAM3-PAM4 occurs on a PHY frame boundary.

#### 97149.4.2.4.7 Reserved Fields

When PMA\_state<7:6> is greater than 01, then [Oct8<1:0>, Oct9<1:0>, Oct10<7:0>] contains a reserved field. All InfoField fields denoted Reserved are reserved for future use.

#### 97149.4.2.4.8 CRC16

CRC16 (2 octets) shall implement the CRC16 polynomial (x+1)(x15+x+1) of the previous 7 octets, Oct4<7:0>, Oct5<7:0>, Oct6<7:0>, Oct6

## 97149.4.2.4.9 PMA MDIO function mapping

The MDIO capability described in Clause 45 defines several variables that provide control and status information for and about the PMA. Mapping of MDIO control variables to PMA control variables is shown in Table 97149–9. Mapping of MDIO status variables to PMA status variables is shown in Table 97149–10.

#### 97149.4.2.4.10 Start-up sequence

The start-up sequence shall comply with the state diagram description given in Figure 97–26149-16. If the Auto-Negotiation function is not implemented, or mr\_autoneg\_en = false, PMA\_CONFIG is predetermined to be MASTER or SLAVE via management control during initialization or via default hardware setup.

The Auto-Negotiation function is optional for 1000BASE T1 PHYs. If the Auto-Negotiation function is used, during the Auto-Negotiation process PHY Control is in the DISABLE\_TRANSMITTER state and the transmitter is disabled. If the Auto-Negotiation function is not used, during the PHY Link Synchronization stage the PHY Control remains in the DISABLE\_TRANSMITTER state and the Link Synchronization function (see 97149, 4.2.6) is the data source for the PMA Transmit function.

When the Auto-Negotiation asserts link\_control = ENABLE, or PHY Link Synchronization process asserts sync\_link\_control = ENABLE, PHY Control enters the INIT\_MAXWAIT\_TIMER state. Upon entering the INIT\_MAXWAIT\_TIMER state, the maxwait\_timer is started. PHY Control then transitions to the SILENT state where the minwait\_timer is started and the PHY transmits zeros (tx\_mode = SEND\_Z).

In MASTER mode PHY Control transitions to the TRAINING state once the minwait\_timer expires.

Upon entering the TRAINING state, the minwait\_timer is started and the PHY Control asserts tx\_mode = SEND\_T sending PAM2 together with InfoFields. The PHY Control also sets PMA\_state = 00 and sends the PHY capability bits, the user configurable register bits, and the Seed value used by the local device for the data mode scrambler initialization, see <u>97149</u>.4.2.4.5.

The optional EEE capability shall be enabled only if both PHYs set the capability bit EEEen = 1. The optional 1000BASE-T1 OAM capability shall be enabled only if both PHYs set the capability bit OAMen = 1.

#### Formatted: Keep with next

InterleaveDpeth indicates the requested data mode interleaving depth. The value Oct10<2:1> = 00 shall indicate interleaving depth L=1, or no interleaving. The values Oct10<2:1> = 01, 10, and 11 shall indicate interleaving depth of 2, 4, and 8, respectively. The PHY transmitter shall be able to support the requested interleaving depth as indicated by the link partner.

<u>PrecodeSel indicates the requested data mode precoder. The value Oct10<4:3> = 00 shall indicate precoder bypass, or no precoder. The values</u> <u>Oct10<4:3> = 01, 10, and 11 shall indicate precoder choice of 1-D, 1+D, and  $1+D^2$ , respectively, as indicated in 149.3.2.2.20. The PHY transmitter</u> shall be able to support the selected precoder as indicated by the link partner.

Initially the MASTER is not ready for the SLAVE to respond and sets en\_slave\_tx = 0, which is communicated to the link partner via the InfoField. After the MASTER has sufficiently converged the necessary circuitry, the MASTER shall set en\_slave\_tx = 1 to allow the SLAVE to transition to TRAINING.

In SLAVE mode PHY Control transitions to the TRAINING state only after the SLAVE PHY acquires timing, converges its equalizers, acquires its descrambler state and sets loc\_SNR\_margin = OK. The SLAVE shall align its transmit <u>81B-65B-</u>RS <u>FEC super</u> frame to within +0/–1 partial PHY frames of the MASTER as seen at the SLAVE MDI. The SLAVE InfoField partial PHY frame Count shall match the MASTER InfoField partial PHY frame Count for the aligned frame.

Upon entering TRAINING state the SLAVE initially sets timing\_lock\_OK = 0 until it has acquired timing lock at which point the SLAVE sets timing\_lock\_OK = 1.

After the PHY completes successful training and establishes proper receiver operations, PCS Transmit conveys this information to the link partner via transmission of the parameter InfoField value loc\_rcvr\_status. The link partner's value for loc\_rcvr\_status is stored in the local device parameter rem\_rcvr\_status. Upon expiration of the minwait\_timer and when the condition loc\_rcvr\_status = OK and rem\_rcvr\_status = OK is satisfied, PHY control transitions to the COUNTDOWN state.

Upon entering the COUNTDOWN state, PHY Control sets PMA\_state = 01 and DataSwPFC24 to the value of the partial PHY frame count when the transmitter switches from PAM2 to PAM3PAM4.

Upon reaching DataSwPFC24 partial PHY frame count PHY Control transitions to the <u>SEND\_IDLE1PCS\_TEST1</u> state and forces transmission into the <u>idle\_PCS\_Test</u> mode by asserting tx\_mode = <u>SEND\_ISEND\_N</u>.

Once the link partner has transitioned from PAM2 to PAM3PAM4, PHY Control transitions to the SEND\_IDLE2\_PCS\_TEST2 state and starts the minwait\_timer.

Upon expiration of the minwait\_timer and when the condition loc\_phy\_ready = OK and rem\_phy\_ready = OK is satisfied, PHY control transitions to the SEND\_DATA state.

Upon entering the SEND\_DATA state, PHY Control starts the minwait\_timer and enables frame transmission to the link partner by asserting tx\_mode = SEND\_N.

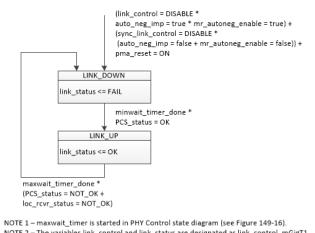

The operation of the maxwait\_timer requires that the PHY complete the start-up sequence from state INIT\_MAXWAIT\_TIMER to SEND\_DATA in the PHY Control state diagram state diagram (Figure 97–26149-16) in less than 97.5 ms to avoid link\_status being changed to FAIL by the Link Monitor state diagram (Figure 97–27149-17).

[NOTE: Need to redefine "rem\_countdown\_done" to be based on implicit counter values, instead of checking last InfoField.]

[NOTE: Need to define "PCS\_status" based on Clause 55.]

NOTE 1 – maxwait\_timer is started in PHY Control state diagram (see Figure 149-16). NOTE 2 – The variables link\_control and link\_status are designated as link\_control\_mGigT1 and link\_status\_mGigT1, respectively, by the Auto-Negotiation Arbitration state diagram (Figure 98-7) if the optional Auto-Negotiation function is implemented.

Figure 149-17 - Link Monitor state diagram

Figure 149-nn6 – Alignment of PAM2 Training PHY frame and data mode RS-FEC superframe

### Formatted: Keep with next