# Multi-Gig PHY Training and FEC Interleaving Depth

Sujan Pandey NXP Semiconductors

November 13, 2018

### **Motivation**

- Task force adopted use of interleaver to handle with variable length burst error due to transient pulse (ISO 7637-3)

- Move to adopt the interleaver as depicted on slide #9 of "tu\_3ch\_01a\_0918.pdf" as the baseline.

- Currently several proposals are on the table in terms of choosing interleaving depth for each PHY

- Mike Tu (<u>tu\_3ch\_04\_1018.pdf</u>)

- William Lo (<u>Lo\_3ch\_04\_1018.pdf</u>)

- Choosing interleaving depth impacts training frame format for all PHYs

## Interleaving Depth (L) Under Consideration

- Mike Tu (tu\_3ch\_04\_1018.pdf) suggests that TX of all PHYs

(2.5G/5G/10GBASE-T1) should support interleaving depth = 1, 2, 4, or 8

- William Lo (Lo\_3ch\_04\_1018.pdf) suggests two options

- 120ns of burst error protection

- 10G → [4, 8]

- 5G  $\rightarrow$  [2, 4]

- $2.5G \rightarrow [1, 2]$

- 60ns of burst error protection

- 10G → 4

- $5G \rightarrow 2$

- 2.5G → 1

- Choosing L for PAM2 training frame format for all PHYs?

- Mike Tu (tu\_3ch\_04\_1018.pdf) suggests to use training frame with L = 8

- This is bit over-kill for low speed PHY, which does not need burst error protection of 480ns!

# Interleaving Depth and Training Frame for all PHYs

- All PHY start with default Interleaving depth (L) = 1 without interleaving

- PAM2 Training frame format (N=360, K=326, m = 10) with L = 1

- 1800 PAM2 symbols

- Use 10 partial frame (PF)

- Each PF consists of 180 symbols same as 1000BASE-T1

- First bit of each partial frame is inverted same as 1000BASE-T1

- infoField is XOR'ed at the start of the 10<sup>th</sup> partial frame

- Actual L needed for data mode is exchanged through infoField during training

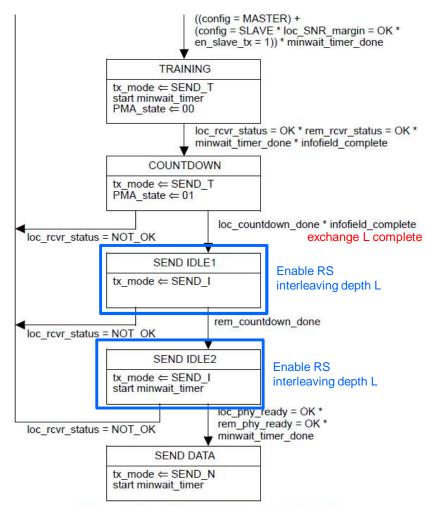

- Minor change to 1000BASE-T1 state diagram

Figure 97-26—PHY Control state diagram

## **Interleaving Depth**

- There are mixed opinions on choosing 60ns or 120ns of burst error protection for 10GBASE-T1?

- Start-up

- Default L=1 for all PHYs

- Choose <=60ns as "must"</li>

- safe guard burst error protection

- Trade-off between latency and power

- Choose 120ns as "optional" for unknowns

- SEND IDLE1, SEND IDLE2, and Data Mode

|      | Must      | Optional |

|------|-----------|----------|

| 2.5G | [1]       | [2]      |

| 5G   | [1, 2]    | [4]      |

| 10G  | [1, 2, 4] | [8]      |

#### Conclusions

- All PHYs should have one single interleaving depth for training frame and that should not add additional burden to lower speed PHYs

- Later the interleaving depth can be adjusted based on exchanged infoField

- Choosing default interleaving depth L = 1 for all PHYs for simplicity for PHY training frame format

- Interleaving for Data mode

- Choose bare minimum interleaving depths (L) to safe guard burst error protection up to 60ns as must

- Choose other interleaving levels for some specific use cases to address

120ns burst error protection as an optional

SECURE CONNECTIONS FOR A SMARTER WORLD