## Limiting Factors on Signal-to-Noise Ratio

#### Hossein Sedarat

December 2020

#### Overview

• A strawman proposal for insertion loss is derived from 802.3ch limit through frequency-scaling (<u>zimmerman\_3cy\_01a\_1120</u>)

• 30 dB loss at Nyquist frequency (7 GHz)

- A baseline analysis in jonsson\_3cy\_01a\_12\_01\_20 indicates positive performance margin with this limit for insertion loss

- This presentation explores the SNR impact of a few limiting factors not considered in the baseline analysis

#### Outline

- Assumptions in the baseline analysis

- Transmit PSD and its impact on SNR

- PCB insertion loss

- Other contributors to signal loss

- FEC coding gain for Gaussian noise

- EMI considerations

- Other sources of implementation loss

### Assumption in Capacity Analysis

- The baseline analysis indicates roughly 2.5 dB of PHY operating margin with an insertion loss according to the strawman proposal

- Some of the assumptions in that analysis

- Flat transmit PSD

- No other source of signal loss besides the cable

- Generous allocation of FEC coding gain to Gaussian noise

- No allocated budget for EMI

- Limited allocation for implementation loss

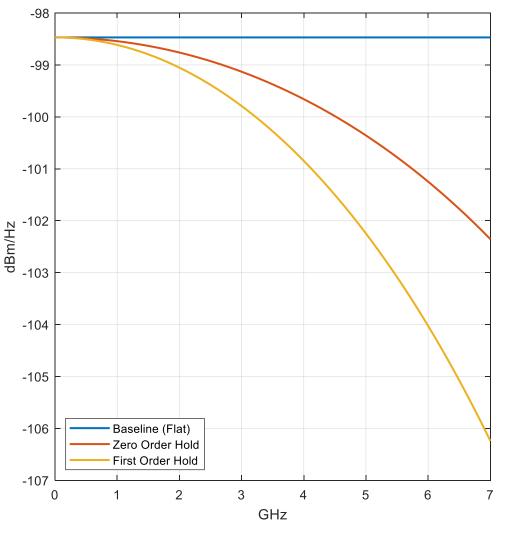

## Transmit PSD

- A flat transmit PSD is not realistic

- At the minimum, we should consider zero order hold

- Assuming the same peak voltage, zero order hold results in 4 dB loss at Nyquist

- A higher order hold, with higher loss, may be more desirable for emission considerations

- → SNR loss due to ZOH = 1.2 dB

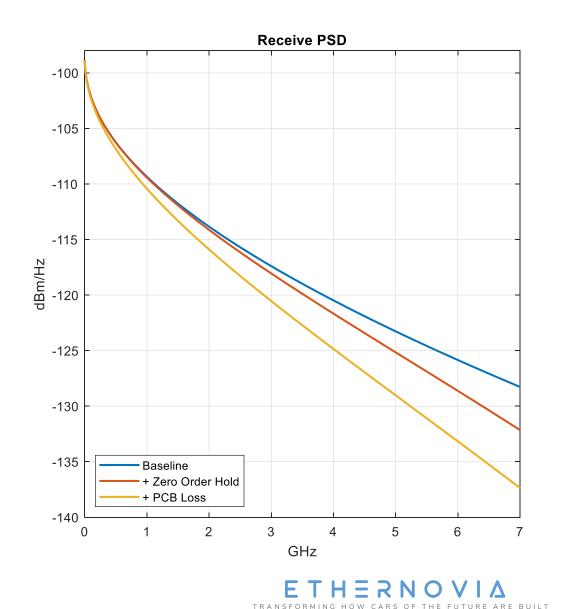

#### **PCB Insertion Loss**

- The baseline analysis assume no insertion loss for PCB

- Considering <u>kadry\_3cy\_02\_0820</u> with the suggested loss of more than 5 dB at Nyquist

- → Incremental SNR loss = 2.6 dB

### **Other Sources of Signal Loss**

- Partial list of additional sources of signal loss:

- Inline connectors

- Common-mode choke

- ESD protection

- PoDL and AC coupling

- The loss at Nyquist can easily grow to a few dBs at each end of the link

With an optimistic signal loss of only 1 dB at each end:

➔ Incremental SNR loss = 0.6 dB

### FEC and Impulse Noise

- FEC is the primary mechanism to protect against impulse noise

- Impulse noise is a burst of high-power disturbance

- The impulse burst may cover many words of an FEC frame (even with interleaving)

- Comparing to the frame size, the impulse burst covers 2.5 times more words than 802.3ch

- $\rightarrow$  Impulse noise is not uniformly spaced in time and it should not be treated as such in coding gain calculation

## FEC Coding Gain

- FEC error correction capability has to be partitioned between impulse noise and Gaussian noise

- Favoring Gaussian noise: consider uniform impulse rate resulting almost all of FEC coding gain (6 dB) allocated to Gaussian noise

- Favoring impulse noise: dedicate the entire FEC capability for impulse noise correction with no coding gain for Gaussian noise

- Fair partitioning: FEC should correct errors due to long burst of impulse noise and Gaussian noise simultaneously resulting in lower coding gain for Gaussian noise

With fair allocation:

→ Reduction in coding gain = 1.6 dB

#### **RF Noise Immunity**

- RF interference is an important noise source that has to be taken into account in overall noise budget

- A wider signaling bandwidth increases the susceptibility to RF noise

- Wider frequency range and exposure to RF sources

- Poor coupling/shielding attenuation of cable at high frequencies

- Worse mode-conversion and imbalance at higher frequencies

In order to tolerate 5 mv of EMI (<u>sedarat\_3cy\_01\_1120</u>):

#### → EMI margin allocation = 3.0 dB

#### Implementation Loss

- There are other sources of implementation loss besides AFE noise and partial echo cancellation

- Some of these sources are

- Finite resolution in digital signal processing

- Finite length of filters

- Additional equalization constraints due to challenges of very high sampling rate

- Sampling phase, PLL phase noise and clock jitter

While 3 dB allocation is very reasonable, consider a minimal value:

#### → Implementation loss = 1.0 dB

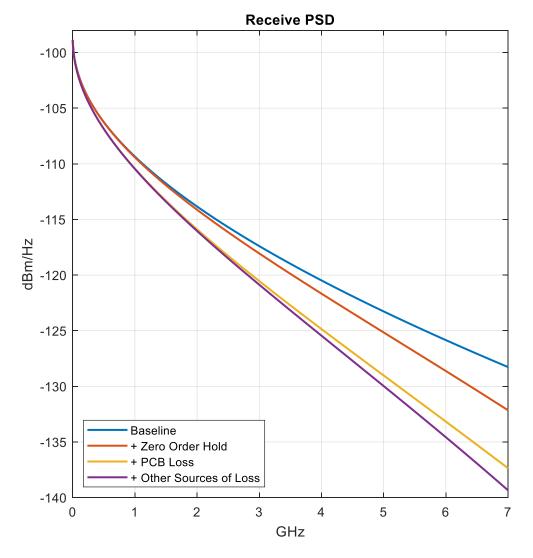

### Summary and Conclusion

- The strawman proposal for insertion loss shows 30 dB of loss at Nyquist

- A baseline analysis showed a positive operating margin for PHY with this limit

- Considering a few real limiting factors, the SNR margin is reduced by as much as 10 dB deep into negative values

➔ The strawman proposal for insertion loss is a very challenging limit line

|                         | SNR Margin<br>(dB) |

|-------------------------|--------------------|

| Baseline                | +2.5               |

| + Zero order hold       | -1.2               |

| + PCB loss              | -2.6               |

| + Other sources of loss | -0.6               |

| + FEC gain correction   | -1.6               |

| + EMI margin allocation | -3.0               |

| + Implementation loss   | -1.0               |

| Final SNR Margin        | -7.5               |

# ΤΗΔΝΚ ΥΟυ

ETHERNOVIA

hossein.sedarat@ethernovia.com