# Clause 104 Maintenance Requests #3

Karl Peterson

**Heath Stewart**

AHEAD OF WHAT'S POSSIBLE™

# Overview

| <b>Item</b>                               | Updated? |

|-------------------------------------------|----------|

| SCCP PSE/PD Watchdog Timer Overlap        | No       |

| SCCP C <sub>IN_CLASS</sub>                | Yes      |

| $\rightarrow$ SCCP $t_{REC}$              | Yes      |

| $\rightarrow$ SCCP $t_{RESET}$ Timing     | New      |

| $\rightarrow$ SCCP $t_{READSLOT}$ Timing  | Yes      |

| $\rightarrow$ SCCP $t_{WRITESLOT}$ Timing | Yes      |

| Reduce T <sub>F, min</sub>                | New      |

# PSE and PD SCCP Timers Overlap

► PSE Table 104-4

| Item | Parameter           | Symbol             | Unit | Min | Max         | Class             | Туре | Additional information |

|------|---------------------|--------------------|------|-----|-------------|-------------------|------|------------------------|

| 8    | Classification time | T <sub>Class</sub> | ms   |     | 366         | AllClasses 0 to 9 | All  | See 104.4.5            |

|      |                     |                    |      |     | <u>1300</u> | Classes 10 to 15  |      |                        |

PD Table 104-7

| 15 | SCCP watchdog timeout | T <sub>SCCP_watchd</sub> | ms | 150                        | 200                 | All <u>A.</u><br>B. C.<br>D | See 104.5.5 |

|----|-----------------------|--------------------------|----|----------------------------|---------------------|-----------------------------|-------------|

|    |                       |                          |    | <u>1000</u><br><u>1300</u> | <u>1300</u><br>2000 | <u>E</u>                    |             |

## **SCCP Watchdog Timer**

| 15 | SCCP watchdog timeout | T <sub>SCCP_watchd</sub> | ms | 150                        | 200                 | All <u>A.</u><br>B. C.<br>D | See 104.5.5 |

|----|-----------------------|--------------------------|----|----------------------------|---------------------|-----------------------------|-------------|

|    |                       |                          |    | <u>1000</u><br><u>1300</u> | <u>1300</u><br>2000 | <u>E</u>                    |             |

**Technical**, 802.3cg, Page 93, Table 104-7, Item 15

#### **Comment:**

The PSE and PD SCCP timers overlap. If all commands are executed at maximum timings the PD timeout can occur too aggressively.

#### **Suggested Remedy:**

Change SCCP, min:max for Class E from 1000ms:1300ms to 1300ms:2000ms.

Need to Address: Consensus

**Technical**, 802.3cg, Page 93, Table 104-7, Item 6b

Need to Address: Consensus

Solution Details: Consensus

#### Comment

- C<sub>IN CLASS</sub> is limited to ensure that excessive rise and fall times do not interfere with SCCP

- Other timing parameters are affected by C<sub>IN\_CLASS</sub>

- t<sub>R</sub> and t<sub>F</sub> were generous and can already accommodate C<sub>IN CLASS</sub> of up to 0.8uF

- C<sub>IN CLASS</sub>, max is 0.4uF for Type E

- This value is unnecessarily restrictive and potentially infeasible

- A reservoir cap is required to maintain PD operation during Reset commands

#### **Suggested Remedy**

Modify Table 104-7, Item 6b

| 6b | Input capacitance during DO_CLASSIFICATION state | C <sub>IN_Class</sub> | μF |   | 0.2        | All <u>A,</u> B, C, D | All classes Applies during tR and tF only. |

|----|--------------------------------------------------|-----------------------|----|---|------------|-----------------------|--------------------------------------------|

|    |                                                  |                       |    | = | 0.4<br>0.8 | <u>E</u>              |                                            |

# SCCP t<sub>REC</sub> Timing

| Parameter         | Min                        | Max  |

|-------------------|----------------------------|------|

| t <sub>REC</sub>  | <del>0.27</del> <u>0.5</u> | 0.33 |

| ŧ <sub>CHRG</sub> | 0.2                        |      |

| ¥ <sub>CHRG</sub> | 0.9×V <sub>PUPmin</sub>    |      |

- t<sub>REC</sub> should be treated like t<sub>CHRG</sub>

- t<sub>REC</sub> max timing is already constrained by t<sub>READ/WRITESLOT</sub>

- Real world slew rates between V<sub>TH</sub> and V<sub>PUP</sub>, rising, cannot be accommodated by existing timing relationships

- Propose: Only a min should be specified, increase min to track C<sub>IN CLASS</sub> change

- t<sub>CHRG</sub> introduces confusion without adding value

- t<sub>CHRG</sub> was intended to enable reservoir capacitor recharge but instead interferes by over-constraining charge

- Propose: Remove as redundant to t<sub>REC</sub>

Need to Address: Consensus

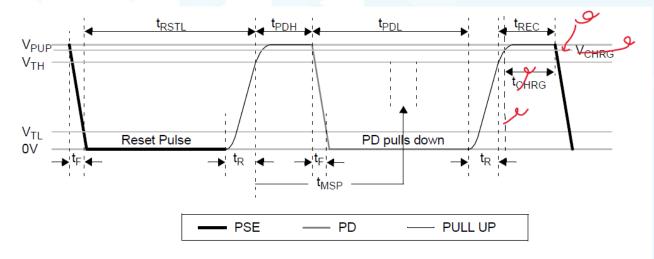

#### **SCCP Reset Command Timing**

| Parameter                  | Min                        | Max                       |

|----------------------------|----------------------------|---------------------------|

| t <sub>F</sub>             | 0.025                      | 0.25                      |

| t <sub>RSTL</sub>          | 8                          | 10.5                      |

| t <sub>PDH</sub>           | 0.7                        | 1.3                       |

| t <sub>MSP</sub>           | 1.8                        | <del>2.2</del> <u>2.4</u> |

| t <sub>PDL, E</sub>        | 2.8                        | 5.2                       |

| t <sub>PDL, E w/ CRM</sub> | 21                         | <del>31</del> <u>39</u>   |

| t <sub>R</sub>             | 0.025                      | 0.5                       |

| t <sub>REC</sub>           | <del>0.27</del> <u>0.5</u> | 0.33                      |

- C<sub>IN CLASS</sub> change lengthens real-world Reset component timings

- ► T<sub>PDL</sub> was by far the tightest PD timing accuracy requirement

- Make rationale and economically feasible by increasing to ~+/-20%

- Incorporate t<sub>RFC</sub> change as proposed previously

Propose: Changes as shown

Need to Address: Consensus

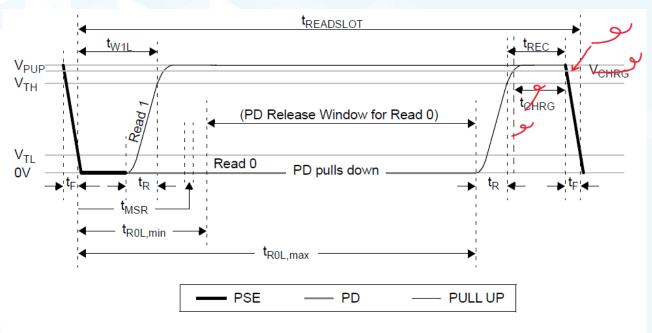

# SCCP t<sub>READSLOT</sub> Timing

| Parameter             | Min                        | Max                       |

|-----------------------|----------------------------|---------------------------|

| t <sub>F</sub>        | 0.025                      | 0.25                      |

| t <sub>MSR</sub>      | 0.9                        | <del>1.1</del> <u>1.3</u> |

| t <sub>ROL</sub>      | 1.75                       | 3.25                      |

| $t_R$                 | 0.025                      | 0.5                       |

| t <sub>REC</sub>      | <del>0.27</del> <u>0.5</u> | 0.33                      |

| t <sub>READSLOT</sub> |                            | 3.83 <u>5</u>             |

- Late changes to Read Slot component timing affected t<sub>READSLOT</sub> but were not accounted correctly

- Original t<sub>READSLOT,max</sub> did not correlate to sum of components

- Original calcs did not account for PSE and PD discrepancies for t<sub>R</sub> and t<sub>F</sub> in end-to-end systems

- Incorporate t<sub>REC</sub> change as proposed previously

Propose: Changes as shown

Need to Address: Consensus

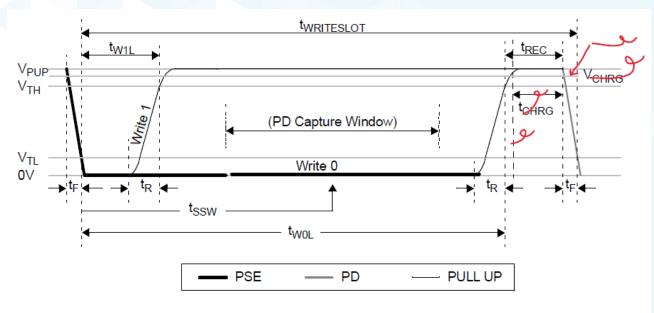

# SCCP twriteslot Timing

| Parameter              | Min                        | Max                         |

|------------------------|----------------------------|-----------------------------|

| t <sub>F</sub>         | 0.025                      | 0.25                        |

| t <sub>W1L</sub>       | 0.09                       | <del>0.61</del> <u>0.64</u> |

| t <sub>WOL</sub>       | 1.8                        | <del>2.2</del> <u>2.6</u>   |

| $t_R$                  | 0.025                      | 0.5                         |

| t <sub>REC</sub>       | <del>0.27</del> <u>0.5</u> | 0.33                        |

| t <sub>WRITESLOT</sub> |                            | <del>2.78</del> <u>3.85</u> |

- Original calcs did not account for PSE and PD discrepancies for t<sub>R</sub> and t<sub>F</sub> in end-to-end systems

- C<sub>IN CLASS</sub> change lengthens real-world Write Slot component timings

- Incorporate t<sub>REC</sub> change as proposed previously

- Propose: Changes as shown

Need to Address: Consensus

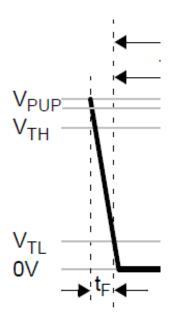

# SCCP t<sub>F</sub> Timing

| Parameter      | Min                       | Max  |

|----------------|---------------------------|------|

| t <sub>F</sub> | <del>0.025</del> <u>0</u> | 0.25 |

- t<sub>F,min</sub> is over-specified and serves as a design recommendation while serving no interoperability value

- Strong negative effect on economic feasibility

- Propose: Change as shown

Need to Address: Consensus

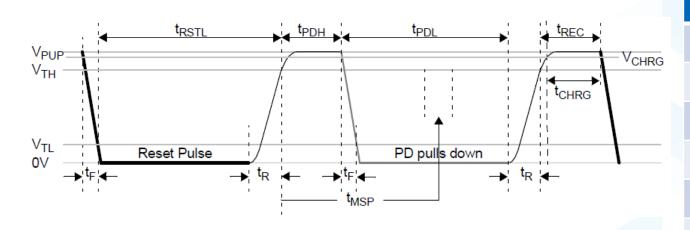

## Figure 104-10 Reset command

**Technical,** 802.3cg, Page 95, Figure 104-10

#### Comment

V\_CHRG and t\_CHRG requirements are limiting without bringing value to the standard.

#### **Suggested Remedy**

Modify Figure 104-10 as shown.

Remove V CHRG and associated voltage line.

Remove t\_CHRG arrow and text.

Remove timing reference dashed line at right end of t\_CHRG arrow.

Figure 104–10—Reset command timing diagram

Figure change based on proposed changes on slide 6

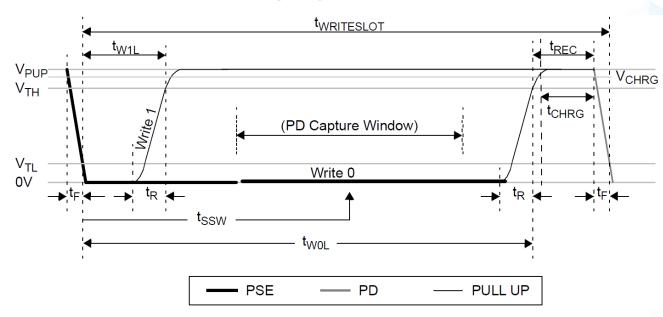

### Figure 104-11 Write 0/1 slot

Technical, 802.3cg, Page 96, Figure 104-11

#### Comment

V\_CHRG and t\_CHRG requirements are limiting without bringing value to the standard.

#### **Suggested Remedy**

Modify Figure 104-11 as shown.

Remove V CHRG and associated voltage line.

Remove t\_CHRG arrow and text.

Remove timing reference dashed line at right end of t\_CHRG arrow.

Figure 104–11—Write 0/1 slot timing diagram

Figure change based on proposed changes on slide 6

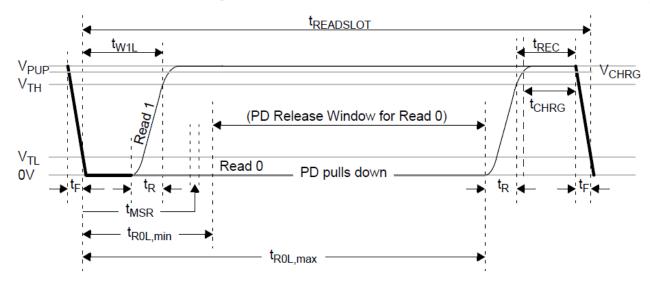

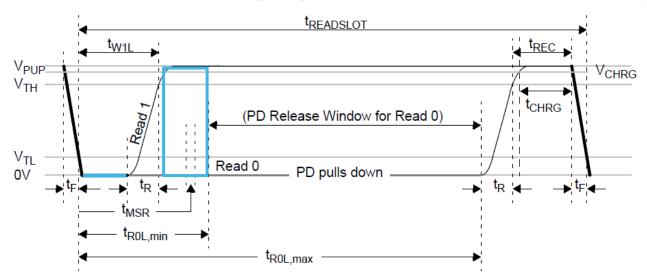

### Figure 104-12 Read 0/1 slot

**Technical,** 802.3cg, Page 96, Figure 104-12

#### Comment

V\_CHRG and t\_CHRG requirements are limiting without bringing value to the standard.

#### **Suggested Remedy**

Modify Figure 104-12 as shown.

Remove V CHRG and associated voltage line.

Remove t\_CHRG arrow and text.

Remove timing reference dashed line at right end of t\_CHRG arrow.

Figure 104–12—Read 0/1 slot timing diagram

Figure change based on proposed changes on slide 6

# Sample Changes

| Item       | Parameter        | Symbol                  | Unit | Min        | Max          | PSE/PD<br>Type              | Additional information |

|------------|------------------|-------------------------|------|------------|--------------|-----------------------------|------------------------|

| 6 <u>a</u> | Write Time Slot  | t <sub>WRITE</sub> SLOT | ms   | 2.7        | 3.3          | <u>A, B, C,</u><br><u>D</u> |                        |

|            |                  |                         |      | =          | 2.78<br>3.85 | <u>E</u>                    |                        |

| <u>6b</u>  | Read Time Slot   | <u>t</u> readslot       | ms   | 2.7        | 3.3          | <u>A, B, C,</u><br><u>D</u> |                        |

|            |                  |                         |      | =          | 3.83<br>5    | <u>E</u>                    |                        |

| 7          | Recovery Time    | t <sub>REC</sub>        | ms   | 0.27       | 0.33         | All A, B, C, D              |                        |

|            |                  |                         |      | <u>0.5</u> |              | <u>E</u>                    |                        |

| 8          | Write 0 Low Time | $t_{ m W0L}$            | ms   | 1.8        | 2.2          | All-<br>A, B, C,<br>D       |                        |

|            |                  |                         |      | 1.8        | <u>2.6</u>   | <u>E</u>                    |                        |

| 9          | Write 1 Low Time | t <sub>W1L</sub>        | ms   | 0.08       | 0.25         | <u>A, B, C,</u><br><u>D</u> |                        |

|            |                  |                         |      | 0.09       | 0.61<br>0.64 | E                           |                        |