## Requests for Adoption

IEEE 802.3dd – Power over Data Lines of Single Pair Ethernet (Maintenance #17) Task Force

George Zimmerman (Chair) – CME Consulting / ADI, APL Group, Cisco, CommScope, Marvell, SenTekSe

May 25, 2021

## V<sub>sig disable</sub> and V<sub>PUP</sub> Tracking Proposed Remedy

Table 104-5-Valid PD detection signature characteristics, measured at PD PI

| Parameter                    | Conditions                                            | Min  | Max  | Unit |

|------------------------------|-------------------------------------------------------|------|------|------|

| $V_{good}$                   | 7mA <i<sub>PD&lt;17mA, PD exiting RESET state</i<sub> | 4.05 | 4.55 | V    |

| I <sub>signature_limit</sub> | V <sub>pD</sub> <v<sub>sig_disable max</v<sub>        | _    | 24   | mA   |

| $V_{sig\_disable}$           | V <sub>PD</sub> rising                                | 4.6  | 5.75 | v    |

| V <sub>sig_enable</sub>      | V <sub>PD</sub> falling                               | 3.6  | 4.3  | v    |

| Item | Parameter                                 | Symbol           | Unit | Min           | Max | PSE/<br>PD<br>Type | Additional<br>information |

|------|-------------------------------------------|------------------|------|---------------|-----|--------------------|---------------------------|

| 1    | PSE Pull-up Voltage<br>(Classes 0 to 9)   | V <sub>PUP</sub> | V    | Vgood_PSE max | 5   | All                | See<br>Table 104–3        |

|      | PSE Pull-up Voltage<br>(Classes 10 to 15) |                  |      |               | 5.5 |                    |                           |

Table 104-8-SCCP electrical requirements

Technical, 802.3bu, Page 54, Table 104-5

### Comment

Transitions from DO\_CLASSIFICATION to MDI\_POWER1 pragmatically occur between  $V_{PUP,max}$  and  $V_{sig\_disable,max}$ . In 802.3bu, for Classes 0-9, this decision region spans 0.75V. In 802.3cg, for Classes 10-15,  $V_{PUP}$  changed to 5.5V, without a corresponding change to  $V_{sig\_disable}$ . The resulting decision region is reduced to 0.25V.

### Suggested Remedy

Modify 104-5 as follows, splitting  $V_{\text{sig\_disable}}$  into two rows Table 104-5—Valid PD detection signature characteristics, measured at PD PI

| Parameter                      | Conditions                                                                                                | Min  | Max  | Unit |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|

| $V_{good}$                     | 7mA <ipd<17ma, exiting="" pd="" reset="" state<="" td=""><td>4.05</td><td>4.55</td><td>v</td></ipd<17ma,> | 4.05 | 4.55 | v    |

| I <sub>signature_limit</sub>   | VpD <vsig_disable max<="" td=""><td>_</td><td>24</td><td>mA</td></vsig_disable>                           | _    | 24   | mA   |

| Vsig_disable, Classes 0 to 9   | V <sub>PD</sub> rising                                                                                    | 4.6  | 5.75 | v    |

| Vsig_disable, Classes 10 to 15 | V <sub>PD</sub> rising                                                                                    | 6.0  | 7.5  | V    |

| V <sub>sig_enable</sub>        | V <sub>PD</sub> falling                                                                                   | 3.6  | 4.3  | V    |

3 // 27 April 2021

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

## Cable Resistance Measurement and V<sub>Report PD</sub>

- For CRM, the PD reports its voltage to the PSE so the PSE can perform a ΔV/ΔI calculation. Accuracy is +/-20mV.

- The existing +/-20mV tolerance requirement does not allow power coupling network resistance to be, optionally, measured

- Removing the negative tolerance requirement allows greater design flexibility

- Regardless any measurement error is capped by R<sub>Cable</sub>, max and there is no risk to interoperability

$$R_{Cable} = \min(R_{Cable\ initial} \times K_{RMF}, R_{Loov(max)}) \Omega$$

(104-4b)

► Change +/- to +

Table 104-10—VOLT\_INFO register table

| Bit(s)  | Name                                               | Description                       | R/W |

|---------|----------------------------------------------------|-----------------------------------|-----|

| b[15:8] | Reserved                                           | Value always 0                    | RO  |

| Ъ[7:0]  | Voltage at<br>PD PI<br>during<br>Presence<br>Pulse | ±x 20 mV tolerance, 10 mV per LSB | RO  |

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

4 // 27 April 2021

<sup>&</sup>lt;sup>a</sup>RO = Read only

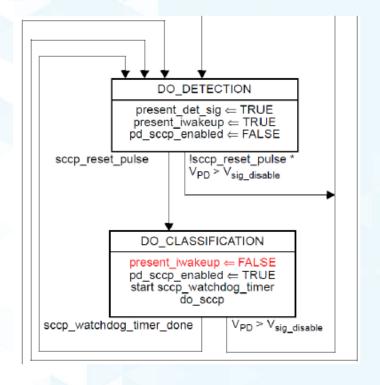

## DO\_CLASSIFICATION: present\_iwakeup

Technical, 802.3bu, Page 53, Figure 104-8

### Comment

The PD state machine, as written, requires present\_iwakeup to be TRUE in DO\_CLASSIFICATION based on an assignment derived from DO\_DETECTION. During classification the PD is engaged in SCCP signaling and cannot simultaneously present the iwakeup signature.

### Suggested Remedy

Modify Figure 104-8 as follows, specifically setting present\_iwakeup to FALSE in DO\_CLASSIFICATION.

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

5 // 27 April 2021

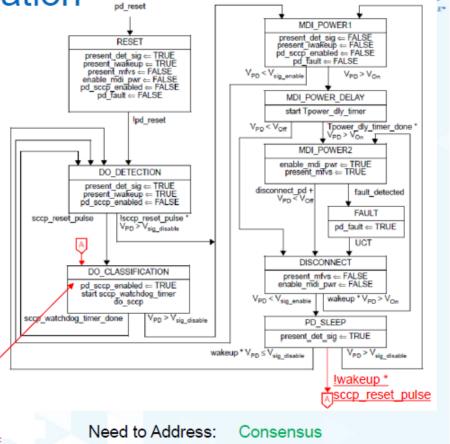

[04/27/21] Post-sleep Classification

Technical, 802.3bu, Page 53, Figure 104-8

#### Comment

The PD state machine, as written, does not allow a PD to respond to SCCP classification on PD\_SLEEP exit.

### Suggested Remedy

Change

wakeup

TRUE: the PD requires the full operating voltage at the PI.

FALSE: the PD is ready to go to sleep.

To

wakeup

An implementation specific variable enabling the PD to request wakeup.

TRUE: the PD requires the full operating voltage at the PI.

FALSE: the PD is ready to go to sleep or is not otherwise requesting full operating voltage.

4/27/21 proposed add: present\_iwakeup <= FALSE

Consensus

Consensus

Solution Form:

Solution Details:

ANALOG

## t<sub>PDL</sub> vs t<sub>PDLOW</sub>

Editorial, 802.3cg, Page 98

#### Comment

104.7 text and figures reference t<sub>PDL</sub> while Table 104-8 describes t<sub>PDLOW</sub>. Harmonize as t<sub>PDL</sub>, t<sub>PDLOW</sub> was a typo.

### Suggested Remedy

Modify Table 104-8, Row 15

|    | 1                           | 1                              | 1  |     |            |                             |                                                                  |

|----|-----------------------------|--------------------------------|----|-----|------------|-----------------------------|------------------------------------------------------------------|

| 15 | Presence-Detect<br>Low Time | <sup>†</sup> PDL <del>OW</del> | ms | 2.5 | 7.5        | <u>A, B, C,</u><br><u>D</u> |                                                                  |

|    |                             |                                |    | 2.8 | <u>5.2</u> | <u>E</u>                    |                                                                  |

|    |                             |                                |    | 21  | 31         | <u>E</u>                    | PDs that<br>support link<br>segment<br>resistance<br>measurement |

|    |                             |                                |    |     |            |                             |                                                                  |

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

### PD Backfeed

Technical, 802.3bu, Page 58

#### Comment

The existing 802.3bu requirement is only achievable for very low PD bulk cap implementations. New PHYs, e.g. T1L, require significant bulk capacitance. Propose to adopt approach taken in 802.3bt for backfeed requirement.

### Suggested Remedy

### Replace

#### 104.5.6.1 PD discharge

At a delay of T<sub>OFF</sub> max (see Table 104–4) after disconnection from the PSE, PD shall not source greater than 410 µJ out of its PI until V<sub>PD</sub> drops below V<sub>Sleep, RD</sub> max.

With the following new subclause (145.5.6.1):

### 104.5.6.1 Backfeed voltage PD discharge

When either there is no PSE or the PSE is not sourcing power, the PD backfeeds presents voltage back onto the (unpowered) pair. This can cause a current to flow out of the PD.

In order to constrain this current, the voltage across a  $5 \text{ k}\Omega$  resistor connected across the PD PI shall not exceed  $V_{PUP}$  as defined in Table 104–8, at a delay of  $T_{OFF}$  max (see Table 104–4) after the removal of PSE power from the PD PI.

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

## PD Current During Disconnect

ANALOG DEVICES

Need to Address: Consensus

Solution Form: Consensus

Solution Details: Consensus

Technical, 802.3bu, Page 56

#### Comment

Meeting the T<sub>OFF</sub> requirement when significant bulk capacitance is present requires the PD to pull down with a reasonable discharge current. The existing I<sub>Sleep PD</sub> requirement is at odds with the requirement to discharge the PD bulk cap within T<sub>OFF</sub>.

The PD is not presenting a valid detection signature in the DISCONNECT state and the PSE state diagram has a matching T<sub>OFF</sub> timer during the PSE's SETTLE\_SLEEP state.

Removing the PD I<sub>Sleep\_PD</sub> requirement in the DISCONNECT state allows the PD is discharge itself when disconnected from the PSE. This modification will not affect PSE/PD interoperability.

104.5.6.3 Input Current states:

During operation in the DISCONNECT and PD\_SLEEP states, the PD shall not draw current in excess of I<sub>Sleep\_PD</sub> as specified in Table 104–7.

### Suggested Remedy

Modify 145.5.6.3

During operation in the DISCONNECT and PD\_SLEEP states, the PD shall not draw current in excess of I<sub>Sleep\_PD</sub> as specified in Table 104–7.