Dear colleagues,

I missed the deadline to submit a comment against Draft 2.0, but this allows me to get your opinion on a specific aspect of the receiver input test procedure.

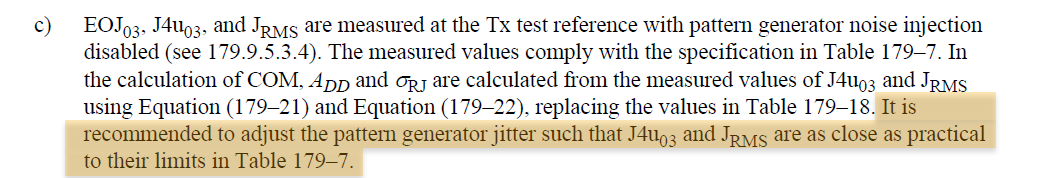

In several places—such as clause 179.9.5.3.3 (Test channel calibration, CR) and annexes 176C (C2C) and 176D (C2M)—there is a recommendation to adjust the pattern generator jitter to approach practical limits (23mUI Jrms, 120muI J4u03) before

injecting broadband noise. Please see the screenshot below for reference.

However, unlike the CK standard (see 120G.3.3.5.1 Host stressed input test setup), these clauses do not specify the jitter mix.

My concern is that this could lead to receivers being tested with overly simplistic jitter profiles—e.g., using only sinusoidal jitter (SJ)—which may not reflect realistic stress conditions. For example, it is possible to approach the 23

mUI Jrms target using only 50 mUI SJ.

Do you think we should clarify or tighten the guidance to ensure more representative jitter conditions?

Looking forward to your thoughts.

Best regards,

Hadrien

Best regards,

Dr. Hadrien Louchet,

Vertical Lead, Datacenter Networking

Keysight Technologies

Herrenberger Str. 130, D 71034 Boeblingen Germany

+49 7031 464 ext. 4089 T | +49 173 631 621 3 M |

email: hadrien.louchet@xxxxxxxxxxxx

Keysight Technologies Deutschland GmbH, Herrenberger Straße 130, 71034 Böblingen

Sitz der Gesellschaft: Böblingen – Amtsgericht Stuttgart HRB 747687, WEEE-Reg.-Nr. DE 26672786

Geschäftsführer: Dr. Joachim Peerlings (Vorsitzender), Thomas Götzl

To unsubscribe from the STDS-802-3-B400G-ELEC list, click the following link: https://listserv.ieee.org/cgi-bin/wa?SUBED1=STDS-802-3-B400G-ELEC&A=1