# Architecture considerations for 800GbE and 1.6TbE

Yuchun LU, Yan ZHUANG, Huawei Technologies

IEEE P802.3df Task Force

May 18 2022

### Observations of adopted physical layer objectives

| Ethernet | Signaling | Electrical                  |                                       |                               | Optical                      |                              |                              |                                                                  |                                              |                                              |

|----------|-----------|-----------------------------|---------------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Rate     | Rate      | AUI                         | Backplane                             | Copper<br>Cable               | MMF<br>50m                   | MMF<br>100m                  | SMF<br>500m                  | SMF<br>2km                                                       | SMF<br>10km                                  | SMF<br>40km                                  |

| 200Gbps  | 200Gbps   | Over 1 lane<br>200GAUI-1    | TBD *<br>200GBASE-KR1                 | Over 1 pair<br>200GBASE-CR1   |                              |                              | Over 1 pair<br>200GBASE-DR1  | Over 1 pair<br>200GBASE-FR1                                      |                                              |                                              |

| 400Gbps  | 100Gbps   |                             |                                       |                               |                              |                              |                              | Over 4 pairs<br>400GBASE-DR4-2                                   |                                              |                                              |

| 400Gbps  | 200Gbps   | Over 2 lanes<br>400GAUI-2   | TBD *<br>400GBASE-KR2                 | Over 2 pairs<br>400GBASE-CR2  |                              |                              | Over 2 pairs<br>400GBASE-DR2 |                                                                  |                                              |                                              |

|          | 100Gbps   | Over 8 lanes<br>800GAUI-8   | Over 8 lanes<br>800GBASE-KR8          | Over 8 pairs<br>800GBASE-CR8  | Over 8 pairs<br>800GBASE-VR8 | Over 8 pairs<br>800GBASE-SR8 | Over 8 pairs<br>800GBASE-DR8 | Over 8 pairs<br>800GBASE-DR8-2                                   |                                              |                                              |

| 800Gbps  | 200Gbps   | Over 4 lanes<br>800GAUI-4   | TBD *<br>Over 4 pairs<br>800GBASE-KR4 | Over 4 pairs<br>800GBASE-CR4  |                              |                              | Over 4 pairs<br>800GBASE-DR4 | Over 4 pairs<br>800GBASE-DR4-2<br>Over 4 lambdas<br>800GBASE-FR4 | TBD                                          |                                              |

|          | TBD       |                             |                                       |                               |                              |                              |                              |                                                                  | Over single<br>SMF in each<br>direction<br>? | Over single<br>SMF in each<br>direction<br>? |

|          | 100Gbps   | Over 16 lanes<br>1.6TAUI-16 |                                       |                               |                              |                              |                              |                                                                  |                                              |                                              |

| ?1.6Tbps | 200Gbps   | Over 8 lanes<br>1.6TAUI-8   |                                       | Over 8 pairs<br>1.6TGBASE-CR8 |                              |                              | Over 8 pairs<br>1.6TBASE-DR8 | Over 8 pairs<br>1.6TBASE-DR8-2                                   |                                              |                                              |

\* Should be adopted as long as the signaling & modulation & insertion loss objectives for CR/KR channels are determined.

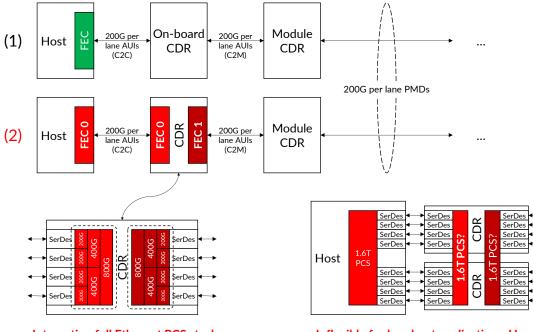

1. In mainstream applications, the number of AUI channels is the same as that of PMD channels.

2. Flexible breakout of the CDR is an essential requirement to support 1x, 2x, 4x and 8x 200Gbps Ethernet interfaces.

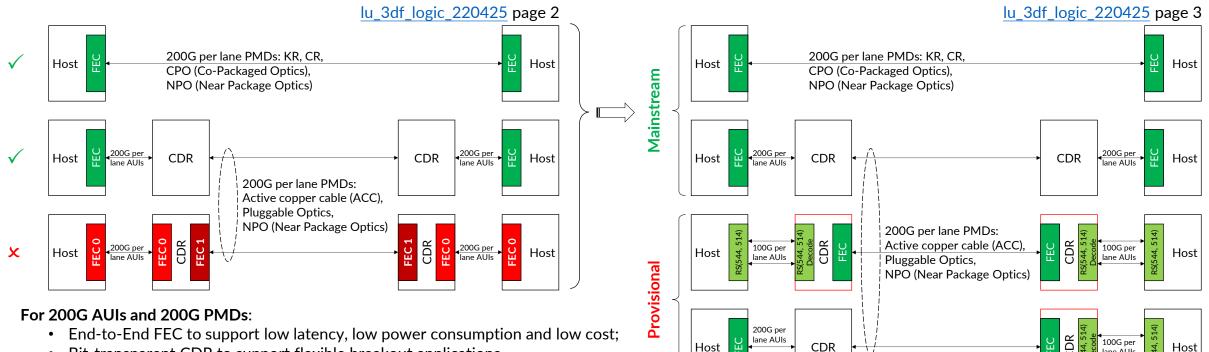

#### Start from 200G AUIs & PMDs and determine the optimization direction for the mainstream applications

• Bit-transparent CDR to support flexible breakout applications.

#### For 100G AUIs and 200G PMDs:

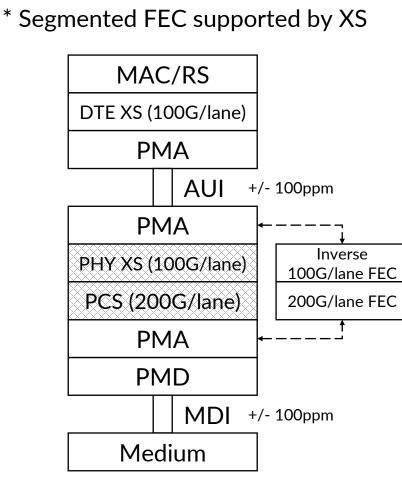

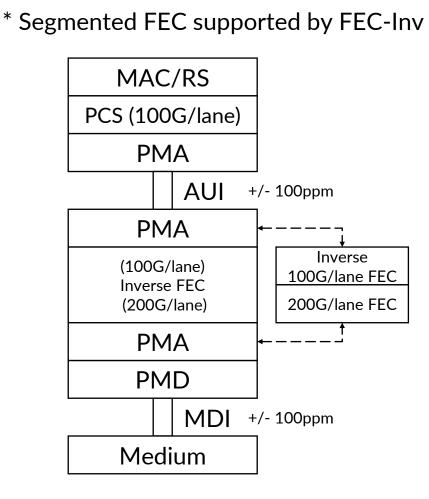

- Segmented FEC is natural, necessary and preferred.

- Use the same FEC for 200G AUIs and 200G PMDs.

- Use virtual lane aggregation to reduce the virtual lane number and the complexity.

- Use 1:1 PMA to avoid error spreading and guarantee the FEC performance.

- End-to-end FEC with interleaved RS(544, 514) needs a lot of evidence to show that:

- RS(544, 514) with bitmux PMA is sufficient for both 200G AUIs & PMDs.

- Channel quality and DSP performance are good enough for RS(544, 514).

- Error spreading of bitmux PMA does not hurt RS(544, 514) performance.

#### General design rules:

- 1. Remove unnecessary intermediate processing.

- 2. Simplify the CDR as much as possible and shift the necessary "complexity" to the host ASIC. (The Concatenated FEC does not simplify the CDR)

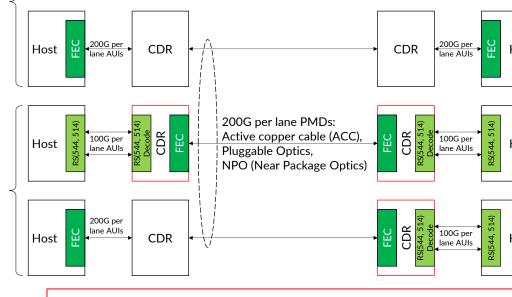

## FEC processing in CDR has small SNR improvement, the gain is negligible if PMD is dominant in performance

YUCHUN LU

## FEC processing in CDR is expensive and inflexible, it should be applied only when necessary (e.g. gearbox & new FEC)

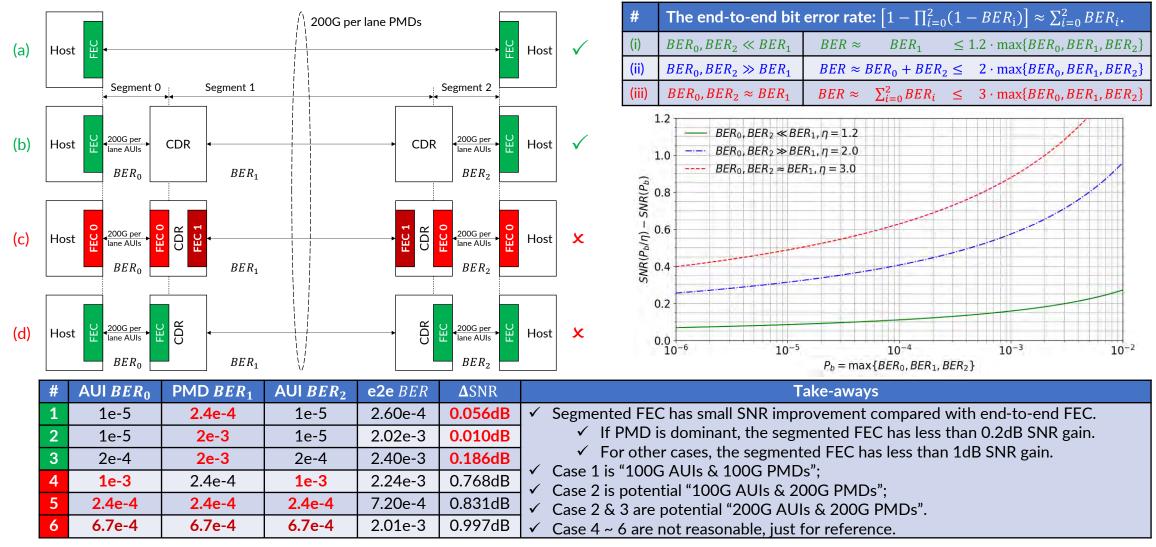

- FEC processing inside CDR means integration of two back-to-back full Ethernet PCS stacks inside the CDR.

- If the rates of the client side and the line side are different, one **extra PLL** per direction is required for new frequency point.

- Ethernet PCS/FEC crosses multiple physical lanes, FEC termination is difficult to support flexible CDR breakout.

#### FEC processing in CDR is expensive and inflexible, choose the FEC according to the worst AUI link segment

Integration full Ethernet PCS stack inside the CDR is too expensive.

Inflexible for breakout applications. How to achieve 1.6T PCS across two CDR chip?

| #                                                       | AUI-C2C BER | AUI-C2M BER | AUI E2E BER | <b>∆</b> SNR |  |  |

|---------------------------------------------------------|-------------|-------------|-------------|--------------|--|--|

| 1                                                       | 2e-4        | 1e-5        | 2.10e-4     | 0.033dB      |  |  |

| 2                                                       | 1e-3        | 2e-4        | 1.20e-3     | 0.163dB      |  |  |

| 3                                                       | 1e-4        | 1e-4        | 2.00e-4     | 0.445dB      |  |  |

| 4                                                       | 2e-4        | 2e-4        | 4.00e-4     | 0.493dB      |  |  |

| Case 1 is "100G AUIs"; Case 2 is potential "200G AUIs"; |             |             |             |              |  |  |

| Case 3 & 4 are not reasonable, just for reference.      |             |             |             |              |  |  |

- FEC termination in CDR has negligible SNR improvement, less than 0.2dB.

- FEC for termination for cascaded AUIs are too expensive and inflexible.

- Two back-to-back full Ethernet PCS stacks inside the on-board CDR are required.

- One extra PLL per direction is required to support new frequency point, if the rates of the client side and line side are different.

- Cannot support flexible CDR breakout.

| Design rules for on-board CDR (CDR for AUIs):           |

|---------------------------------------------------------|

| 1. Simplify the on-board CDR as much as possible and    |

| shift the necessary "complexity" to the host ASIC. Bit- |

| transparent CDR is always optimal.                      |

| 2. Choose the end-to-end FEC according to the worst     |

2. Choose the end-to-end FEC according to the worst segment of the AUI links, i.e. AUI-C2C.

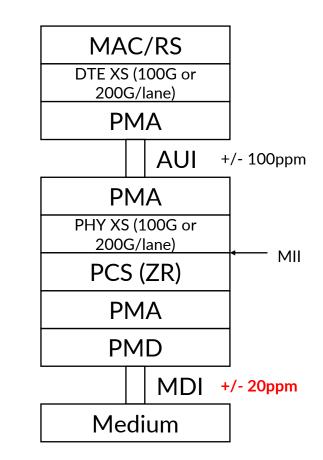

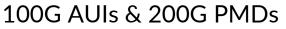

- 1. "Rate matching (supported by XS)" is mandatory for "ZR" applications due to the different requirement of clock drift in ppm.

- 2. It is not necessary to terminate the PCS, only the FEC needs to be terminated and new FEC is encoded/decoded.

- 3. Inverse RS-FEC Sublayer overview can be found in <u>nicholl\_3ck\_02\_0519</u>.

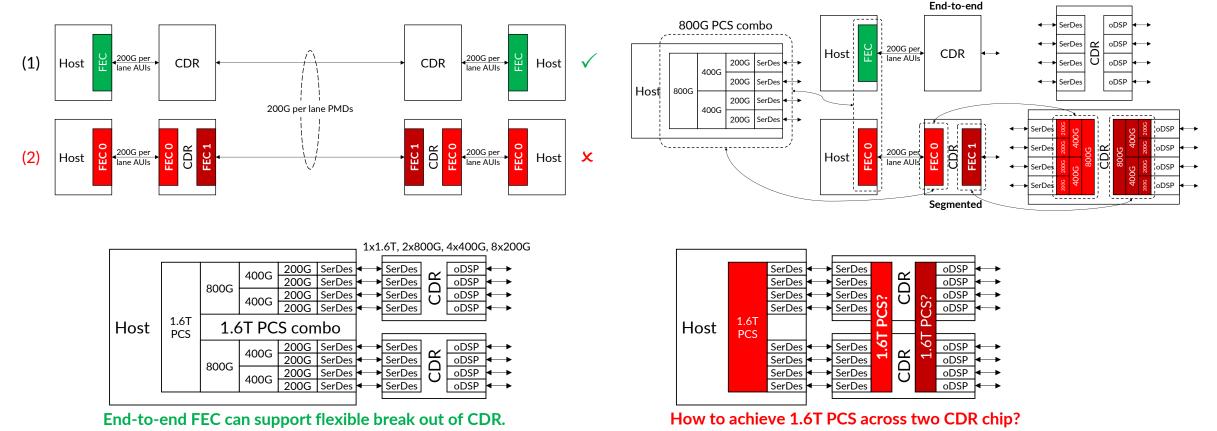

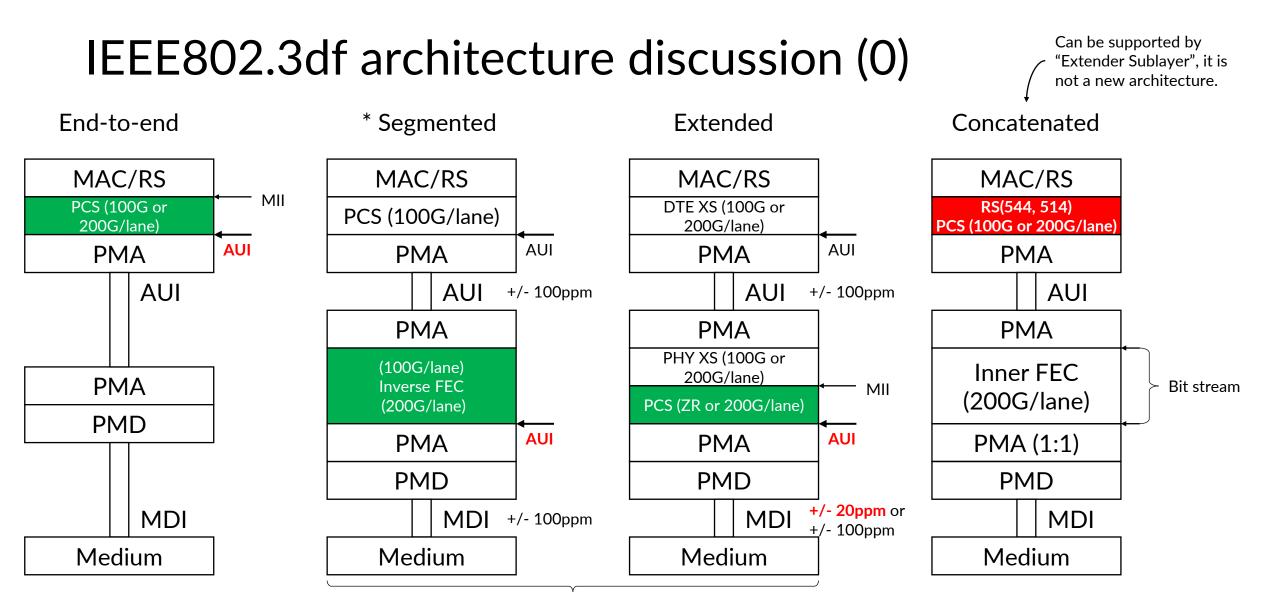

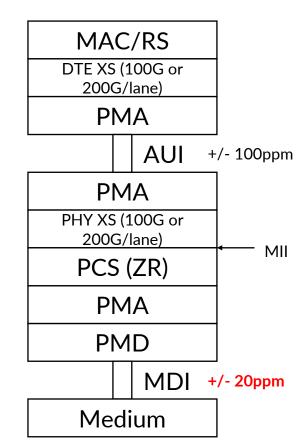

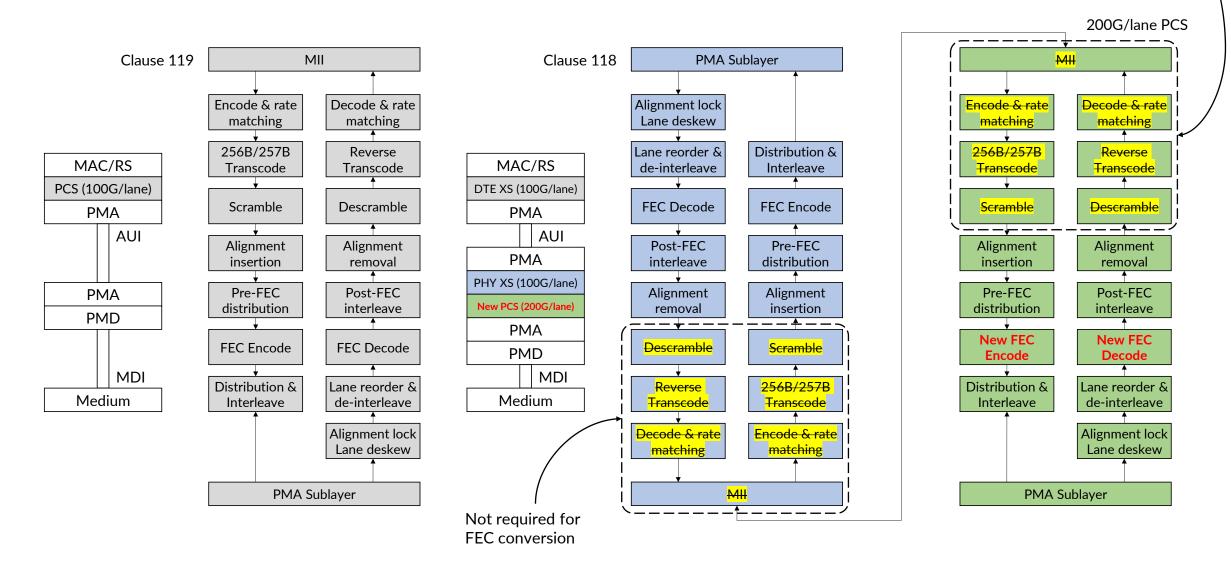

#### IEEE802.3df architecture discussion (1)

100G AUIs & 100G PMDs 200G AUIs & 200G PMDs 100G AUIs & 200G PMDs

100G/200G AUIs & ZR PMDs

2022/4/25

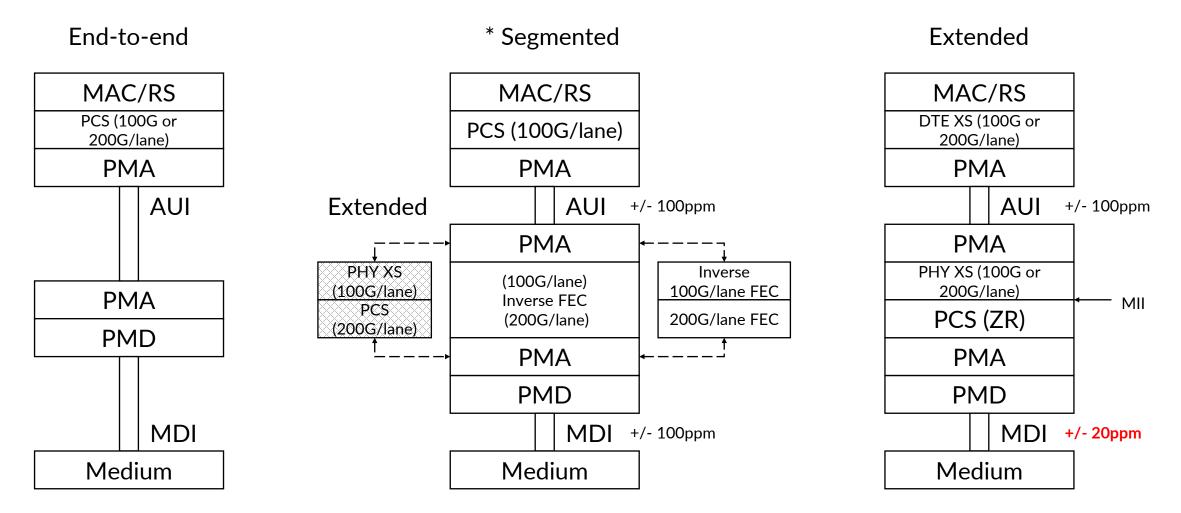

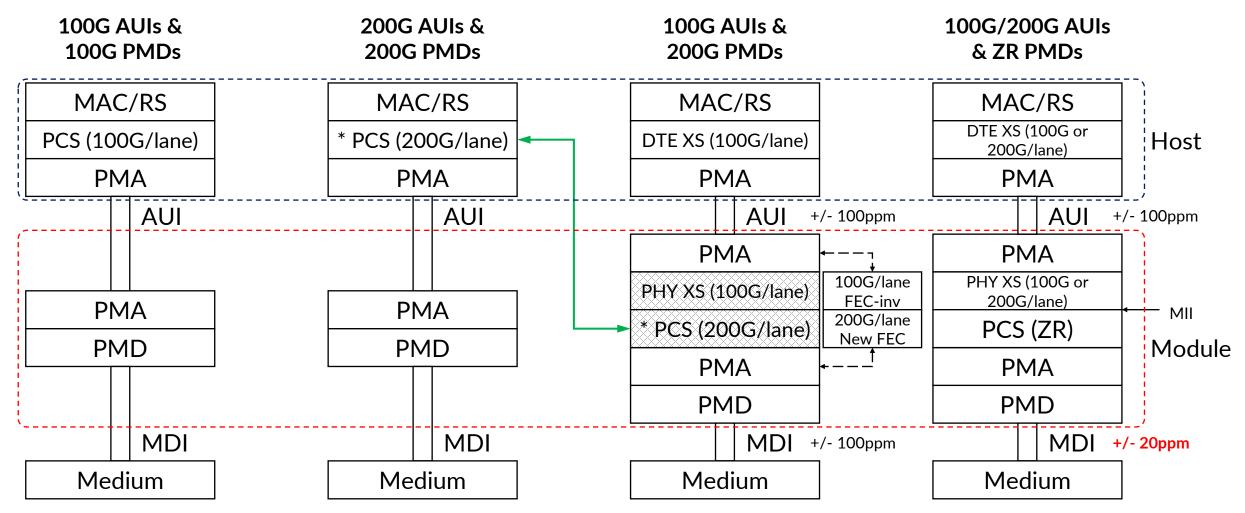

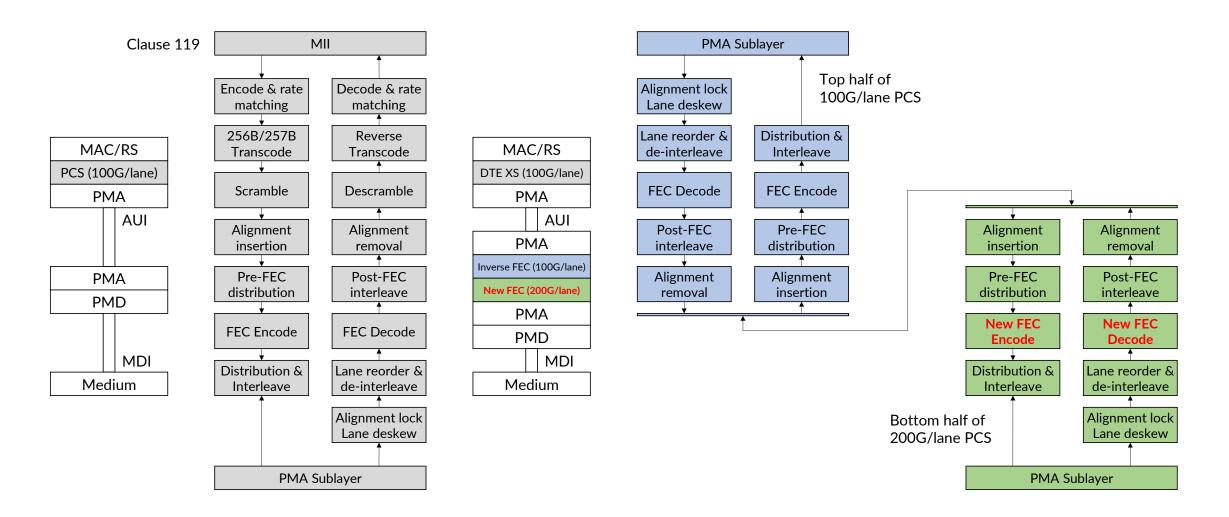

#### IEEE802.3df architecture discussion (2)

100G AUIs & 100G PMDs 200G AUIs & 200G PMDs

Extended

100G AUIs & 200G PMDs

100G/200G AUIs & ZR PMDs

2022/4/25

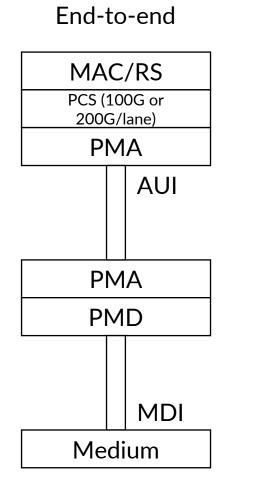

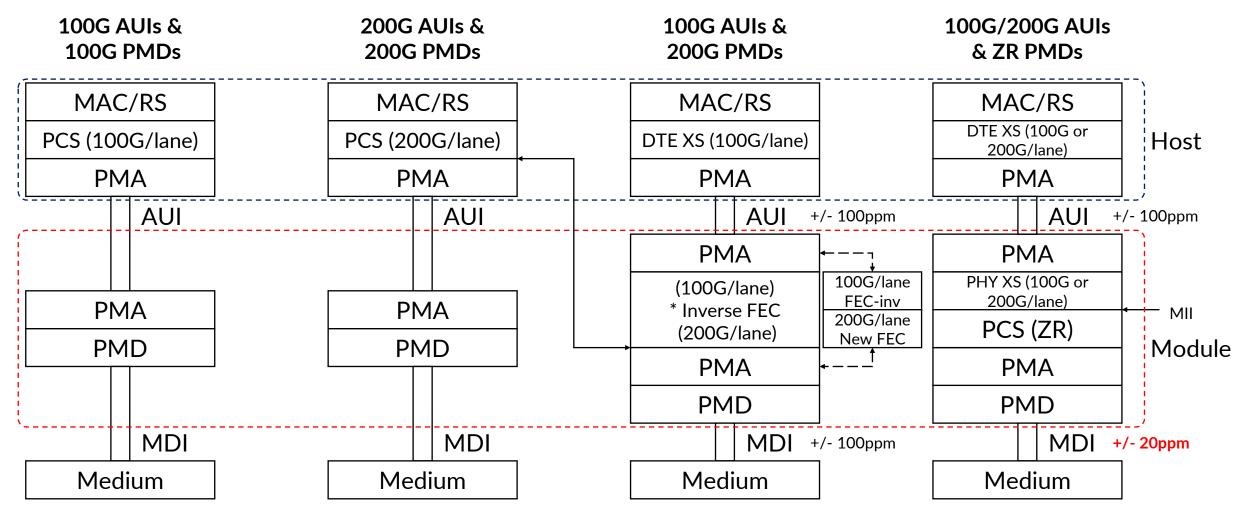

#### IEEE802.3df architecture discussion (3)

100G AUIs & 100G PMDs 200G AUIs & 200G PMDs

Extended

100G/200G AUIs & ZR PMDs

2022/4/25

### Proposed IEEE 802.3df architecture (0)

\* Pros: Only editorial benefit, i.e. re-use "200G/lane PCS" clause for PHY XS; Cons: Lack of technical insights and details.

### Proposed IEEE 802.3df architecture (1)

\* Pros: Intuitive, simple and clear; Cons: Define the inverse FEC sublayer (Editorial).

#### Extender Sublayer for the "new FEC"

Not required for FEC conversion

#### Inverse FEC Sublayer for the "new FEC"

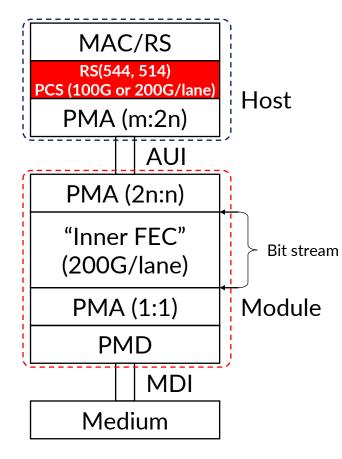

### Questions for Concatenated FEC architecture

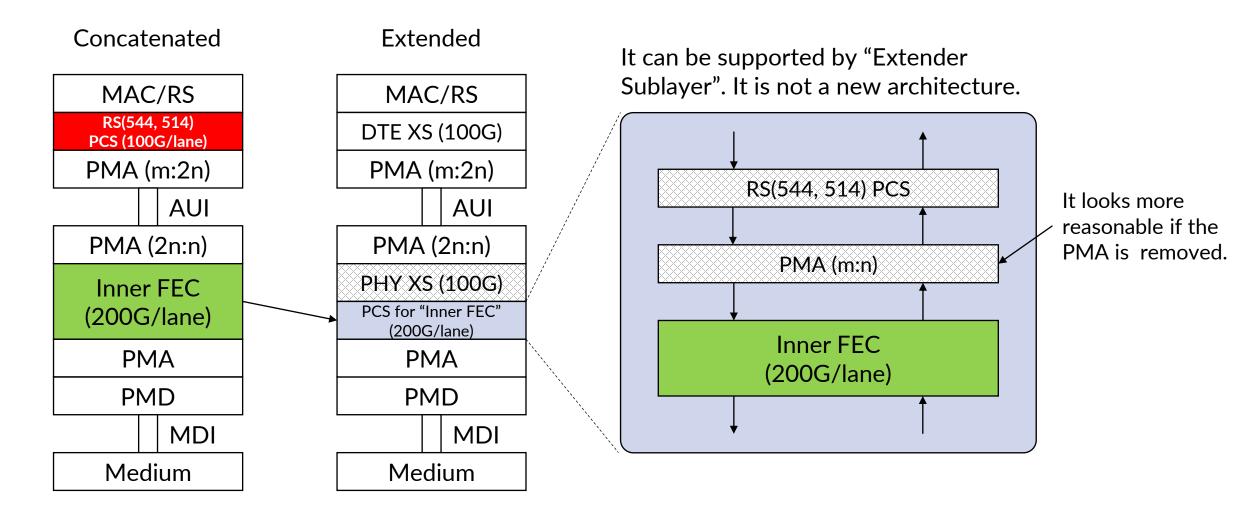

#### Concatenated

- It can be supported by "Extender Sublayer", It is not a new architecture.

- What is the detailed functionality of "Inner FEC" sublayer?

- On the transmitter side, take the PMA bit stream per-lane and slice into data blocks of "inner FEC" payload size, and encoded as inner FEC code word. The "inner FEC" is per-PMD lane based.

- On the receiver side, take the per-PMD lane based inner FEC stream, decode the inner FEC code, strip the inner FEC parity and recover the "bit-muxed" PMA bit stream lanes.

- Does it require RS(544, 514) FEC to cover all the 200G AUIs?

- RS(544, 514) need to cover the 200G AUIs and PMDs end-to-end for 200G/lane native applications.

- What would be the instantiation on host PCS of this architecture?

- Soft-decision FEC cannot be implemented in the host ASIC.

- How to address the performance concern?

- The **net coding gain improvement is negligible or even negative** compared RS(544, 514) under burst channels (<u>lu 3df\_logic\_220425</u>, page 9).

- Soft-decision FEC is not compatible with DFE & MLSE, it is probably the worst in performance (<u>lu\_3df\_01b\_220215</u>, page 6~8).

- How to address the reliability concern (MTTFPA issue)?

- The inner FEC decoding failure generates **burst errors** (<u>lu 3df logic 220425</u>, page 12). The parity bits of "inner FEC" are wasted, the error detection capability is not improved. **Random error model for MTTFPA calculation is not available** and it is over optimistic, a new model account for burst errors is required.

- Reliable inner FEC frame alignment with "2e-3" channels, without the alignment markers is challenging? The "bit-muxed" PMA streams do not have alignment markers.

- How to address the CDR complexity concern over the bit-transparent CDR scheme?

- The rates of client side and line side are different, **it is overwhelmed to introduce one extra PLL per direction** to support new frequency point. It is far more complicated than the bit-transparent CDR.

## Concatenated FEC can be supported by "Extender Sublayer", it is not a new architecture

### Summary

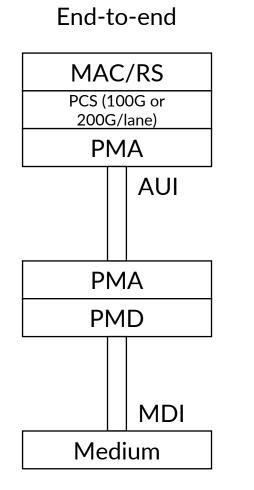

- End-to-end FEC architecture is optimal for 200G AUIs & 200G PMDs and cascaded multiple AUIs.

- FEC processing inside CDR means integration of two back-to-back full Ethernet PCS stacks inside the CDR. The rate difference between the client side and line side requires extra PLLs.

- Ethernet PCS/FEC crosses multiple physical lanes. Only bit-transparent CDR can support low cost flexible breakout.

- Choose the end-to-end FEC according to the worst segment of the AUI and PMD links.

- Segmented FEC architecture is optimal for 100G AUIs & 200G PMDs.

- Can be supported by "Extended Sublayer" or "Inverse FEC Sublayer".

- "Extended Sublayer" is flexible, has editorial benefit, but lack of technical insights and details.

- "Inverse FEC Sublayer" is intuitive, simple and clear.

- Extended Sublayer is essential for 100G/200G AUIs & ZR PMDs, due to the different clock drift of AUIs (+/-100ppm) and ZR PMDs (+/- 20ppm). It is different from the "Inverse FEC Sublayer" idea.

- A lot of investigations and clarifications are required for "Concatenated FEC".

#### Recommendation

- Adopt "End-to-end FEC" as a baseline architecture (support bit-transparent CDR and flexible CDR breakout) for the mainstream applications, i.e. "100G AUIs & 100G PMDs" and "200G AUIs & 200G PMDs" to achieve low cost, low power consumption, low latency and flexibility (CDR breakout).

- Adopt the "Segmented FEC/Extended Sublayer" as baseline architecture for the provisional applications, i.e. "100G AUIs & 200G PMDs". Adopt Extended Sublayer for ZR applications to compensate the clock drift difference between AUIs (+/-100ppm) and ZR PMDs (+/- 20ppm).

- Support multiple FEC code schemes, e.g. RS(N, K), ZR FEC, etc.

- The concatenated FEC can be supported by the "Segmented/Extended" architecture.

# Q&A