# 802.3df D1.1 Comment Resolution

P802.3df editorial team

### Introduction

• This slide package is put together by the 802.3df editorial team to provide background and detailed resolutions to aid in comment resolution.

# Clause 167

### Fiber optics cabling Comments 13, 14, 116 (part 1)

- Three comments were received highlighting issues with the clause 167 "Characteristics of the fiber optic cabling and MDI" PICS table

- Comments 13, 14, and 116

| CI 167                                                                              | SC                                                        | 167.11.4.6                                                                                            | ß                                                                      | P158                                        |                       | L 31      |          | # 13 |          |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------|-----------------------|-----------|----------|------|----------|

| Ran, Adee                                                                           |                                                           |                                                                                                       |                                                                        | Cisco                                       |                       |           |          | -    |          |

| Comment                                                                             | Туре                                                      | т                                                                                                     | Commen                                                                 | t Status X                                  |                       |           |          |      |          |

|                                                                                     | led fib                                                   |                                                                                                       | 5 through 0<br>. However,                                              |                                             |                       |           |          |      |          |

| The va                                                                              | lue/co                                                    | mment nee                                                                                             | ds to be dif                                                           | ferent for a                                | angled and            | flat.     |          |      |          |

| Suggested                                                                           | Reme                                                      | dy                                                                                                    |                                                                        |                                             |                       |           |          |      |          |

| Add or                                                                              | chang                                                     | e PICS iter                                                                                           | ms for 167.                                                            | 10.3.4 as a                                 | ppropriate            | э.        |          |      |          |

| Proposed I                                                                          | Deene                                                     |                                                                                                       | Deenenee                                                               | Status O                                    |                       |           |          |      |          |

| Floposeu                                                                            | Respon                                                    | nse                                                                                                   | Response                                                               |                                             |                       |           |          |      |          |

| Floposed                                                                            | Respo                                                     | nse                                                                                                   | Response                                                               | otatus U                                    |                       |           |          |      |          |

|                                                                                     |                                                           |                                                                                                       |                                                                        |                                             |                       | 1 37      |          | # 14 |          |

| CI 167                                                                              | SC                                                        | nse<br>167.11.4.6                                                                                     |                                                                        | P158                                        |                       | L 37      |          | # 14 |          |

| Cl 167<br>Ran, Adee                                                                 | SC                                                        | 167.11.4.6                                                                                            |                                                                        | P158<br>Cisco                               |                       | L 37      |          | # 14 |          |

| Cl 167<br>Ran, Adee<br>Comment                                                      | SC<br>Type                                                | 167.11.4.6<br>T                                                                                       | Commen                                                                 | P158<br>Cisco<br>t Status X                 |                       |           |          |      |          |

| Cl 167<br>Ran, Adee<br>Comment<br>The va                                            | SC<br>Type<br>ilue/co                                     | 167.11.4.6<br>T<br>mment for 0                                                                        |                                                                        | P158<br>Cisco<br>t Status X<br>des "or per  |                       |           | design   |      | CIS 18 A |

| C/ 167<br>Ran, Adee<br>Comment<br>The va<br>1-0 or                                  | SC<br>Type<br>Ilue/co<br>FOCIS                            | <b>167.11.4.6</b><br>T<br>mment for (<br>3 18 R-1x16                                                  | Commen<br>OC18 inclue                                                  | P 158<br>Cisco<br>t Status X<br>des "or per | ANSI/TIA              | -604-18-A | design   |      | CIS 18 A |

| Cl 167<br>Ran, Adee<br>Comment<br>The va<br>1-0 or<br>These                         | SC<br>Type<br>ilue/co<br>FOCIS<br>do not                  | <b>167.11.4.6</b><br><b>T</b><br>mment for (<br>3 18 R-1x16<br>t appear in (                          | Commen<br>OC18 inclue<br>-1-0-1-2-0"                                   | P 158<br>Cisco<br>t Status X<br>des "or per | ANSI/TIA              | -604-18-A | . design |      | CIS 18 A |

| Cl 167<br>Ran, Adee<br>Comment<br>The va<br>1-0 or<br>These<br>Also in              | SC<br>Type<br>ilue/co<br>FOCIS<br>do not                  | <b>167.11.4.6</b><br><b>T</b><br>mment for (<br>3 18 R-1x16<br>appear in (                            | Commen<br>OC18 inclue<br>-1-0-1-2-0"                                   | P 158<br>Cisco<br>t Status X<br>des "or per | ANSI/TIA              | -604-18-A | . design |      | CIS 18 A |

| Cl 167<br>Ran, Adee<br>Comment<br>The va<br>1-0 or<br>These<br>Also in<br>Suggested | SC<br>Type<br>Ilue/co<br>FOCIS<br>do not<br>0 OC19        | <b>167.11.4.6</b><br><b>T</b><br>mment for (<br>5 18 R-1x16<br>t appear in (<br>0.<br>dy              | Commen<br>OC18 incluo<br>-1-0-1-2-0"<br>the reference                  | P 158<br>Cisco<br>t Status X<br>des "or per | ANSI/TIA<br>use 167.1 | -604-18-A | ι design |      | CIS 18 A |

| Cl 167<br>Ran, Adee<br>Comment<br>The va<br>1-0 or<br>These<br>Also in<br>Suggested | SC<br>Type<br>ilue/co<br>FOCIS<br>do not<br>OC19<br>Remed | <b>167.11.4.6</b><br><b>T</b><br>mment for 4<br>3 18 R-1x16<br>t appear in 1<br>0.<br>dy<br>ie/commen | Commen<br>OC18 incluc<br>S-1-0-1-2-0"<br>the reference<br>t and the su | P 158<br>Cisco<br>t Status X<br>des "or per | ANSI/TIA<br>use 167.1 | -604-18-A | . design |      | CIS 18 A |

| C/ 167     | SC 167.11.      | 4.6 P158                       | L13 | # 116 |

|------------|-----------------|--------------------------------|-----|-------|

| 0/ 10/     | 30 107.11.      | 4.6 / 158                      | 213 | # 116 |

| Dawe, Pie  | rs              | Nvidia                         |     |       |

| Comment    | Type E          | Comment Status X               |     |       |

| These      | PICS need wo    | rk to align them to the clause |     |       |

| Suggested  | Remedy          |                                |     |       |

| Remov      | ving Option A v | vill make this task simpler    |     |       |

| Proposed I | Response        | Response Status 0              |     |       |

## Fiber optics cabling Comments 13, 14, 116 (part 2)

#### D1.1 167.11.4.6 PICS Table

| Item        | Feature                                                                                    | Subclause         | Value/Comment                                                                                                                              | Status                                                   | Support                          |

|-------------|--------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|

|             |                                                                                            |                   |                                                                                                                                            |                                                          |                                  |

| OC5         | MDI layout for<br>400GBASE-VR4 and<br>400GBASE-SR4                                         | 167.10.3.1<br>a   | Optical lane assignments per<br>Figure 167–8                                                                                               | (VR4 or<br>SR4):M                                        | Yes [ ]<br>N/A [ ]               |

| <u>OC5a</u> | MDI layout for<br>800GBASE-VR8 and<br>800GBASE-SR8<br>option A                             | 167.10.3.1<br>a   | Optical lane assignments per<br>Figure 167–8a                                                                                              | <u>(VR8 or</u><br><u>SR8):M</u>                          | <u>Yes</u> []<br><u>N/A[]</u>    |

| <u>OC5b</u> | MDI layout for<br>800GBASE-VR8 and<br>800GBASE-SR8<br>option B                             | 167.10.3.1<br>a   | Optical lane assignments per<br>Figure 167–8a                                                                                              | <u>(VR8 or</u><br><u>SR8):M</u>                          | <u>Yes</u> []<br><u>N/A[]</u>    |

| OC6         | MDI mating,<br>100GBASE-VR1 and<br>100GBASE-SR1,<br>with duplex optical<br>fiber connector | 167.10.3.2        | MDI optically mates with plug on<br>the cabling, performance grade<br>Bm/2m                                                                | (VR1 or<br>SR1):M                                        | Yes [ ]<br>N/A [ ]               |

|             |                                                                                            |                   |                                                                                                                                            |                                                          |                                  |

| OC15        | MDI requirements,<br>with multifiber<br>connector                                          | 167.10.3.3        | Per IEC 63267-1, performance<br>grade Bm/1m                                                                                                | INS and (VR1,<br>SR1, VR2, SR2,<br>VR4, or<br>SR4):AFI:M | Yes [ ]<br>N/A [ ]               |

| <u>OC16</u> | MDI mating, with<br>multifiber connector                                                   | 167.10.3.4        | MDI optically mates with plug on<br>the cabling, performance grade<br>Bm/2m                                                                | (VR8 or<br>SR8):AFI:M                                    | <u>Yes []</u><br>N/A[]           |

| <u>OC17</u> | MDI dimensions.<br>with multifiber<br>connector                                            | <u>167.10.3.4</u> | Per IEC 61754-7-1 interface 7-1-3<br>or interface 7-1-10                                                                                   | (VR8 or<br>SR8):AFI:M                                    | <u>Yes []</u><br>N/A[]           |

| <u>OC18</u> | MDI dimensions,<br>with multifiber<br>connector                                            | <u>167.10.3.4</u> | Per IEC 61754-7-2 interfaces<br>7-2-3 or 7-2-10, or per<br>ANSI/TIA-604-18-A designation<br>FOCIS 18 A-1-0 or<br>FOCIS 18 R-1x16-1-0-1-2-0 | (VR8 or<br>SR8):AFI:M                                    | <u>Yes</u> []<br><u>N/A[]</u>    |

| <u>OC19</u> | Cabling connector<br>dimensions, with<br>multifiber connector                              | <u>167.10.3.4</u> | Per IEC 61754-7-2 interface 7-2-4<br>or ANSI/TIA-604-18-A<br>designation<br>FOCIS 18 P-1x16-1-0-2-2-0                                      | INS*(VR8 or<br>SR8):AFI:M                                | <u>Yes[]</u><br><u>N/A[]</u>     |

| <u>OC20</u> | MDI requirements,<br>with multifiber<br>connector                                          | <u>167.10.3.4</u> | Per IEC 61753-1 and IEC<br>61753-022-2, performance grade<br>Bm/2m                                                                         | INS*(VR8 or<br>SR8):AFI:M                                | <u>Yes</u> [ ]<br><u>N/A [ ]</u> |

### Fiber optics cabling Comments 13, 14, 116 (part 3)

#### Proposed D1.2 167.11.4.6 PICS Table

| Item        | Feature                                                                                    | Subclause          | Value/Comment                                                               | Status                                                   | Support                       |

|-------------|--------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|

|             |                                                                                            |                    |                                                                             |                                                          |                               |

| OC5         | MDI layout for<br>400GBASE-VR4 and<br>400GBASE-SR4                                         | 167.10.3.1         | Optical lane assignments per<br>Figure 167–8                                | (VR4 or<br>SR4):M                                        | Yes [ ]<br>N/A [ ]            |

| <u>OC5a</u> | MDI layout for<br>800GBASE-VR8 and<br>800GBASE-SR8<br>option A                             | <u>167.10.3.1a</u> | Optical lane assignments per<br>Figure 167–8a                               | <u>(VR8 or</u><br><u>SR8):M</u>                          | <u>Yes[]</u><br><u>N/A[]</u>  |

| <u>OC5b</u> | MDI layout for<br>800GBASE-VR8 and<br>800GBASE-SR8<br>option B                             | <u>167.10.3.1a</u> | Optical lane assignments per<br>Figure 167–8a                               | <u>(VR8 or</u><br><u>SR8):M</u>                          | <u>Yes[]</u><br><u>N/A[]</u>  |

| OC6         | MDI mating,<br>100GBASE-VR1 and<br>100GBASE-SR1,<br>with duplex optical<br>fiber connector | 167.10.3.2         | MDI optically mates with plug<br>on the cabling, performance<br>grade Bm/2m | (VR1 or<br>SR1):M                                        | Yes [ ]<br>N/A [ ]            |

|             |                                                                                            |                    | -                                                                           |                                                          |                               |

| OC15        | MDI requirements,<br>with multifiber<br>connector                                          | 167.10.3.3         | Per IEC 63267-1, performance<br>grade Bm/1m                                 | INS and (VR1,<br>SR1, VR2, SR2,<br>VR4, or<br>SR4):AFI:M | Yes [ ]<br>N/A [ ]            |

| <u>OC16</u> | MDI mating, with<br>multifiber connector                                                   | <u>167.10.3.4</u>  | MDI optically mates with plug<br>on the cabling, performance<br>grade Bm/2m | (VR8 or<br>SR8):!AFI:M                                   | <u>Yes[]</u><br>N/A[]         |

| <u>OC17</u> | MDI mating, with<br>multifiber connector                                                   | <u>167.10.3.4</u>  | MDI optically mates with plug<br>on the cabling, performance<br>grade Bm/1m | (VR8 or<br>SR8):AFI:M                                    | <u>Yes[]</u><br>N/A[]         |

| <u>OC18</u> | MDI dimensions.<br>with multifiber<br>connector                                            | <u>167.10.3.4</u>  | Per IEC 61754-7-2 interface<br>7-2-3 or interface 7-2-10                    | (VR8 or<br>SR8):!AFI:M                                   | <u>Yes[]</u><br><u>N/A[]</u>  |

| <u>OC19</u> | MDI dimensions.<br>with multifiber<br>connector                                            | <u>167.10.3.4</u>  | Per IEC 61754-7-4 interface<br>7-4-7 or interface 7-4-9                     | (VR8 or<br>SR8):AFI:M                                    | <u>Yes[]</u><br><u>N/A[]</u>  |

| <u>OC20</u> | Cabling connector<br>dimensions, with<br>multifiber connector                              | <u>167.10.3.4</u>  | Per IEC 61754-7-2 interface<br>7-2-4                                        | INS*(VR8 or<br>SR8):!AFI:M                               | <u>Yes</u> []<br><u>N/A[]</u> |

| Item        | Feature                                                       | Subclause         | Value/Comment                                                      | Status                     | Support                        |

|-------------|---------------------------------------------------------------|-------------------|--------------------------------------------------------------------|----------------------------|--------------------------------|

| <u>OC21</u> | Cabling connector<br>dimensions, with<br>multifiber connector | <u>167.10.3.4</u> | Per IEC 61754-7-4 interface<br>7-4-1                               | INS*(VR8 or<br>SR8):AFI:M  | <u>Yes []</u><br><u>N/A []</u> |

| <u>OC22</u> | MDI requirements.<br>with multifiber<br>connector             | <u>167.10.3.4</u> | Per IEC 61753-1 and<br>IEC 61753-022-2, performance<br>grade Bm/2m | INS*(VR8 or<br>SR8):!AFI:M | <u>Yes</u> []<br><u>N/A[]</u>  |

| <u>OC23</u> | MDI requirements,<br>with multifiber<br>connector             | <u>167.10.3.4</u> | Per IEC 63267-1, performance<br>grade Bm/1m                        | INS*(VR8 or<br>SR8):AFI:M  | <u>Yes</u> []<br><u>N/A[]</u>  |

## Fiber optics cabling Comments 13, 14, 116 (part 4)

Proposed D1.2 PICS Table Updates

- •

- The value/comments of OC16 through OC23 now align with the updated text in 167.10.3.4

- The use of !AFI for flat connectors and AFI for angled connectors is consistent with 802.3db-2022

| OC14 | MDI requirements,<br>with multifiber<br>connector | 167.10.3.3 | Per IEC 61753-1 and<br>IEC 61753-022-2, performance<br>grade Bm/2m | INS and (VR1,<br>SR1, VR2, SR2,<br>VR4, or<br>SR4):!AFI:M | Yes [ ]<br>N/A [ ] |

|------|---------------------------------------------------|------------|--------------------------------------------------------------------|-----------------------------------------------------------|--------------------|

| OC15 | MDI requirements,<br>with multifiber<br>connector | 167.10.3.3 | Per IEC 63267-1, performance<br>grade Bm/1m                        | INS and (VR1,<br>SR1, VR2, SR2,<br>VR4, or<br>SR4):AFI:M  | Yes [ ]<br>N/A[ ]  |

• The resolution of comment #115 could affect the final PICS table

# Clause 173

## PCSL Grouping Comment #84

Dawe, Piers

Nvidia

# 84

(bucket1)

L 51

Comment Type T Comment Status D

Adapt the PCSL (PCS lane) formatted signal to the appropriate number of abstract or physical lanes

P212

#### SuggestedRemedy

Adapt the PCSL (PCS lane) formatted signal to the appropriate number and grouping of abstract or physical lanes

Proposed Response Response Status W

PROPOSED ACCEPT IN PRINCIPLE.

The constrained grouping of lanes is part of the "adapt" process and does not need to be listed as a detail here. Instead, this detail is specified in 173.4. The proposed change is not necessary.

However, the acronym PCSL is not properly introduced in this clause. Change "PCSL (PCS lane)" to "PCS lane (PCSL)".

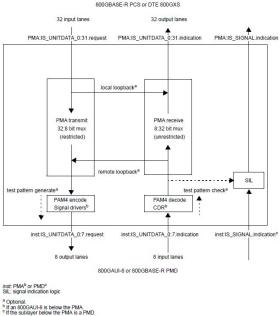

#### Figure 173–1—800GBASE-R PMA relationship to the ISO/IEC Open Systems Interconnection (OSI) reference model and IEEE 802.3 Ethernet model

#### 173.1.3 Summary of functions

The following is a summary of the principal functions implemented (when required) by the PMA in both the transmit and receive directions:

- Adapt the PCSL (PCS lane) formatted signal to the appropriate number of abstract or physical lanes

- Provide per input-lane clock and data recovery

- Provide bit-level multiplexing

212 Copyright © 2022 IEEE. All rights reserved. This is an unapproved IEEE Standards draft, subject to change

|                   | mendment to IEEE Std 802.3-2022 IEEE Draft P802.3df<br>802.df 400 Gb/s and 800 Gb/s Ethernet Task Force 20 December                       |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <u></u>           | Provide clock generation                                                                                                                  |       |

| 1                 | Provide signal drivers                                                                                                                    |       |

| -                 | Optionally provide local loopback to/from the PMA service interface                                                                       |       |

|                   | Optionally provide remote loopback to/from the PMD service interface                                                                      |       |

|                   | Optionally provide test-pattern generation and detection                                                                                  |       |

|                   | Tolerate Skew Variation                                                                                                                   |       |

| 10 <del>-30</del> | Perform PAM4 encoding and decoding                                                                                                        |       |

| 85-75             | Provide receive link status information in the receive direction                                                                          |       |

| 173.1             | .4 PMA sublayer positioning                                                                                                               |       |

|                   | plementation may use one or more PMA sublayers to adapt the number and rate of the PCSLs t                                                |       |

|                   | er and rate of the PMD lanes. The number of PMA sublayers required depends on the partitionin<br>onality for a particular implementation. | ng of |

| Figure            | e 173-2 shows examples of the PMA sublayer positioning for implementations with an 8000                                                   | GMII  |

54

•---

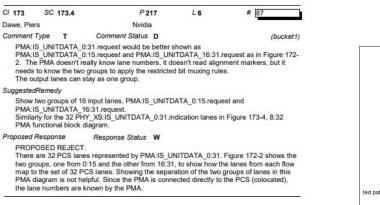

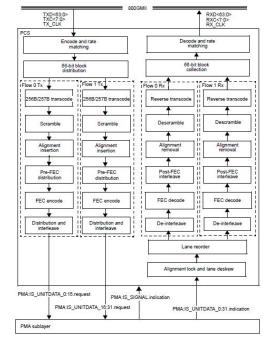

### PCSL Grouping Comment #87

| Figure 173-3 |

|--------------|

| (PMA Clause) |

### Figure 172-2 (PCS Clause)

Figure 173-3-32-8 PMA functional block diagram

Figure 172-2—Functional block diagram

### Link Status Comment #85

| C/ 173                           | SC 173.1               | 1.3                                                                      | P 213         | L 10              | # 85            |          |

|----------------------------------|------------------------|--------------------------------------------------------------------------|---------------|-------------------|-----------------|----------|

| Dawe, Pier                       | rs                     | N                                                                        | vidia         |                   | 5.5             |          |

| Comment                          | Туре Т                 | Comment Sta                                                              | tus D         |                   | (1              | bucket1) |

| forware<br>"Provide<br>that whet | ded.<br>de receive lir | (800GAUI-8) receive<br>nk status information i<br>ed to a PHY XS, it pro | in the receiv | ve direction": do | we need another |          |

| Suggested<br>Per co              | Remedy                 |                                                                          |               |                   |                 |          |

| Proposed                         | Response               | Response Stat                                                            | tus W         |                   |                 |          |

|                                  |                        |                                                                          |               |                   |                 |          |

#### PROPOSED REJECT.

The opening sentence in 173.1.3 states "The following is a summary of the principal functions implemented (when required) by the PMA in both the transmit and receive directions." The phrase "when required" implies that some of the functions listed are conditional upon the PMA type. The requirement for each of the functions listed is specified per PMA type in 173.4.

### Section 171.1.3

#### 173.1.3 Summary of functions

The following is a summary of the principal functions implemented (when required) by the PMA in both the transmit and receive directions:

- Adapt the PCSL (PCS lane) formatted signal to the appropriate number of abstract or physical lanes

- Provide per input-lane clock and data recovery

- Provide bit-level multiplexing

212 Copyright © 2022 IEEE. All rights reserved. This is an unapproved IEEE Standards draft, subject to change.

Draft Amendment to IEEE Std 802.3-2022 IEEE P802.df 400 Gb/s and 800 Gb/s Ethernet Task Force IEEE Draft P802.3df/D1.1 20 December 2022

- Provide clock generation

- Provide signal drivers

- Optionally provide local loopback to/from the PMA service interface

- Optionally provide remote loopback to/from the PMD service interface

- Optionally provide test-pattern generation and detection

- Tolerate Skew Variation

- Perform PAM4 encoding and decoding

- Provide receive link status information in the receive direction

# Clause 172

### Test pattern control Comment #79 (part 1)

C/ 172 SC 172.2.4.9

P 202

L 52

Comment Type T Comment Status D test pattern This mentions the test-pattern control register (bit 3.42.3). But does 3.42.7 Scrambled idle test-pattern apply also?

Nvidia

#### SuggestedRemedy

Dawe, Piers

Please clarify, and please refer to 172.3.1 PCS MDIO function mapping

Proposed Response Response Status W

PROPOSED REJECT.

!! pulled from bucket #1 !!

The pattern selection bits were implemented for lower rate PCS specifications (e.g., 10GBASE-R) where the PCS supported more than one pattern type. For the 100GBASE-R, 200GBASE-R, 400GBASE-R, and now 800GBASE-R PCS, only one pattern is supported, so a separate bit to select a pattern type is not required. The bit 3.42.7 defined in 45.2.3.19.1 is not specified for use with any PCS in the base standard. The scrambled idle pattern is therefore enabled or disabled using bit 3.42.3 only.

#### 172.2.4.9 Test-pattern generators

The PCS shall have the ability to generate a scrambled idle test pattern, which is suitable for receiver tests and for certain transmitter tests. When a scrambled idle pattern is enabled, the test pattern is generated by the PCS. The scrambled idle test pattern is the output of the PCS when the input to the PCS at the 800GMII is a control block with all idle characters.

If a Clause 45 MDIO is implemented, then control of the test-pattern generation is from the BASE-R PCS test-pattern control register (bit 3.42.3).

#### 45.2.3.19 BASE-R PCS test-pattern control register (Register 3.42)

The assignment of bits in the BASE-R PCS test-pattern control register is shown in Table 45–248. This register is only required when the BASE-R capability is supported. If both BASE-R and 10GBASE-W capability is supported, then this register may either ignore writes and return zeros for reads when in 10GBASE-W mode or may function as defined for BASE-R. PRBS9, PRBS31, pseudo random, and square wave test patterns are defined for 10GBASE-R PCS only. Scrambled idle test patterns are defined for 25/40/50/100/200/400GBASE-R PCS only. The test-pattern methodology is described in 49.2.8 and 82.2.11.

#### Table 45-248-BASE-R PCS test-pattern control register bit definitions

| Bit(s)    | Name                                                             | Description                                                                                                           | R/W <sup>a</sup> |

|-----------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|

| 3.42.15:8 | Reserved                                                         | Value always 0                                                                                                        | RO               |

| 3.42.7    | Scrambled idle test-pattern enable                               | 1 = Enable scrambled idle test-pattern mode<br>0 = Disable scrambled idle test-pattern mode                           | R/W              |

| 3.42.6    | Single Lane PHY BASE-R<br>PRBS9 transmit<br>test-pattern enable  | 1 = Enable PRBS9 test-pattern mode on the transmit path<br>0 = Disable PRBS9 test-pattern mode on the transmit path   | R/W              |

| 3.42.5    | Single Lane PHY BASE-R<br>PRBS31 receive<br>test-pattern enable  | 1 = Enable PRBS31 test-pattern mode on the receive path<br>0 = Disable PRBS31 test-pattern mode on the receive path   | R/W              |

| 3.42.4    | Single Lane PHY BASE-R<br>PRBS31 transmit<br>test-pattern enable | 1 = Enable PRBS31 test-pattern mode on the transmit path<br>0 = Disable PRBS31 test-pattern mode on the transmit path | R/W              |

| 3.42.3    | Transmit test-pattern<br>enable                                  | 1 = Enable transmit test pattern<br>0 = Disable transmit test pattern                                                 | R/W              |

| 3.42.2    | Receive test-pattern enable                                      | 1 = Enable receive test-pattern testing<br>0 = Disable receive test-pattern testing                                   | R/W              |

| 3.42.1    | Test-pattern select                                              | 1 = Square wave test pattern<br>0 = Pseudo random test pattern                                                        | R/W              |

| 3.42.0    | Data pattem select                                               | 1 = Zeros data pattem<br>0 = LF data pattern                                                                          | R/W              |

<sup>a</sup>RO = Read only, R/W = Read/Write

## Test pattern control Comment #79 (part 2)

Proposed changes...

In 45.2.3.19, with appropriate editing instructions amend the last sentence in the first paragraph to:

"Scrambled idle test patterns are defined for 25/40/50/100/200/400/<u>800GBASE-R PCS</u> only. The test-pattern methodology is described in 49.2.8, 82.2.11. and 172.2.4.9."

Change 172.2.4.9 as follows:

#### 172.2.4.9 Test-pattern generators

The PCS shall have the ability to generate a scrambled idle test pattern, which is suitable for receiver tests and for certain transmitter tests. When test pattern generation a scrambled idle pattern is enabled (tx\_test\_mode is 1), the scrambled idle test pattern is generated by the PCS. The scrambled idle test pattern is the output of the PCS when the input to the PCS at the 800GMII is a control block with all idle characters. If a Clause 45 MDIO is implemented, then control of the test-pattern generation is from the BASE-R PCS test-pattern control register (bit 3.42.3) the tx\_test\_mode variable is accessible through the register as shown in Table 172-5.

### Stateless encoder / decoder Comments #20, 24

| C/ 172      | SC 172.2.4.1 | .1 P 198         | L 40 | # 20              |

|-------------|--------------|------------------|------|-------------------|

| Ran, Adee   |              | Cisco            |      |                   |

| Comment Typ | e TR         | Comment Status D |      | stateless enc-dec |

Table 172-1 column "T\_TYPE (tx\_raw\_i-1)" has cells with the strings "C + T" and "S + D". These seem to be based on the state diagram convention that "+" is a logical-OR, but this is not a state diagram, and the letters are not conditions, so it isn't very clear. Using "or" would be preferable (as in the similar Table 172–4).

In addition, for each of these two strings there are two rows with two values in "T\_TYPE (tx\_raw\_i)" column; these can be merged with the word "or" as well.

SuggestedRemedy

$\begin{array}{l} \mbox{Merge rows 2 and 5 to a single row with columns:} \\ \mbox{"0 | C or T | C or S | ENCODE (bc_raw_i)".} \\ \mbox{Merge rows 3 and 4 to a single row with columns:} \\ \mbox{"0 | S or D | D or T | ENCODE (bc_raw_i)".} \\ \end{array}$

### **Existing tables**

#### Table 172-1-PCS stateless encoder rules

#### T TYPE (tx raw<sub>i-1</sub>)<sup>a</sup> T TYPE (tx raw;)b Resulting tx cod ed reset any block type any block type LBLOCK T C + TS ENCODE (tx raw,) S+D D ENCODE (tx raw.) S+D Т ENCODE (tx raw.) C + TC ENCODE (tx raw,) any combination not listed above EBLOCK T

### Suggested remedy

#### Table 172-1-PCS stateless encoder rules

| reset | T_TYPE (tx_raw <sub>i-1</sub> ) <sup>a</sup> | T_TYPE (tx_raw <sub>i</sub> ) <sup>b</sup> | Resulting tx_cod ed           |

|-------|----------------------------------------------|--------------------------------------------|-------------------------------|

| 1     | any block type                               | any block type                             | LBLOCK_T                      |

| 0     | C or T                                       | S or C                                     | ENCODE (tx_raw <sub>i</sub> ) |

| 0     | S or D                                       | D or T                                     | ENCODE (tx_rawi)              |

| 0     | any combination                              | EBLOCK_T                                   |                               |

C/ 172 SC 172.2.5.8.1 P 204 L 23 # 24

Comment Type TR Comment Status D stateless enc-dec

In Table 172-4, row 3, column "R\_TYPE (rx\_coded\_i)", the value is "S or D or T or C".

The possible R\_TYPE values (based on 119.2.6.2.3) are C, LI, S, T, D, and E, LI is not valid for clause 172 (per 172.2.3, EEE and low power idle are not supported). Therefore, "S or D or T or C' is equivalent to "not E". This excludes only the combination "E | E".

However, the combination "E | E" matches the second row, and therefore results in the same  $x_r$  raw, EBLOCK\_R. So having R\_TYPE( $rx_c$  coded\_i-1)=E with any value of R\_TYPE( $rx_c$  coded\_i) would result in EBLOCK\_R.

This means the table can be simplified and made more readable.

SuggestedRemedy

Change the third row to the following contents: "0 | E | any block type | EBLOCK\_R".

#### Table 172-4-PCS stateless decoder rules

| r eset | $R_TYPE (rx_coded_{i-1})^a$      | R_TYPE (rx_cod ed_)b | Resulting rx_raw     |

|--------|----------------------------------|----------------------|----------------------|

| 1      | any block type                   | any block type<br>E  | LBLOCK_R<br>EBLOCK_R |

| 0      | any block type                   |                      |                      |

| 0      | E                                | S or D or T or C     | EBLOCK_R             |

| 0      | any combination not listed above |                      | DECODE (rx_coded;)   |

#### Table 172-4-PCS stateless decoder rules

| rese | t | R_TYPE (rx_coded <sub>i-1</sub> ) <sup>a</sup> | R_TYPE (rx_coded,)b | Resulting rx_raw   |

|------|---|------------------------------------------------|---------------------|--------------------|

| 1    |   | any block type                                 | any block type      | LBLOCK_R           |

| 0    |   | any block type                                 | E                   | EBLOCK_R           |

| 0    |   | E                                              | any block type      | EBLOCK_R           |

| 0    |   | any combination not listed above               |                     | DECODE (rx_coded;) |

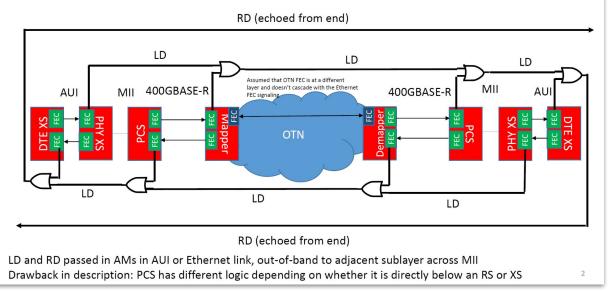

# **Cross-Clause**

## FEC Degrade Comments 17, [<u>55</u>, 56], 59

Consensus View on how FEC degrade signaling should work OTN mapper contribution to FEC degrade signaling is for ITU to decide, but LD, RD must be propagated whether or not the FEC decoder in the OTN mapper contributes to the accumulated LD status

https://www.ieee802.org/3/bs/public/17\_03/trowbridge\_3bs\_01\_0317.pdf

- FEC degrade signals should be retained.

- FEC degrade signal can propagate through OTN network.

- Both FEC degrade signals and FEC bin counters can be used to determine the link quality.

## Multiplexing rules Comments [<u>27</u>, 89, 92] - (part 1)

• Three comments were received proposing additional PMA multiplexing constraints above and beyond what was agreed to in the adopted baseline:

https://www.ieee802.org/3/df/public/22\_10/22\_1004/shrikhande\_3df\_01a\_221004.pdf

- Comment #6 against Draft 1.0 made a similar proposal. Straw polls recorded in the response to comment #6 indicated favor for adopting the proposal but there were many votes for "need more information", and more consensus building was necessary.

- A new presentation provides more information on the problem (ran\_3df\_01\_2301) and suggests essentially the same remedy (with minor editorial changes).

## Multiplexing rules Comments [27, 89, 92] - (part 2)

Below is the final response to D1.0 comment #6, including the results of the straw poll.

#### REJECT.

The current text and constrainted PCSL multiplexing requirement is consistent with the adopted baseline (see slides 17&18 in https://www.ieee802.org/3/df/public/22 10/22 1004/shrikhande 3df 01a 221004.pdf).

The following presentation was reviewed by the task force: https://www.ieee802.org/3/df/public/22\_12/ran\_3df\_01a\_2212.pdf

Based on straw polls #1 and #2 there is no consensus to make the proposed changes at this time. The commenter is encouraged to refine the proposal and build consensus,

Straw poll #1 (direction) I would support the changes proposed on slides 10 in ran\_3df\_01a\_2212. Yes: 19 No: 6 Need more information: 27

Straw poll #2 (direction) I would support the changes proposed on slides 11 in ran\_3df\_01a\_2212. Yes: 13 No: 6 Need more information: 33

### Suggested remedy (modified) – part 1

#### 173.4.2.1 32:8 PMA bit-level multiplexing

Change the second list item as shown:

- The multiplexing function has an additional constraint that each of the 8 output lanes contain two unique PCSLs from PMA client lanes i = 0 to 15 and followed by two unique PCSLs from PMA client lanes i = 16 to 31

#### 173.4.2.2 8:32 PMA bit-level multiplexing

Change the second list item as shown:

The multiplexing function has an additional constraint that each of the 8 output lanes contain two unique PCSLs from service interface lanes i = 0 to 15 and followed by two unique PCSLs from service interface lanes i = 16 to 31.

### Suggested remedy (modified) – part 2

#### 173.4.2.3 8:8 PMA bit-level multiplexing

Change the second list item as shown:

- The 4 PCSLs received on any input lane shall be mapped together to an output lane <u>such that the Gray-coded</u> PAM4 symbol sequence on the output is identical to the Gray-coded PAM4 symbol sequence on the input (see <u>173.4.7.1).-The order of PCSLs from an input lane does not have to be maintained on the output lane.</u>