# FEC Options for 200G/Lane DRn, DRn-2, and FR1

Piers Dawe, Bill Simms, and Vishnu Balan NVIDIA

# Acknowledgements

- Contributors

- **Bill Simms NVIDIA**

- Tony Zortea NVIDIA

- **Piers Dawe NVIDIA**

- Vishnu Balan NVIDIA

- Supporters

- John Calvin Keysight

- Roberto Rodes Coherent

- Vipul Bhatt Coherent

- Leon Bruckman Huawei

- Yan Zhuang Huawei

- Jonathan Ingham Huawei

- Pavel Zivny Tektronix

- Xiang He Huawei

- Guangcan Mi Huawei

# Objectives

- Add optional support for SD-FEC Bypass when not needed to reduce power and latency

- Avoid convolutional interleaver to minimize latency

Revisit a low-latency end-to-end FEC option for DR channels at 200G/lane Leverage existing 100G/lane infrastructure and simply double the bandwidth

# Review – farhood\_3df\_02b\_2211

**Reviewed FEC architectures**

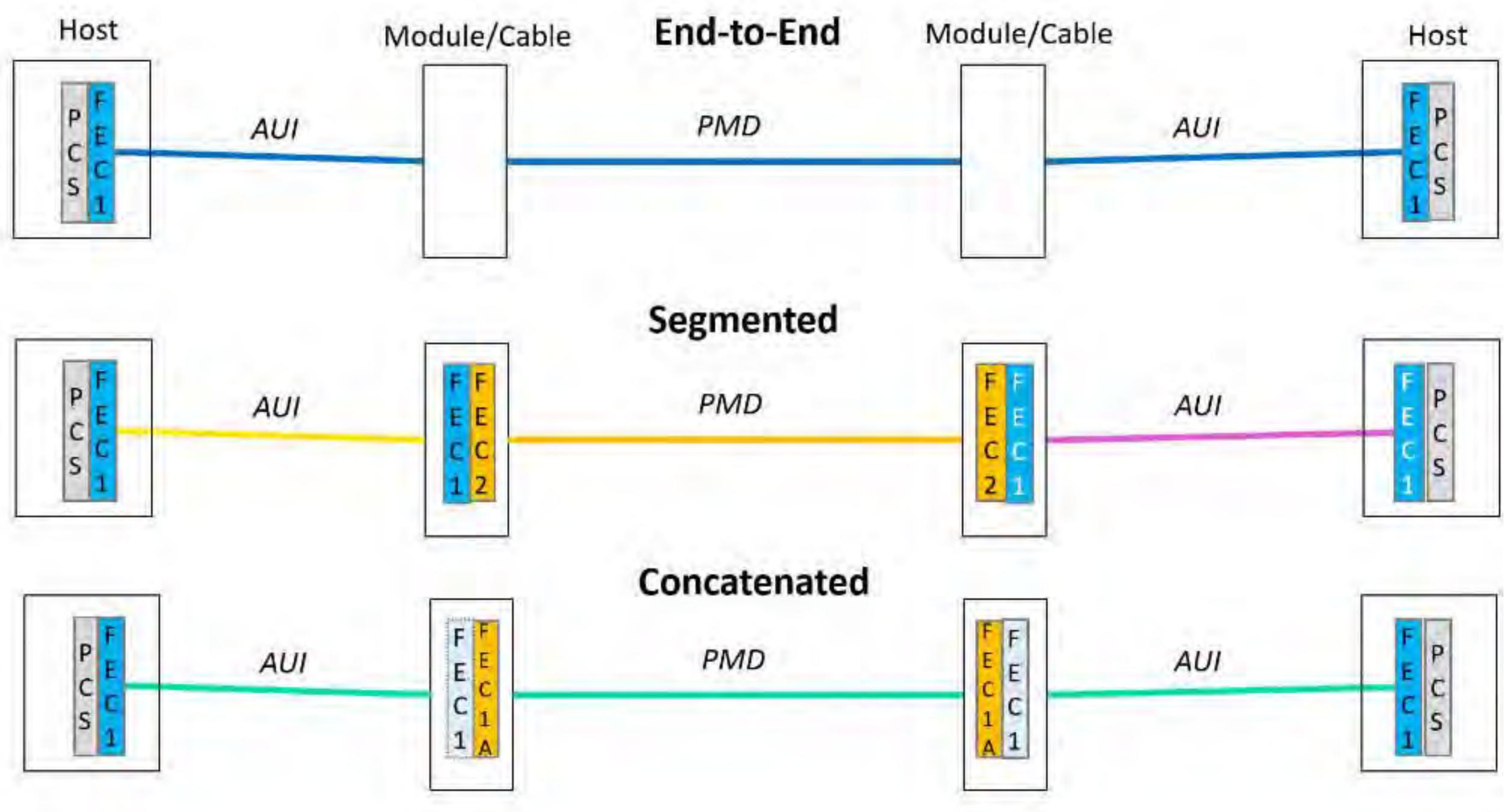

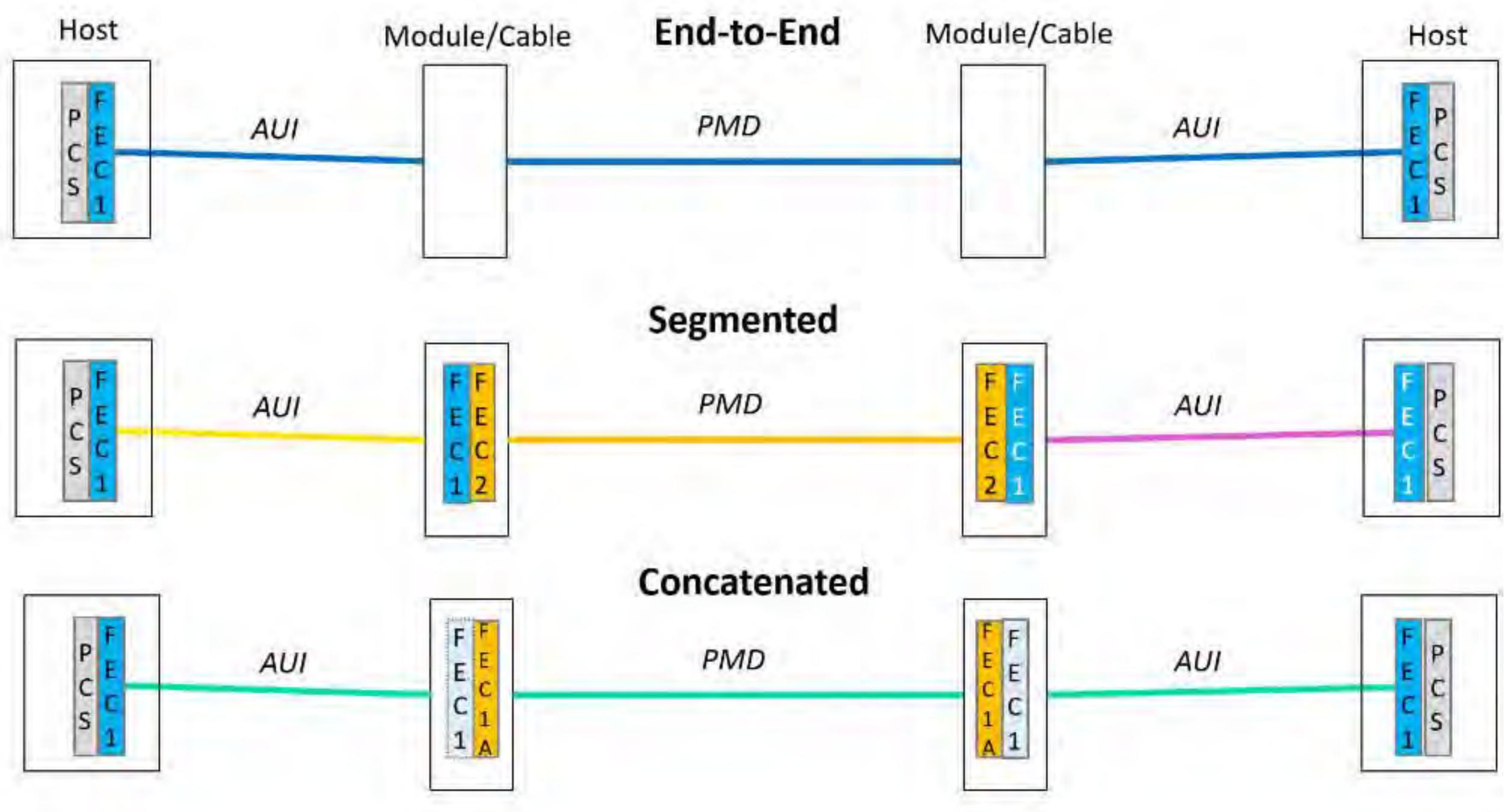

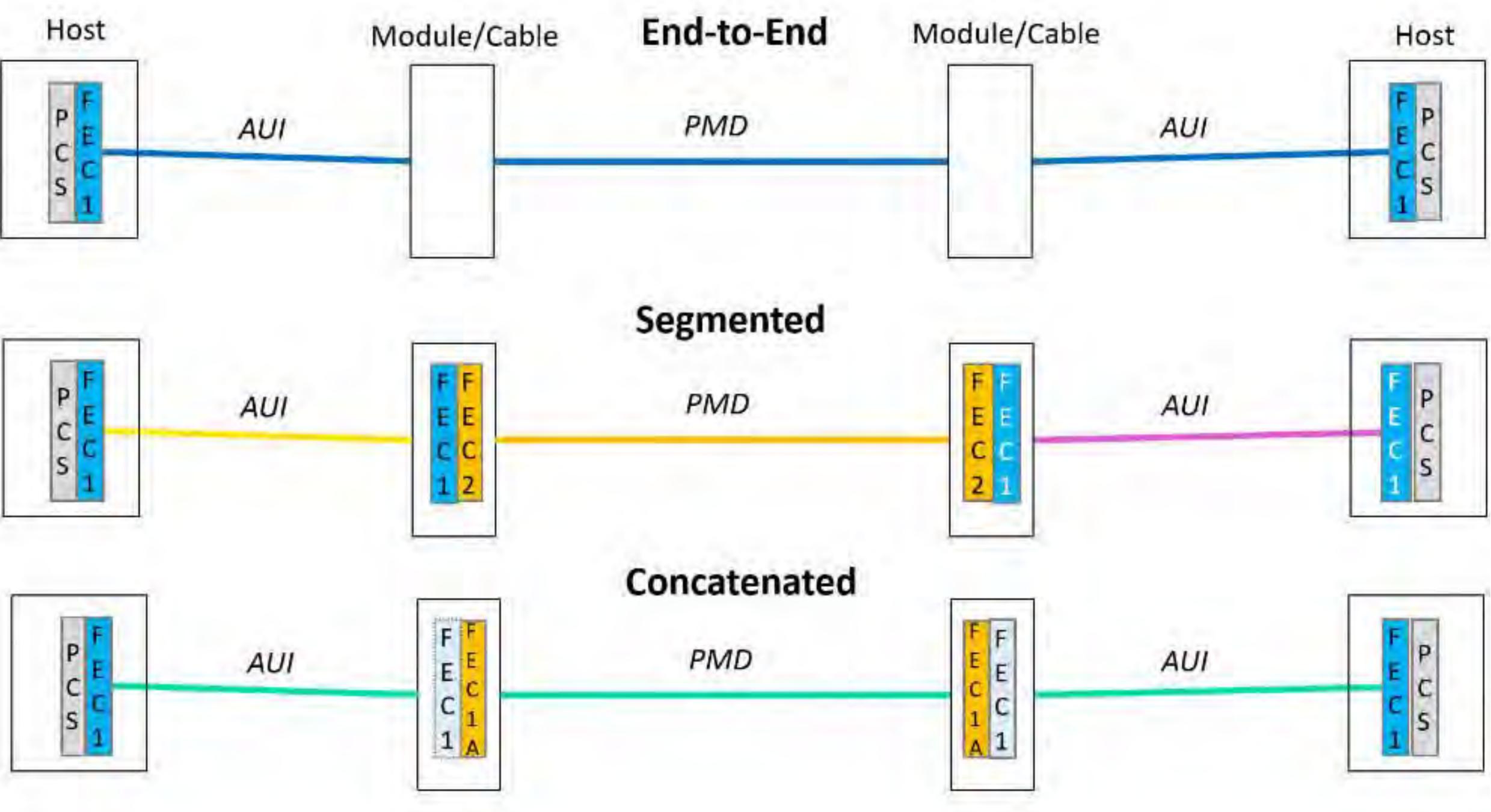

# Refresh of FEC Architecture already discussed in this forum: End-to-End, Segmented, Concatenated scheme

FEC 1: is end-to-end (AUI+PMD+AUI)

FEC 1: AUI only FEC 2: PMD only

FEC 1 (outer) FEC: (AUI + PMD + AUI)**Optional PMD FEC1** FEC 1A (inner) FEC: (PMD only)

#### Concatenated FEC could be bypassed to provide End-to-End RS544

### **Review – he\_3dj\_02a\_230206** Demonstrates latency increases due to use of convolutional interleaver, hard decision, and soft decision inner FEC

# Tradeoff Between Latency and Pre-FEC BER Threshold

- 0

- ۰

- - Bypass configuration can either be static or configurable.

| BER<br>Threshold | Bypass Convo.<br>Interleaver | Bypass<br>Inner Code | Inner Code Decoder:<br>Soft or Hard Decision | Inner Code<br>Total Latency |

|------------------|------------------------------|----------------------|----------------------------------------------|-----------------------------|

| 4.6E-3           | No                           | No                   | Soft                                         | 50~300 ns                   |

| 3.3E-3           | Yes                          | No                   | Soft                                         | 5~10 ns*                    |

| 6.1E-4           | Yes                          | No                   | Hard                                         | 1~2 ns*                     |

| 2.4E-4           | Yes                          | Yes**                |                                              | 0 ns*                       |

\*Based on 200G/lane throughput, same for all Ethernet rates from 200 GbE to 1.6 TbE. \*\*Bypassing inner code will lead to different PMD rate.

Inner code itself does not require the convolutional interleaver to work. Concatenated code performance without convolutional interleaver has been analyzed in he 3df 01 2211.pdf. For links that has lower pre-FEC BER levels, convolutional interleaver can be bypassed. 800 GbE PCS layer provides 4 codewords interleaving (likely for 1.6 TbE, too), which can provide moderate protection. For links that meets RS(544,514) threshold, the inner code can be bypassed completely. Tradeoff between latency and pre-FEC BER threshold can be made.

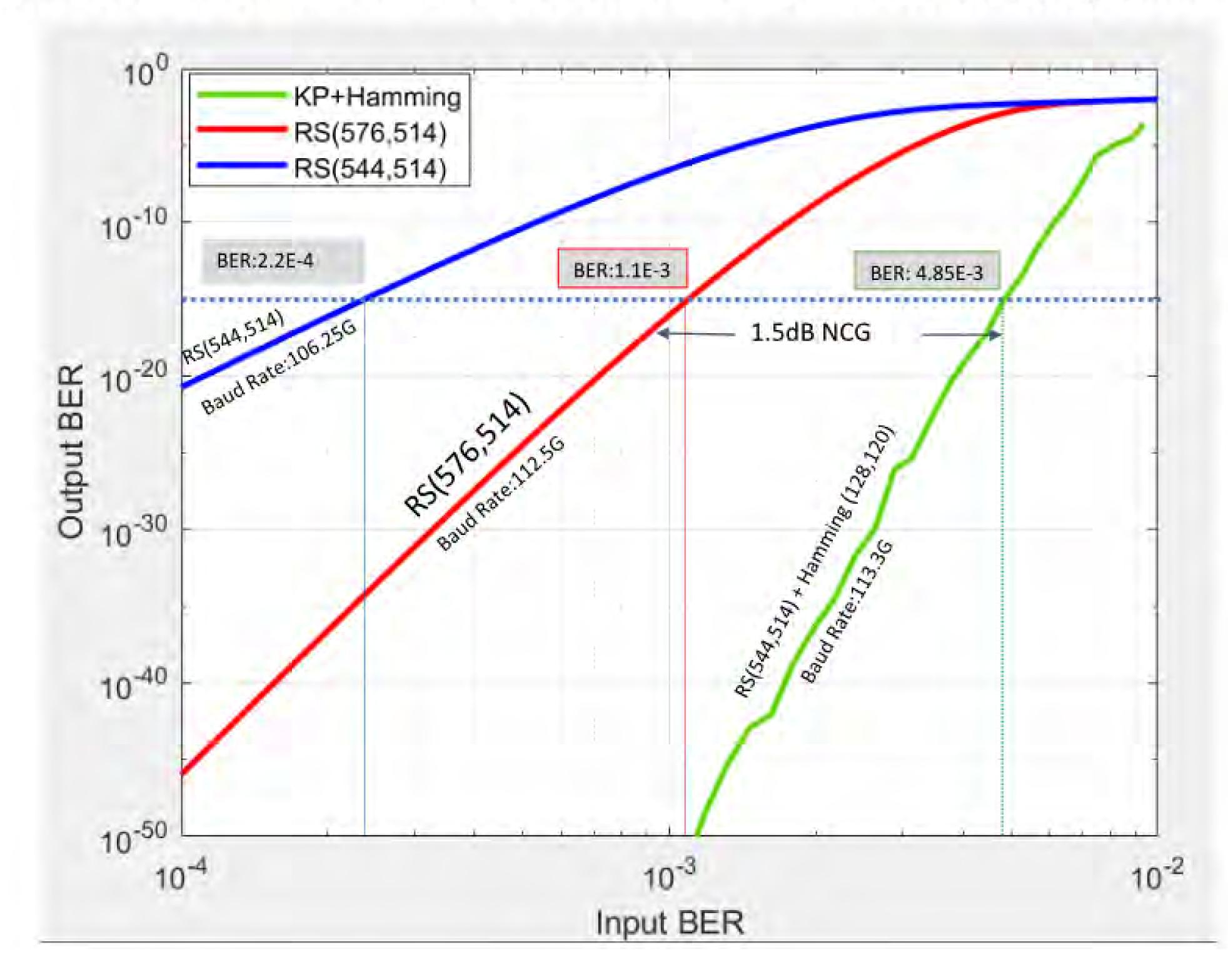

## **Review – patra\_3df\_01\_220518** Demonstrates performance of RS(544,514)+Hamming(128,120) over RS(544,514) alone

Performance of KP4 FEC Vs RS(576,514) Vs KP4 + Hamming (128,120)

KP4 + Hamming (128,120) Vs RS(576,514):

Net Coding gain increase : 1.5dB with very similar overhead

# **Review – simms\_3df\_01\_221005**

No SD-FEC required to operate 800GBASE-DR4 links

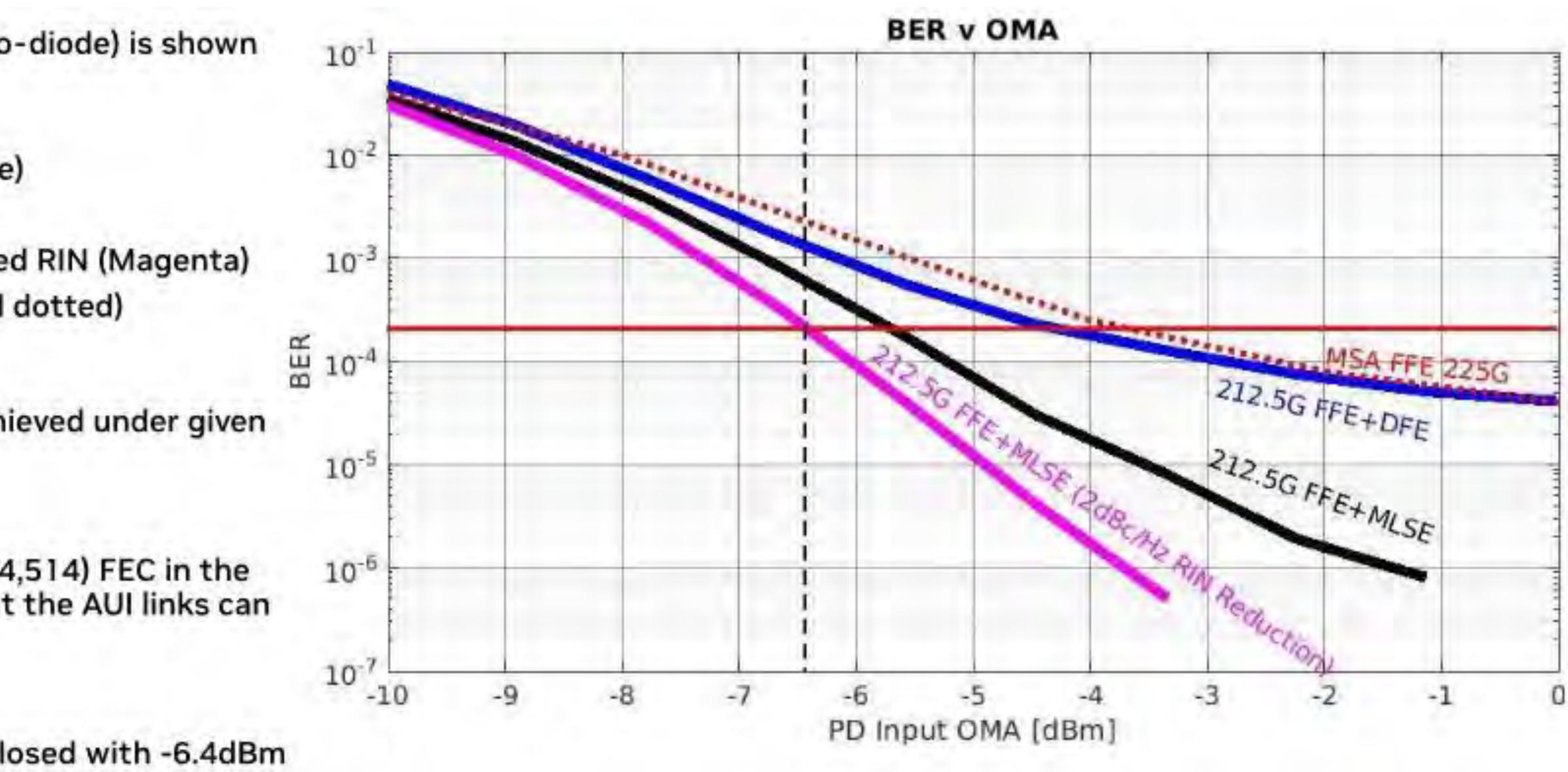

A plot of BER vs. OMA (at the Rx photo-diode) is shown for 212.5 Gbps:

- Baseline EQ : FFE + 1-tap DFE (Blue)

- Advanced EQ: FFE + MLSE (Black)

- Advanced EQ: FFE + MLSE + Reduced RIN (Magenta)

- 800G MSA shown for reference (Red dotted)

BER target of 2 x 10<sup>-4</sup> (Red) can be achieved under given conditions

We can rely on end-to-end KP4 RS(544,514) FEC in the host under the usual assumptions that the AUI links can meet BER of 10<sup>-5</sup> or better

With this example the link budget is closed with -6.4dBm

# Demonstrated feasibility of end-to-end RS544 FEC using improved link parameters

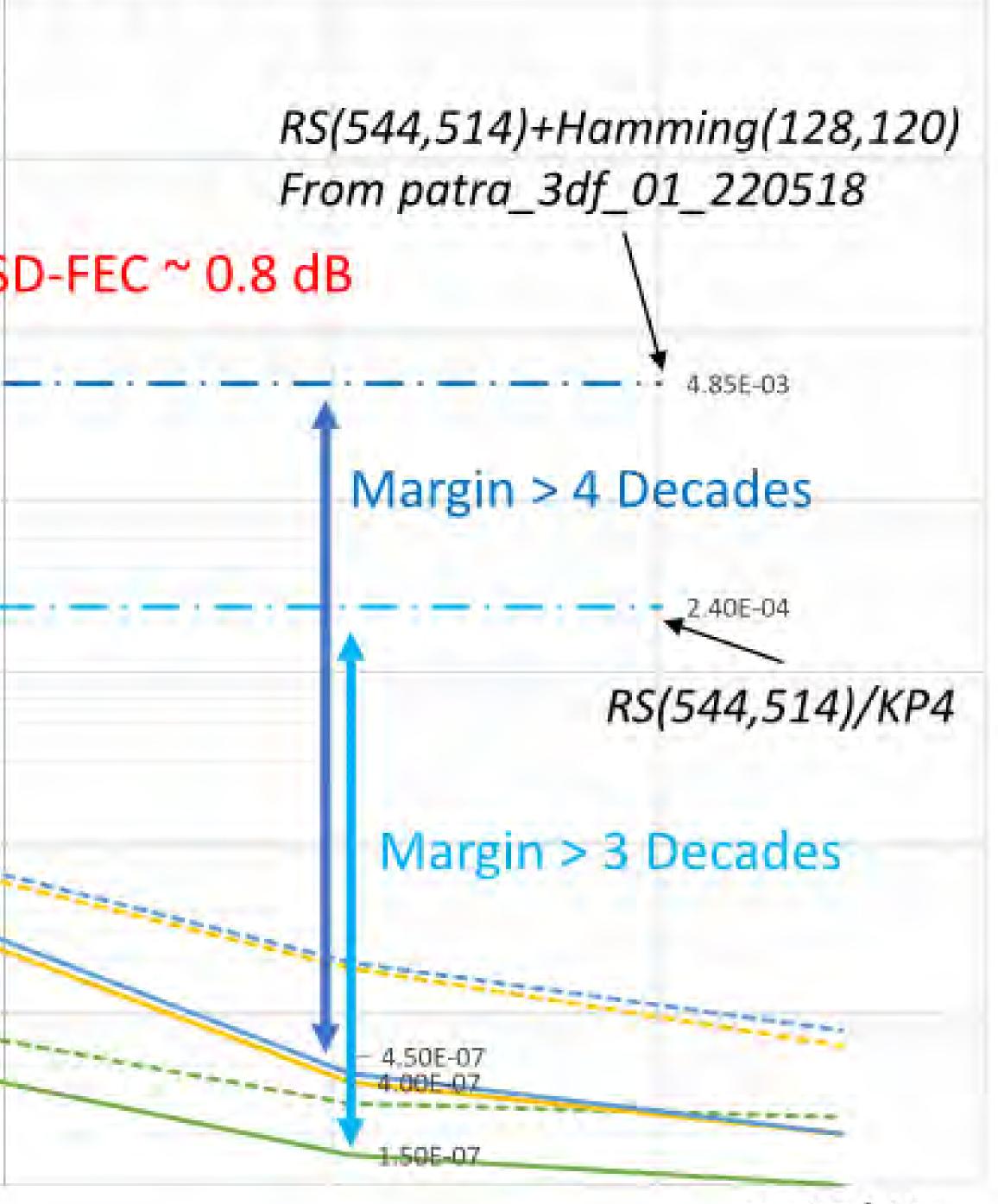

# **Review – welch\_3df\_01a\_221011** Demonstrates FEC options with DFE1 and Rin improved to -137dB/Hz Case 2: Comparisons to FEC Options 1.00E+00 1.00E-01 Net/Effective Coding Gain of SD-FEC ~ 0.8 dB 1.00E-02 1.00E-03 BER 1.00E-04 Green = 106.25 GBD Yellow = 112.5 GBD1.00E-05 Blue = 113.3 GBDDashed = -136 dB/Hz1,00E-06 Solid = $-137 \, dB/Hz$ 1.00E-07

OMA (dBm)

2 dB/div

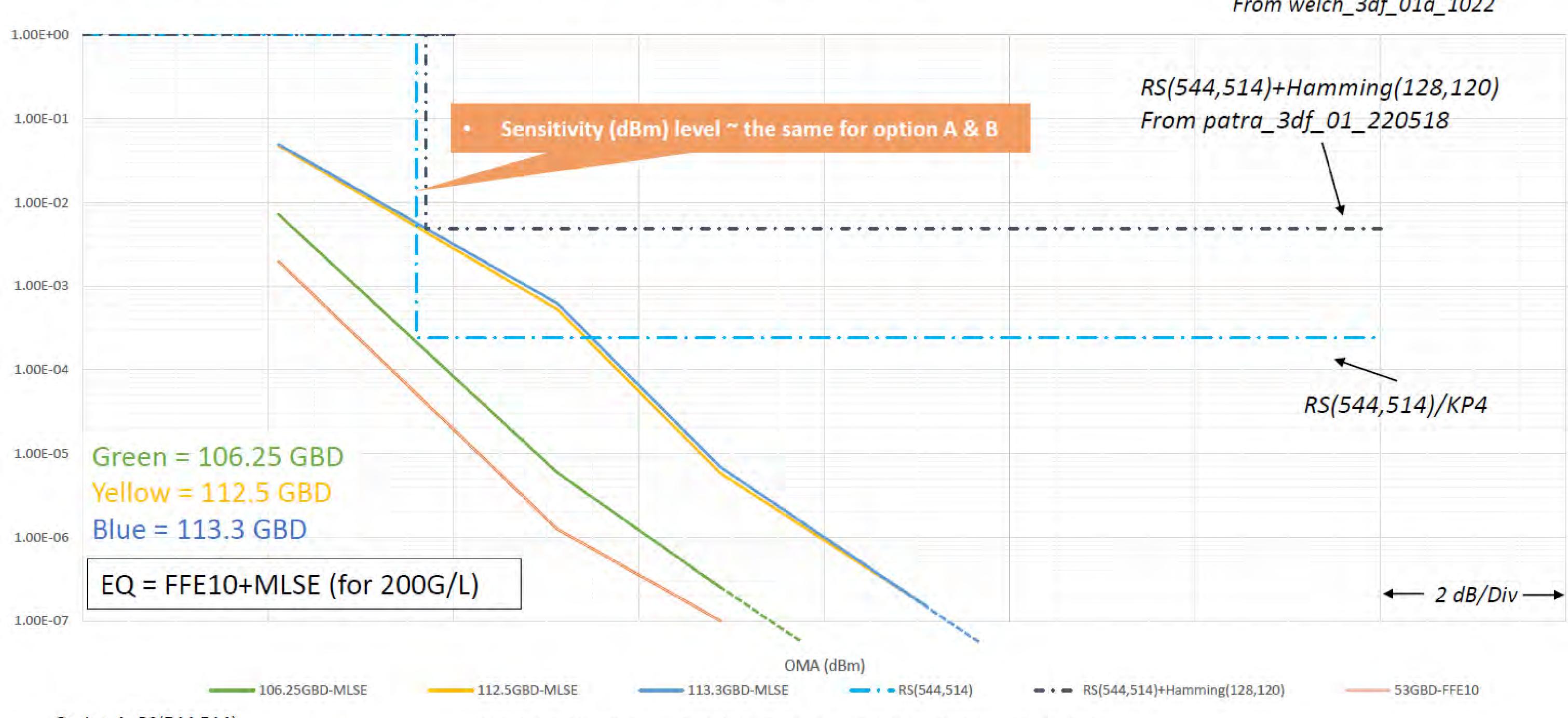

# **Review – welch\_3dj\_01a\_230206** Demonstrates closed link budget with OMA 1dB improved over 100G. SD\_FEC has similar sensitivity level Option A vs. B: Power Levels

Option A: RS(544,514) Option B: RS(544,514) + Hamming Inner

IEEE P802.3dj 200 Gb/s, 400 Gb/s, 800 Gb/s, and 1.6 Tb/s Ethernet Task Force

From welch\_3df\_01a\_1022

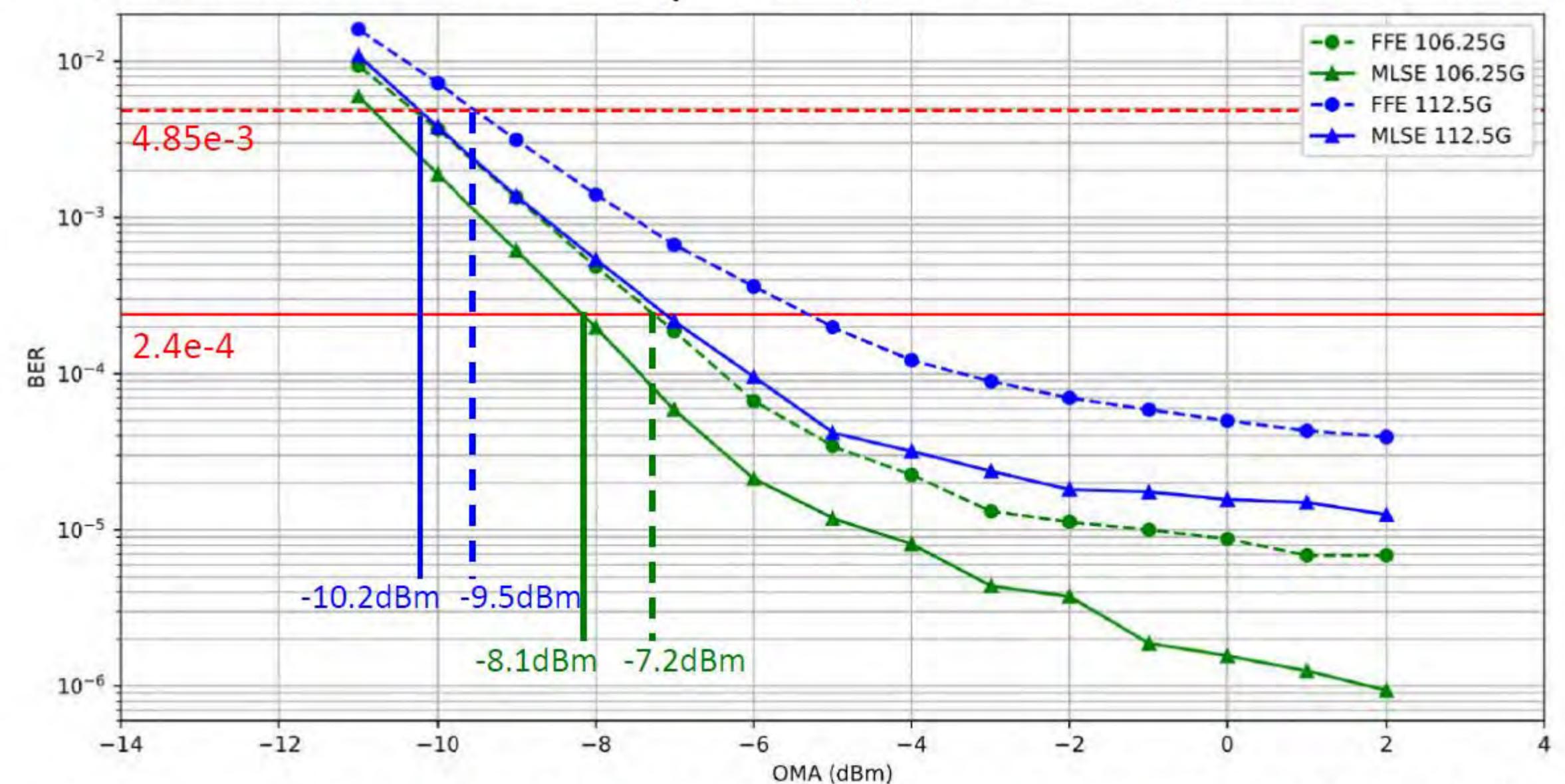

### Review – li\_3dj\_01a\_230206 Feasibility of 106.25 GBd MLSE and FFE (roughly 2 dB OMA margin for inner FEC)

# Simulation results (2km, 106.25/112.5GBd)

-8.1dBm Rx sensitivity with MLSE for 106.25GBd can meet RS(544,514) BER standard -10.2dBm Rx sensitivity for 112.5GBd of RS(544,514)+Hamming(128,120) Considering 1dB EOL aging margin, OMA Rx sensitivities of -7.1dBm and -9.2dBm could be feasible for two signaling rates, respectively

# Conclusion

- SD-FEC in the module for pluggables

- Best for low power and low latency operation

- Reviewed prior presentations which arrive at same conclusion and similar results

- - May allow for design reuse between DR4 and FR4/DR4-2 systems **Requires BW increase and circuit optimization**

# Simulation results for a DR (500 m, SMF) channel which closes the link budget without requiring an

A bypassable SD-FEC (Hamming 128/120) may be used for higher loss systems (FR and DR4-2) where the extra power is needed to guarantee system operation and extra latency can be tolerated

Avoid convolutional interleaver to reduce latency, area, and power

#### References

- - Brian Welch Cisco

# References

"Updates on Concatenated FEC Proposal for 200G/Lane PMD", Lenin Patra – Marvell Semiconductor https://www.ieee802.org/3/df/public/22\_07/patra\_3df\_01a\_2207.pdf "FEC Architecture of B400GbE to Support BER Objective", Xiang He, et al – Huawei Technologies https://ieee802.org/3/B400G/public/21\_05/he\_b400g\_01\_210426.pdf • "DSP and FEC Considerations for 800GbE and 1.6TbE", Yuchun Lu, et al – Huawei Technologies https://www.ieee802.org/3/df/public/22\_02/lu\_3df\_01b\_220215.pdf Baseline Proposals for 800GBASE-DR-4, 800GBASE-DR4-2, and 800GBASE-FR4", Brian Welch – Cisco Inc https://ieee802.org/3/df/public/22\_05/22\_0602/welch\_3df\_01b\_220602.pdf • MSA FFE 225G curve extracted from 800G Pluggable Multi-Source Agreement White Paper https://static.s123-cdn-static-d.com/uploads/2598123/normal\_60d5f55c54664.pdf "Bypass Options for Concatenated FEC", Xiang He, Matt Brown – Huawei Technologies https://www.ieee802.org/3/dj/public/23\_01/23\_0206/he\_3dj\_02a\_230206.pdf • "Baseline proposals for 200G/L PMD specifications for single wavelength 500m and 2km standards",

https://www.ieee802.org/3/dj/public/23\_01/23\_0206/welch\_3dj\_01a\_230206.pdf Consideration on 200G per lane 500m and 2km objectives", Huanlu Li, et al – Huawei Technologies https://www.ieee802.org/3/dj/public/23\_01/23\_0206/li\_3dj\_01a\_230206.pdf

# Thank You