# FEC\_I Sublayer Architecture Proposal for Type 2 PHYs

Xiang He, Hao Ren Huawei Technologies

### Contributors

- Kechao Huang, Huawei

- Xiaoling Yang, Huawei

#### Introduction

- Type 2 PHY/FEC scheme has been adopted with Hamming(128,120) as the inner FEC.

- See parthasarathy 3dj 02a 2303, and motions 3dfdj 2303.

- Detailed design regarding convolutional interleaver and FEC lane rates are TBD.

- Symbol-pair muxing has been adopted for 200G/lane AUIs.

- See <u>ran\_3dj\_01a\_2303</u>, and <u>motions\_3dfdj\_2303</u>.

- Convolutional interleaver has been proposed to randomize errors from inner FEC.

- See patra 3dj 01b 2303.pdf, huang 3df 01a 2211 and he 3dj 01a 230206.pdf.

- Three different lane rates were proposed: 25G/lane, 100G/lane and 200G/lane.

- The convolutional interleaver should be avoided for shorter PMDs due to high latency.

- See <u>he 3dj 02a 230206</u>, <u>dawe 3dj 01a 2303</u>.

- Latency impact has been analyzed in <u>brown 3dj optx 01b 230413</u> and <u>brown 3dj elec 01 230420</u>.

- This presentation focuses on FEC\_I lane rates, and recommend to use 200G/lane design.

- Convolutional interleaver in the following slides could be excluded if not needed.

#### **Architecture Overview**

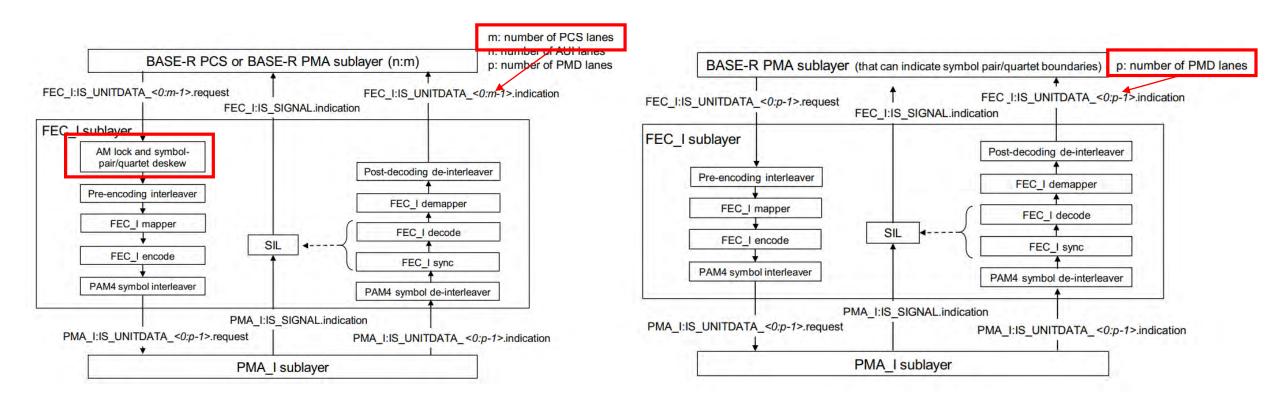

- The three FEC lane designs can be viewed as two main options, one has PCS lane based design, and the other has PMA/PMD lane based design.

- Both options have exactly the same performance in terms of FEC gain.

- Both options have the same number of bits storage for convolutional interleaver if used.

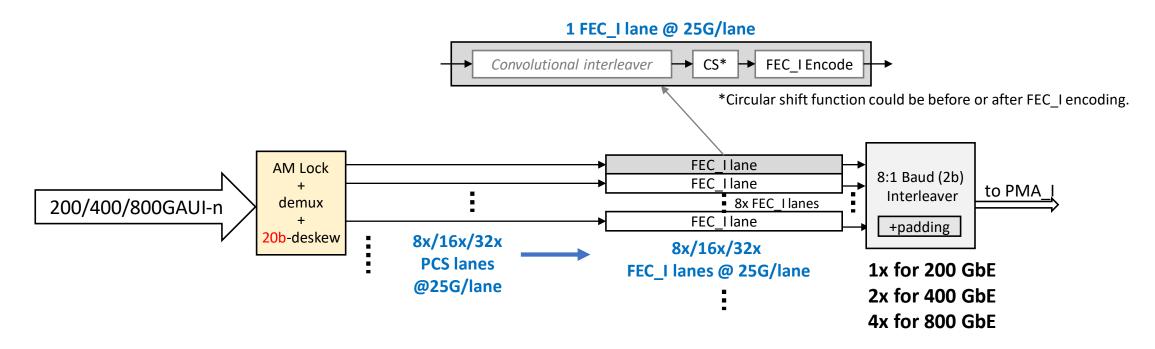

## 25G/lane Design — 200 GbE, 400 GbE and 800 GbE

- Data from AUI is de-muxed to PCS lanes first, and deskewed to RS symbol-pair (20b) boundary.

- FEC\_I sublayer is based on 100G/lane.

- For 200/400/800 GbE, PCS lane rate is 25G/lane, and each has its own FEC\_I lane.

- 8-lane per 200G PMD lane naturally supports 8:1 channel interleaver.

<sup>\*</sup>Highlighted boxes are rate-specific functions.

# 25G/lane Design — 1.6 TbE

- Data from AUI is de-muxed to PCS lanes first, and deskewed to RS symbol-quartet (40b) boundary.

- FEC\_I sublayer is based on 100G/lane.

- For 1.6 TbE, each PCS lane rate is 100G, and each needs to be split into 4x25G "virtual" lanes.

- 4x25G virtual lanes need to be recombined back to a PCS lane on Rx side.

<sup>\*</sup>Highlighted boxes are rate-specific functions.

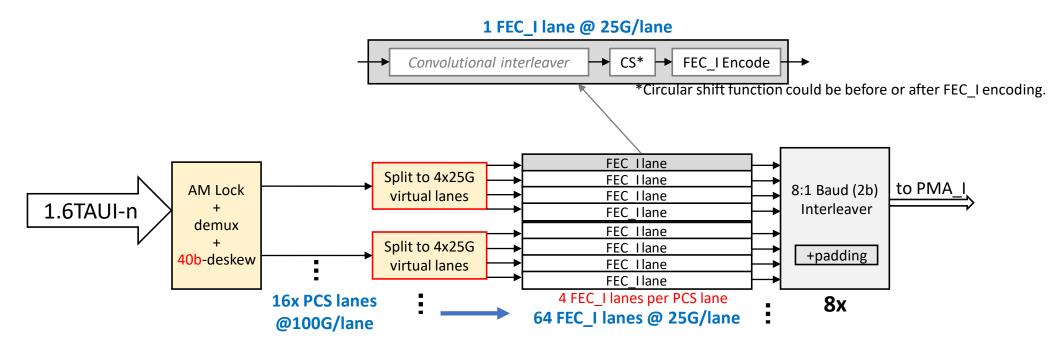

### 100G/lane Design — 200 GbE, 400 GbE and 800 GbE

- Data from AUI is de-muxed to PCS lanes first, and deskewed to RS symbol-pair (20b) boundary.

- FEC\_I sublayer is based on 100G/lane.

- For 200/400/800 GbE, a 4:1 symbol-pair mux is needed for each FEC\_I lane.

- 100G/lane design could also support 8:1 (or higher ratio) post-encoding Baud interleaver.

- Circular shift function could be before or after FEC\_I encoding.

<sup>\*</sup>Highlighted boxes are rate-specific functions.

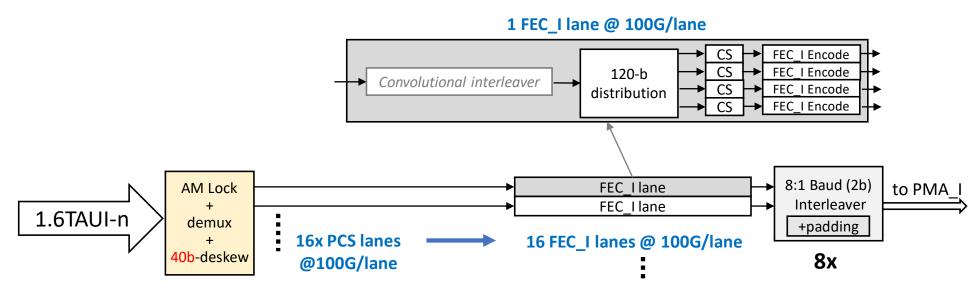

# 100G/lane Design — 1.6 TbE

- Data from AUI is de-muxed to PCS lanes first, and deskewed to RS symbol-quartet (40b) boundary.

- FEC\_I sublayer is based on 100G/lane.

- For 1.6 TbE, each FEC\_I lane takes the 100G/lane PCS input directly.

- 100G/lane design could also support 8:1 (or higher ratio) post-encoding Baud interleaver.

- Circular shift function could be before or after FEC\_I encoding.

- patra\_3di\_optx\_01\_230427 defined single lane CS+FEC\_I encode, but functionally is the same as shown below.

<sup>\*</sup>Highlighted boxes are rate-specific functions.

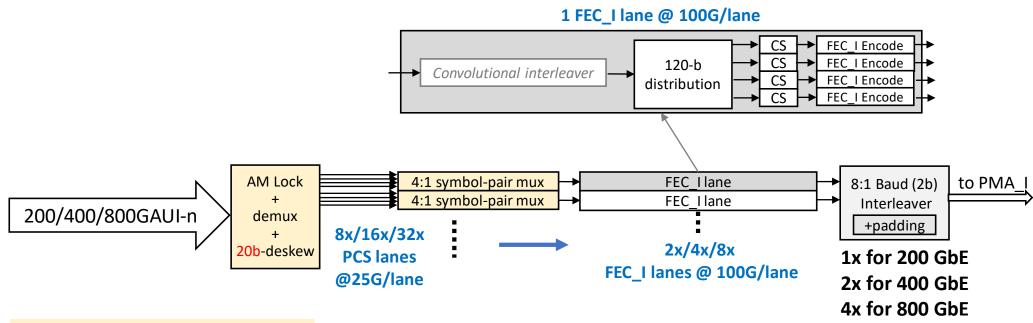

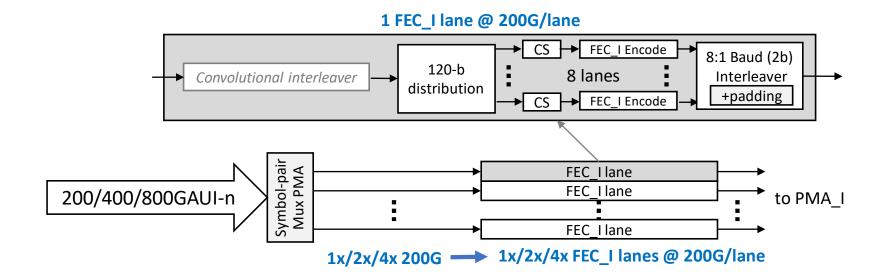

### 200G/lane Design — 200 GbE, 400 GbE and 800 GbE

- Data from AUI is NOT required to be de-muxed to PCS lanes first.

- Relying on the symbol-pair muxing PMA functions to establish FEC\_I lane mapping.

- Maximizing the common functional blocks across different rates.

- 200G/lane design could also support 8:1 (or higher ratio) post-encoding Baud interleaver.

- Circular shift function could be before or after FEC\_I encoding.

<sup>\*</sup>No rate-specific functions.

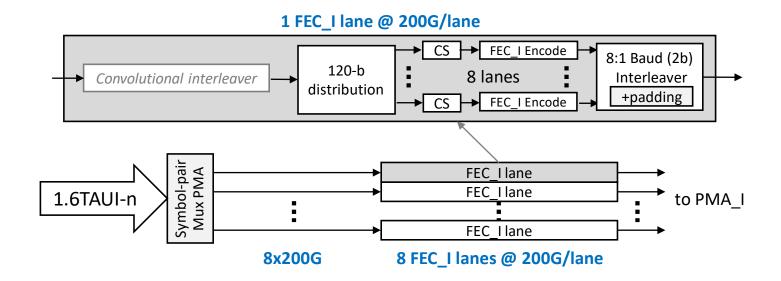

# 200G/lane Design — 1.6 TbE

- Data from AUI is NOT required to be de-muxed to PCS lanes first.

- Relying on the symbol-pair muxing PMA functions to establish FEC\_I lane mapping.

- Maximizing the common functional blocks across different rates.

- 200G/lane design could also support 8:1 (or higher ratio) post-encoding Baud interleaver.

- Circular shift function could be before or after FEC\_I encoding.

<sup>\*</sup>No rate-specific functions.

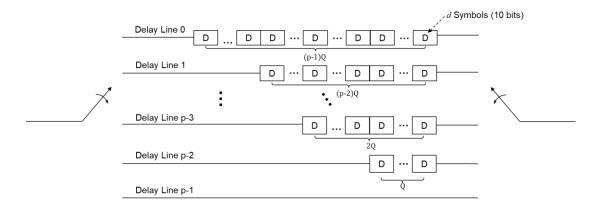

# 200G/lane Convolutional Interleaver Design

- 200G/lane FEC\_I design could utilize the same design blocks across different rates.

- 200G/lane convolutional interleaver design has lower latency for most cases.

- For latency sensitive applications, convolutional interleavers should not be used.

| Proposal                 | PCS   | d<br>(RS symbol) | Р | Q  | Depth  | Latency<br>ns | FEC_I Lane Rate |

|--------------------------|-------|------------------|---|----|--------|---------------|-----------------|

| patra_3dj_optx_01_230427 | 1.6TE | 4                | 3 | 11 | 12x RS | 24.85         | 100G/lane       |

|                          | 800GE | 4                | 3 | 6  | 12x RS | 54.21         | 25G/lane        |

|                          | 400GE | 4                | 3 | 6  | 6x RS  | 54.21         |                 |

|                          |       | 2                | 6 | 6  | 12x RS | 135.53        |                 |

|                          | 200GE | 4                | 3 | 11 | 6x RS  | 99.39         |                 |

|                          |       | 2                | 6 | 12 | 12x RS | 271.06        |                 |

| he_3dj_optx_01_230427    | 1.6TE | 4                | 3 | 23 | 12x RS | 25.98         | 200G/lane       |

|                          | 800GE | 4                | 3 | 45 | 12x RS | 50.82         |                 |

|                          | 400GE | 4                | 3 | 45 | 6x RS  | 50.82         |                 |

|                          |       | 2                | 6 | 46 | 12x RS | 129.88        |                 |

|                          | 200GE | 4                | 3 | 91 | 6x RS  | 102.78        |                 |

|                          |       | 2                | 6 | 91 | 12x RS | 256.94        |                 |

### Summary

- The FEC\_I lane rate does not affect the FEC performance.

- However it needs to be defined clearly to ensure interop.

- FEC\_I sublayer designing based on 200G/lane PMA lanes enables unified design across all rates that supports 200G/lane optical PMDs.

- With a single FEC\_I sublayer defined, it could be used to define all Ethernet rates using 200G/lane optics.

# Thank you!