# 802.3dj - CR Considerations for Insertion Loss Budget Baseline

Chris DiMinico

PHY-SI LLC/SenTekse LLC

cdiminico@ieee.org

## **Purpose**

- Consideration for CR insertion loss budget baseline

- Compliance test points and insertion losses

- die-to-die

- Cable assembly, TX/RX, test fixtures

#### **Contributors**

- Michael Rowlands, Sam Kocsis; Amphenol

- Nathan Tracy, Megha Shanbhag; TE Connectivity

- Scott Sommers; Molex

- Adee Ran; Cisco Systems

- Richard Mellitz; Samtec

- Mike Li, Kent Lusted; Intel

## **Supporters**

- Nathan Tracy, Megha Shanbhag; TE Connectivity

- Scott Sommers; Molex

- Mike Li; Intel

- Priyank Shukla; Synopsys

- Ali Ghiasi; Ghiasi Quantum

- Howard Heck; Intel

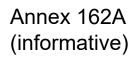

## **CR Compliance Test Points**

- Normative: Cable Assembly, Transmitter, Receiver, Test Fixtures

- Informative: Die-to-die, TP0 to TP5, recommended device package + host IL

#### Table XXX–X—Test points

| Test points                                        | Description                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

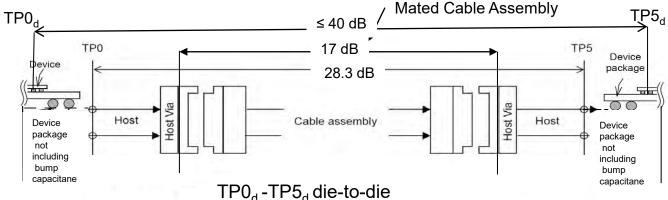

| TP0 <sub>d</sub> to TP5 <sub>d</sub>               | The channel including the device package, the host transmitter and receiver differential controlled impedance PCB insertion loss and the cable assembly insertion loss.                                                                                                       |  |  |

| TP0 to TP5                                         | The channel including the transmitter and receiver differential controlled impedance PCB insertion loss and the cable assembly insertion loss.                                                                                                                                |  |  |

| TP1 to TP4                                         | All cable assembly measurements are made between TP1 and TP4 as illustrated in Figure xxx-x. The cable assembly test fixture of Annex xxxx, or its equivalent, is required for measuring the cable assembly specifications in xxx.x at TP1 and TP4.                           |  |  |

| TP0 <sub>d</sub> to TP2<br>TP3 to TP5 <sub>d</sub> | A mated connector pair has been included in both the transmitter and receiver specifications defined in xxx.x and xxx.x. The recommended maximum insertion loss from TP0 <sub>d</sub> to TP2 or from TP3 to TP5 <sub>d</sub> including the test fixture is provided in xxx.x. |  |  |

| TP2                                                | Unless specified otherwise, all transmitter measurements defined in xxx.x are made at TP2 utilizing the test fixture specified in Annex xxx.                                                                                                                                  |  |  |

| TP3                                                | Unless specified otherwise, all receiver measurements and tests defined in xxxx are made at TP3 utilizing the test fixture specified in Annex xxxx.                                                                                                                           |  |  |

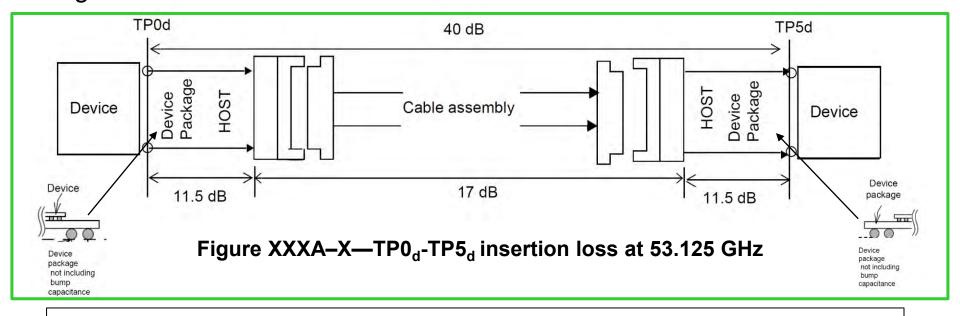

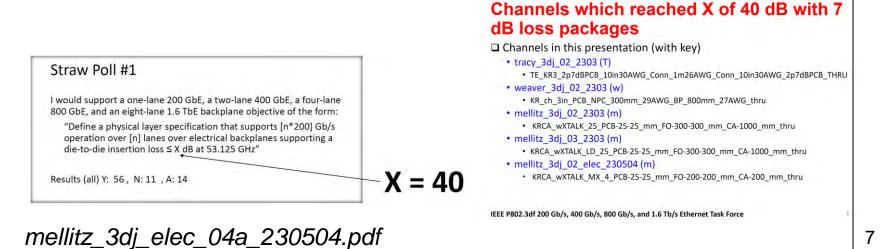

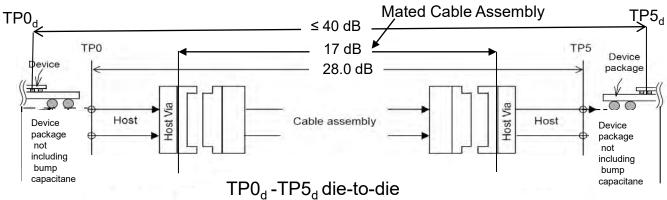

# TP0<sub>d</sub>- TP5<sub>d</sub> Insertion Loss (informative Annex)

Align with KR die-to-die insertion loss ≤ 40 dB

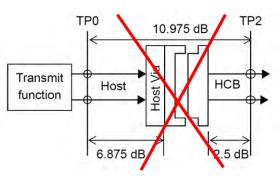

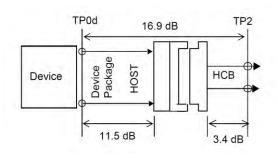

## **TP0<sub>d</sub>-TP2/TP3** Insertion Loss (informative Annex)

- Partition loss budget allocation for device package + host

- No change to test point reference TP2/TP3 i.e., testing of normative TX/RX

#### Table XXX-X—Test points

| Test points                                        | Description                                                                                                                                                                                                                                                               |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP0 <sub>d</sub> to TP5 <sub>d</sub>               | The channel including the device package, the host transmitter and receiver differential controlled impedance PCB insertion loss and the cable assembly insertion loss.                                                                                                   |

| TP0 to TP5                                         | The channel including the transmitter and receiver differential controlled impedance PCB insertion loss and the cable assembly insertion loss.                                                                                                                            |

| TP1 to TP4                                         | All cable assembly measurements are made between TP1 and TP4 as illustrated in Figure xxx-x. The cable assembly test fixture of Annex xxxxx, or its equivalent, is required for measuring the cable assembly specifications in xxxx at TP1 and TP4.                       |

| TP0 <sub>d</sub> to TP2<br>TP3 to TP5 <sub>d</sub> | A mated connector pair has been included in both the transmitter and receiver specifications defined in xxx.x and xxx.x. The recommended maximum insertion loss from TP0 $_{\rm d}$ to TP2 or from TP3 to TP5 $_{\rm d}$ including the test fixture is provided in xxx.x. |

| TP2                                                | Unless specified otherwise, all transmitter measurements defined in xxx.x are made at TP2 utilizing the test fixture specified in Annex xxx.                                                                                                                              |

| TP3                                                | Unless specified otherwise, all receiver measurements and tests defined in xxxx are made at TP3 utilizing the test fixture specified in Annex xxxx.                                                                                                                       |

NOTE—The 11.5 dB ILdd includes allowance for BGA and connector footprint vias.

NOTE—Device package not including bump

capacitance

Figure XXXA–X—TP0<sub>d</sub>-TP2/TP3 Insertion loss at 53.125 GHz

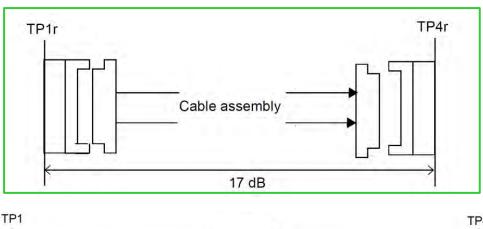

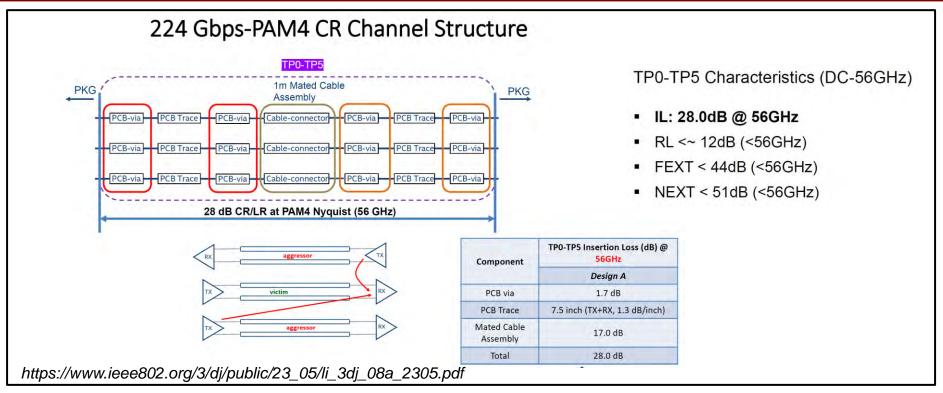

## Mated Cable Assembly - ≤17 dB @ 53.125 GHz

Mated Cable Assembly ≤17 dB @ 53.125 GHz supported by contributions

Source:

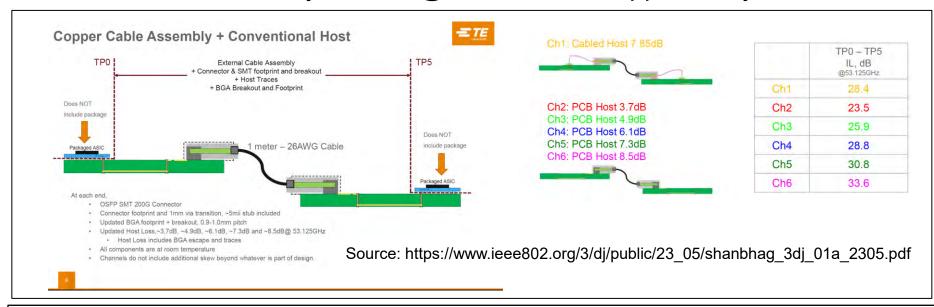

CR Copper Cable Channel Configurations

Amphenol

| Configuration | TP0 Side Host Loss<br>(dB@53.125GHz) | Copper Cable Length (m) | TP5 Side Host Loss<br>(dB@53.125GHz) | TP0-TP5 Loss<br>(dB@53.125GHz) |

|---------------|--------------------------------------|-------------------------|--------------------------------------|--------------------------------|

| 1             | 8                                    | 1                       | 8                                    | 30.75                          |

| 2             | 10                                   | 1                       | 10                                   | 34.51                          |

| 3             | 4                                    | 1.5                     | 4                                    | 26.65                          |

| 4             | 3                                    | 1                       | 9                                    | 26.74                          |

| 5             | 9                                    | 1                       | 3                                    | 26.74                          |

- · Configurations 1 and 2 represent symmetric, switch-switch links

- Configuration 3 represents case with physical reach >1.5m

- · Configurations 4 and 5 represent asymmetric, switch-server links

https://www.ieee802.org/3/dj/public/23\_05/kocsis\_3dj\_01a\_2305.pdf

Package length adjusted to maintain 40dB "die-to-die" in each analysis

### **TP1-TP4 Cable Assembly- Mated Test Fixtures**

- Need further discussions on test fixtures

- inclusion of RF connector

- Time gated propagation delay methods

- Consider test reference points TP1, and TP4,

Adopt cable assembly test point reference pending methodology

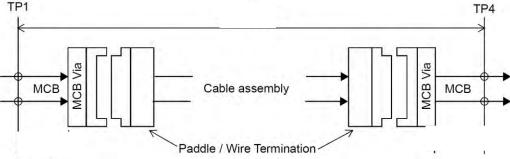

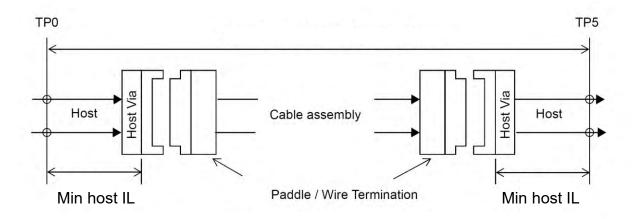

#### TP0-TP5

- XXX.X Transmitter characteristics at TP0

- The recommended transmitter characteristics at TP0 as measured at TP0v are described in XXX.X.

- XXX.X Receiver characteristics at TP5

- The recommended receiver characteristics at TP5 as measured at TP5v are describe in XXX.X.

- TP0-TP5 Min host insertion loss for all cable assemblies

Figure xxxA-x—Minimum Channel insertion loss at 53.125 GHz

# **Supplemental**

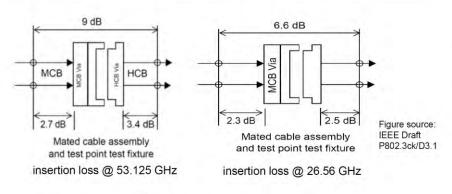

## TP1-TP4,TP2,TP3- tested with compliant fixtures

#### Mated test fixture insertion loss - HFSS model

| Test points              | Description                                                                                                                                                                                                                                          |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TP0 to TP5               | The channel including the transmitter and receiver differential controlled impedance PCB insertion loss and the cable assembly insertion loss.                                                                                                       |  |  |

| TP1 to TP4               | All cable assembly measurements are made between TP1 and TP4 as illustrated in Figure 162–2. The cable assembly test fixture of Annex 162B, or its equivalent, is required for measuring the cable assembly specifications in 162.10 at TP1 and TP4. |  |  |

| TP0 to TP2<br>TP3 to TP5 |                                                                                                                                                                                                                                                      |  |  |

| TP2                      | Unless specified otherwise, all transmitter measurements defined in 162.9.4 are made at TP2 utilizing the test fixture specified in Annex 162B.                                                                                                      |  |  |

| TP3                      | Unless specified otherwise, all receiver measurements and tests defined in 162.9.5 are made at TP3 utilizing the test fixture specified in Annex 162B.                                                                                               |  |  |

Table 162-8-Test points

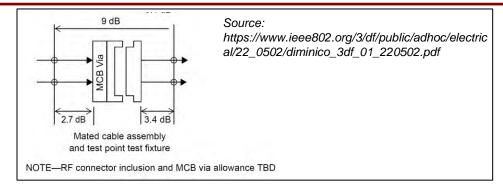

| Component                                                                                                  | Insertion Loss (dB) |  |

|------------------------------------------------------------------------------------------------------------|---------------------|--|

| Module Compliance Board (MCB) PCB - 2" of ~1.35 dB/in                                                      | 2.7                 |  |

| Host Compliance Board (HCB) - 1inch*1.35dB/in + 6inch coax * .28dB/inch + 0.5dB via and co-ax transitions. | 3.4                 |  |

| Mated Test Fixture (MTF)                                                                                   | 9                   |  |

| MTF connector + 2 via's                                                                                    | 2.9                 |  |

Mated test fixture and host insertion loss allocations @ 53.125 GHz

#### Source:

https://www.ieee802.org/3/df/public/adhoc/electrical/22\_0502/diminico\_3df\_01\_220502.pdf

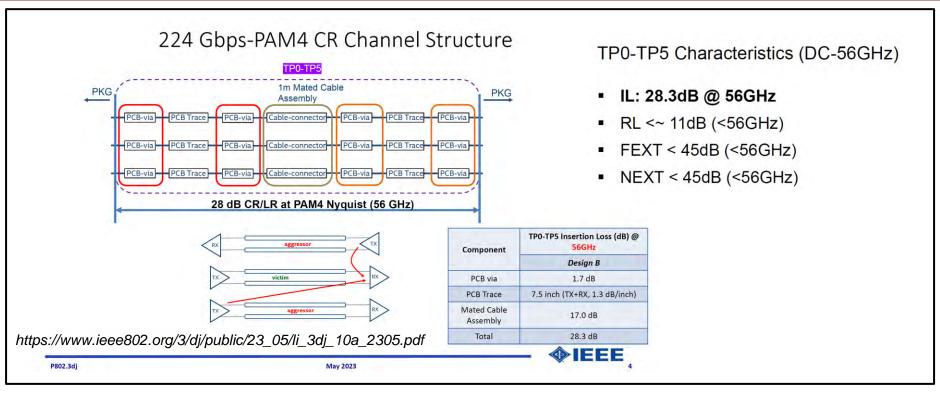

#### A 224 Gbps-PAM4 1 Meter DAC Long Reach Channel and Its Characteristics: Design A

#### A 224 Gbps-PAM4 1 Meter DAC Long Reach Channel and Its Characteristics: Design B