# 212Gb/s Per Lane PAM4 CR Channels with Flexible Host Architectures and Longer Reach Cables - Switch Perspective

James Weaver - Arista Networks Jason Chan - Arista Networks

# **Overview**

- This is a preliminary investigation into a typical CR implementation

- The intent is to facilitate early discussion among participants using realizable channels

- PCB trace s-parameter data measurement procedure similar to Delta-L but using AFR

- All PCB footprints designed using HFSS and conform to the DFM rules of major fabricators

- These models are ball-to-ball to allow use with different package models

- Bump-to-bump channel specification is still critical, owing to large package losses

- Development is continuing, so all models are subject to continuous refinement.

- New channels will be contributed as refinements are made

# **Description**

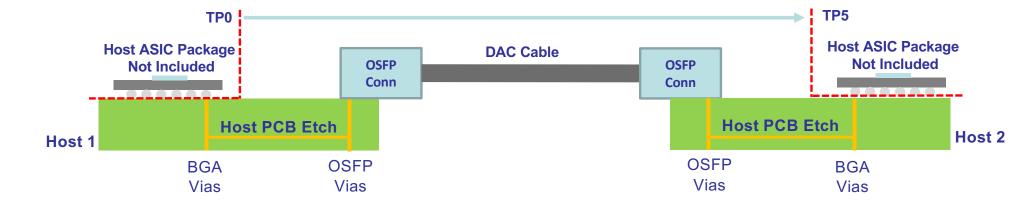

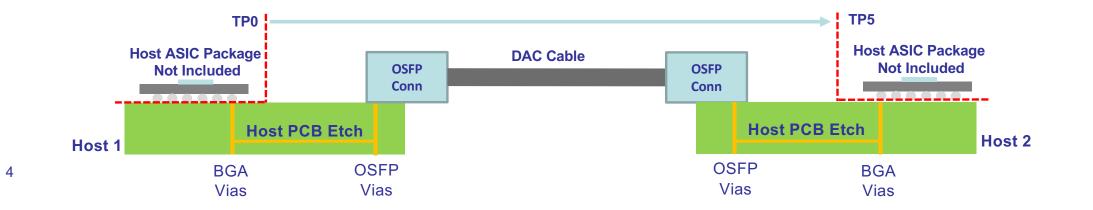

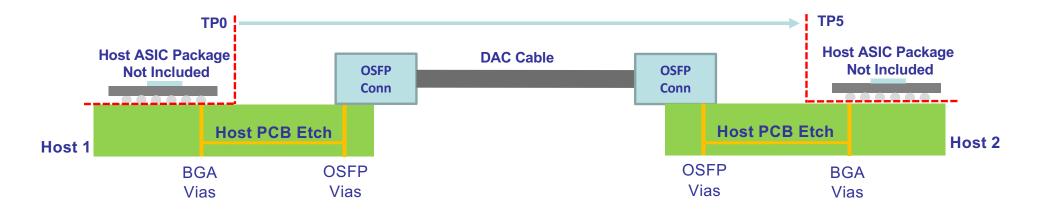

- Simulation of a typical host-to-host CR architecture over various trace lengths where one of the hosts is representative of a large switch

- For NIC perspective, please reference akinwale\_3dj\_01\_2311

- Composition:

3

- BGA / PCB trace / OSFP via escapes simulated with HFSS

- OSFP DAC cable assembly models with mated connectors provided by 3 vendors

- Ball-to-Ball topology: does not include package effects

- This presentation does NOT propose the following:

- Specific aggregate losses

- Specific host architecture implementations

## **Host-to-Module Composition**

- PCB Composition

- BGA & OSFP Breakout Footprints

- ~ 3mm worst-case PTH breakout depth

- 8 mil vias with 5 mil stubs

- Conforms to current PCB fab design rules

- Nothing exotic: no skip layers, no microvias

- Host Breakout Trace

- Fanout lengths to OSFP vias: 2, 3, 5 inches

- Losses @Hi Temp: ~ 1.40 dB/in @ 53.125 GHz

- 90 ohm @ 6 mil line width

- DAC cable Composition

- OSFP 1x1 SMT Connector with DAC 26AWG cable

- Vendors "X", "Y", "Z"

- Room Temperature only models

- Cable Lengths: 0.5m, 1.0m, 1.5m @ 26AWG

- Integrated DAC cable assembly models includes

- OSFP 1x1 connectors with mated module PCB's

- Cable attachment assemblies

- 26AWG twinax cables

- o Vendor 'X': 100 ohms

- Vendor 'Y': 95 ohms

- Vendor 'Z': 92 ohms

## **Asymmetric Host / Cable Combos**

| Host #1 PCB Trace | Cable | Host #2 PCB Trace |

|-------------------|-------|-------------------|

| HH (5 inch)       | 0.5m  | HN (3 inch)       |

| HH (5 inch)       | 1.0m  | HL (2 inch)       |

| HN (3 inch)       | 1.0m  | HN (3 inch)       |

| HN (3 inch)       | 1.5m  | HL (2 inch)       |

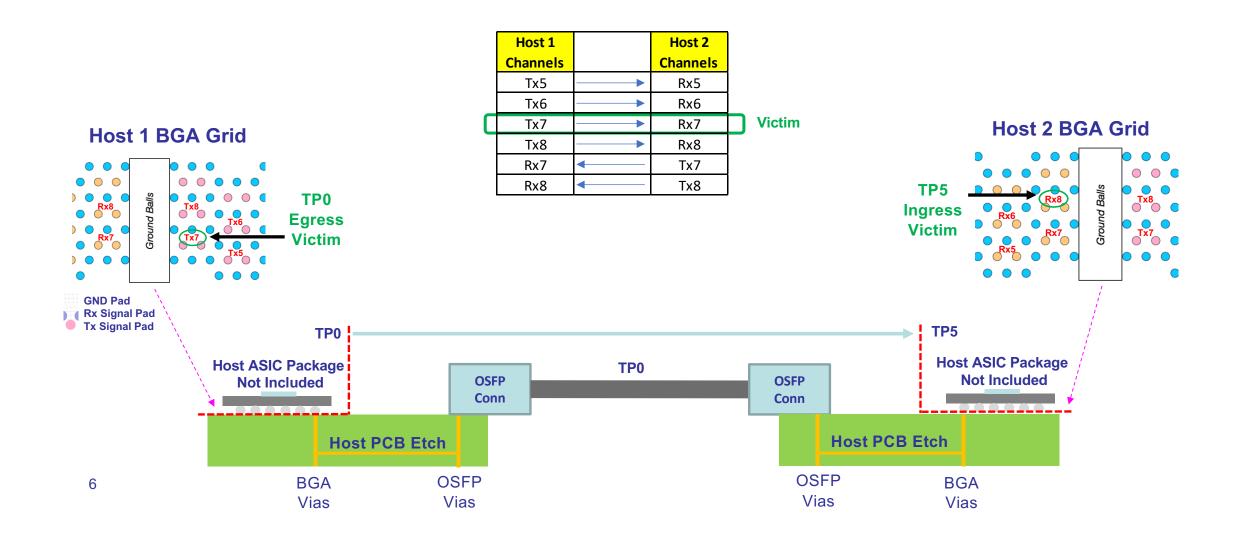

## **Signaling Topology**

## **Signaling Topology**

Host 1 BGA Grid  $\circ$  $\bigcirc$ TP0 Balls Rx8 **Egress** Ground  $\bigcirc$ Victim 0 Tx8a **GND** Pad 7 Rx Signal Pad Tx Signal Pad

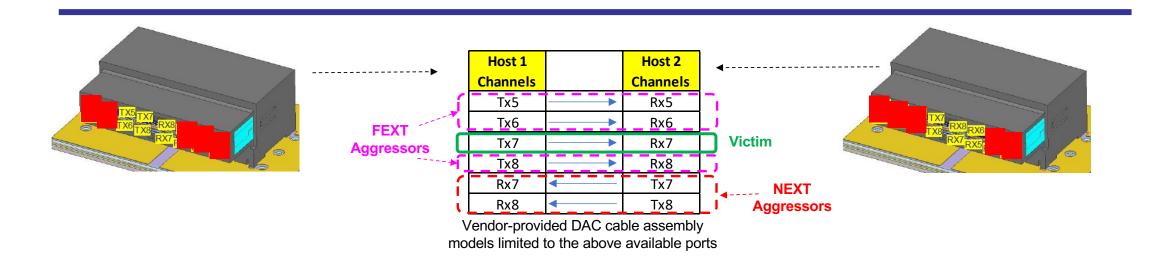

To include the "virtual" FEXT/NEXT from BGA signal balls Tx8a and Tx7a instantiate two copies of the following:

Tx8a: "...FEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p" Tx7a: "...NEXT\_TP0\_Tx7\_to\_TP5\_Rx7.s4p"

See slides 17-19 for full file names

# Host 2 BGA Grid

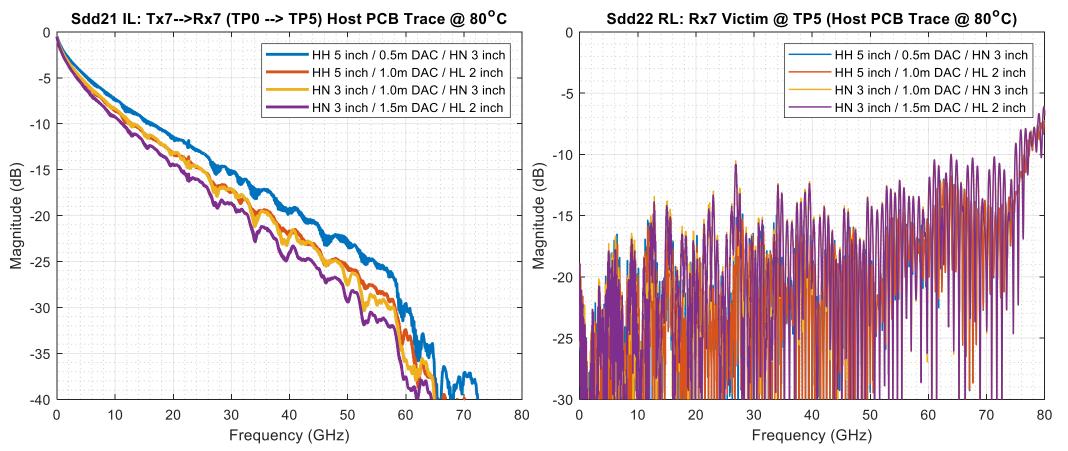

## CR Channel Model with Vendor "X" OSFP DAC Cable Insertion/Return Loss vs. Host PCB Lengths

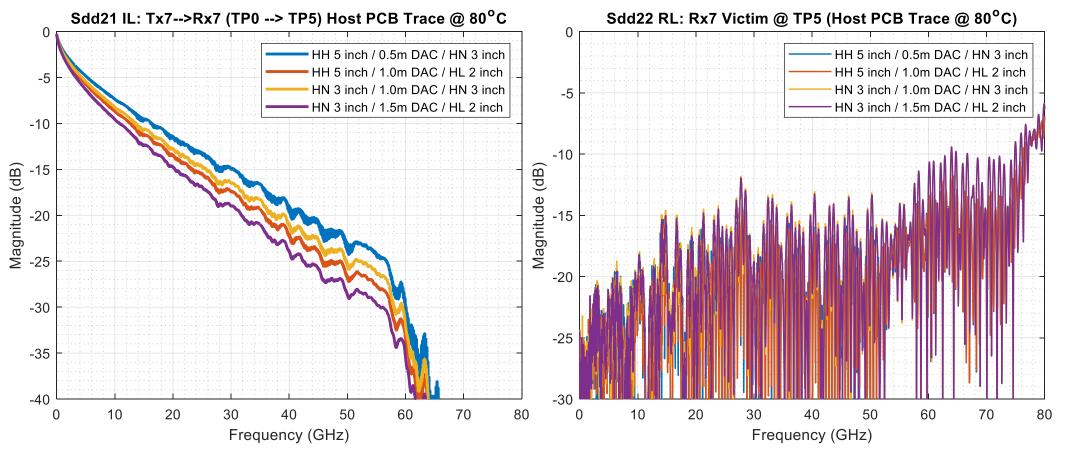

## CR Channel Model with Vendor "Y" OSFP DAC Cable Insertion/Return Loss vs. Host PCB Lengths

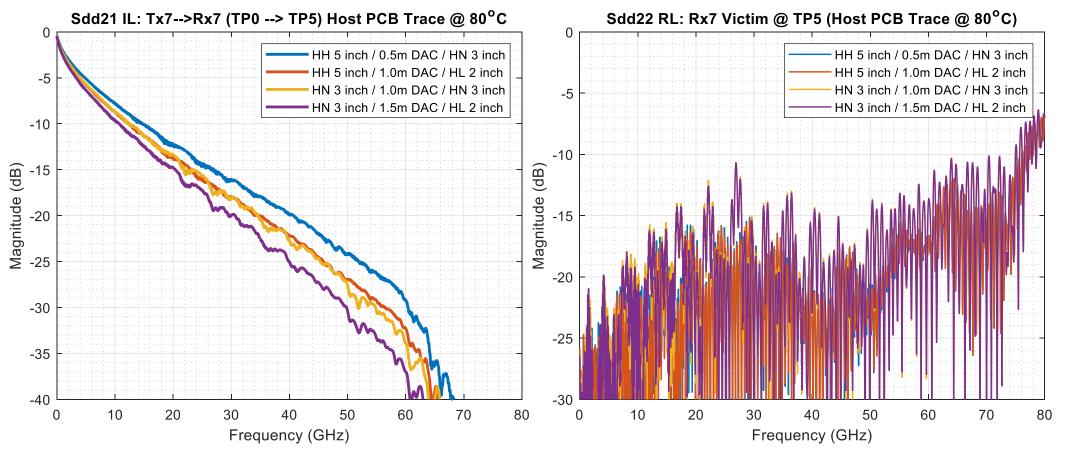

## CR Channel Model with Vendor "Z" OSFP DAC Cable Insertion/Return Loss vs. Host PCB Lengths

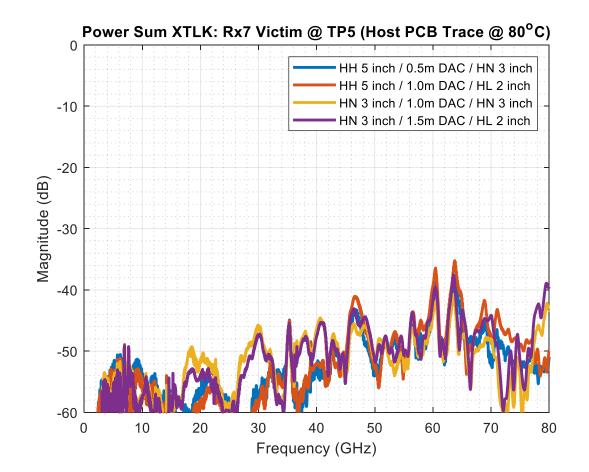

## CR Channel Model with Vendor "X" OSFP DAC Cable Power Sum XTLK vs. Host PCB Lengths

11

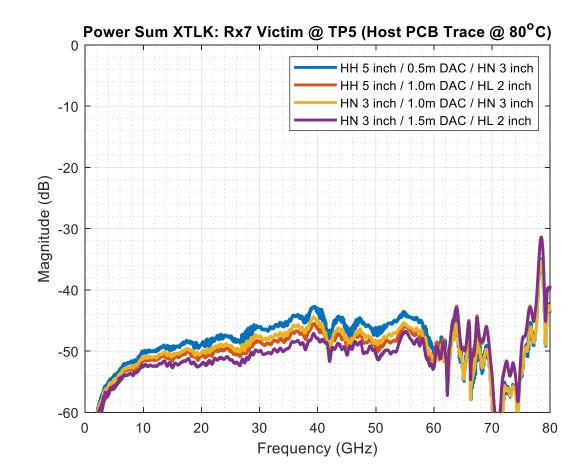

## CR Channel Model with Vendor "Y" OSFP DAC Cable Insertion/Return Loss vs. Host PCB Lengths

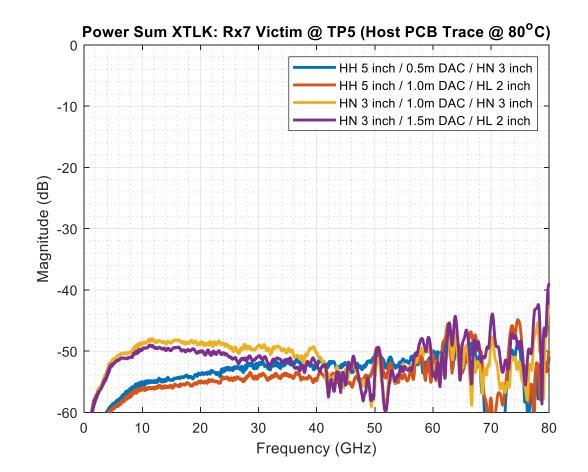

## CR Channel Model with Vendor "Z" OSFP DAC Cable Insertion/Return Loss vs. Host PCB Lengths

13

## **Summary**

#### Contributed CR channel models with OSFP DAC Cables

|               |             |               | TP0-TP5 Insertion Loss (dB) @53GHz |         |         |

|---------------|-------------|---------------|------------------------------------|---------|---------|

| Host #1       | Cable       | Host #2       | DAC 'X'                            | DAC 'Y' | DAC 'Z' |

| HH (5" trace) | CA-A (0.5m) | HN (3" trace) | -25.35                             | -23.36  | -25.45  |

| HH (5" trace) | CA-B (1.0m) | HL (2" trace) | -27.73                             | -26.58  | -28.33  |

| HN (3" trace) | CA-B (1.0m) | HN (3" trace) | -29.54                             | -25.14  | -29.23  |

| HN (3" trace) | CA-C (1.5m) | HL (2" trace) | -31.66                             | -28.49  | -32.16  |

- Each victim channel contains 6 signal lanes: 1 victim and 5 aggressors

- Return losses less than –10dB to ~60GHz

- Power summed XTLK is generally less than –40dB to ~60GHz

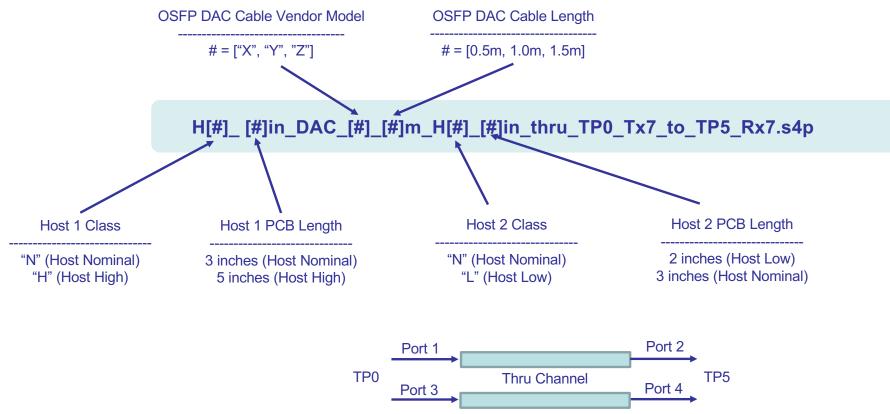

#### File Naming Convention: TP0→TP5 Thru Channels

**Thru Channel Files:** OSFP DAC Cable Vendor: ### = [X, Y, Z]

HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_thru\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_thru\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_thru\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_thru\_TP0\_Tx7\_to\_TP5\_Rx7.s4p

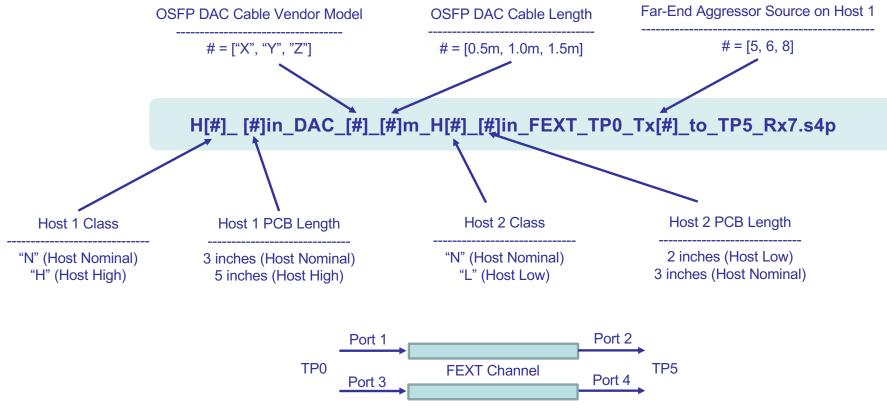

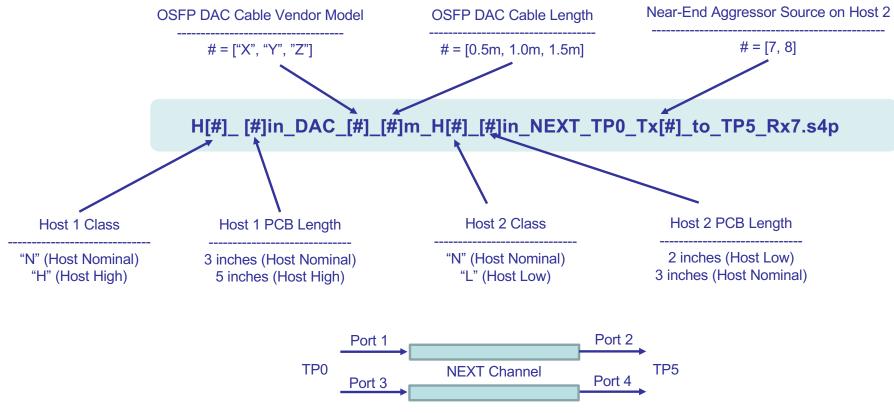

#### File Naming Convention: TP0→TP5 FEXT Channels

#### File Naming Convention: TP0→TP5 NEXT Channels

#### **XTLK Channel Files:** OSFP DAC Cable Vendor: ### = [X, Y, Z]

#### HH - 0.5m DAC - HN

HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_FEXT\_TP0\_Tx5\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_FEXT\_TP0\_Tx6\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_FEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_NEXT\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_0p5m\_HN\_3in\_NEXT\_TP0\_Tx8\_to\_TP5\_Tx7.s4p

#### <u>HH - 1.0m DAC - HL</u>

HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_FEXT\_TP0\_Tx5\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_FEXT\_TP0\_Tx6\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_FEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_NEXT\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HH\_5in\_DAC\_###\_1p0m\_HL\_2in\_NEXT\_TP0\_Tx8\_to\_TP5\_Tx7.s4p

#### HN - 1.0m DAC - HN

HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_FEXT\_TP0\_Tx5\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_FEXT\_TP0\_Tx6\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_FEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_NEXT\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p0m\_HN\_3in\_NEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p

#### HN - 1.5m DAC - HL

HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_FEXT\_TP0\_Tx5\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_FEXT\_TP0\_Tx6\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_FEXT\_TP0\_Tx8\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_NEXT\_TP0\_Tx7\_to\_TP5\_Rx7.s4p HN\_3in\_DAC\_###\_1p5m\_HL\_2in\_NEXT\_TP0\_Tx8\_to\_TP5\_Tx7.s4p