# 800GBASE-LR1 state diagrams

Leon Bruckman (Huawei)

## Supporters

- Kent Lusted (Intel)

- Eric Maniloff (Ciena)

- Yan Zhuangyan (Huawei)

- Xiang He (Huawei)

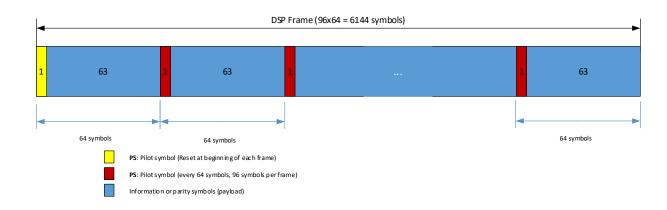

## The 800GBASE-LR1 DSP frame

- The 800GBASE-LR1 DSP frame is defined as a set of 96x64=6144 4–bit blocks

- 4-bit pilot symbols (PS) are inserted every 64 4-bit blocks (1 pilot 4-bit symbol, 63 message 4-bit blocks)

- Two 800GBASE-LR1 DSP frames are generated by the Inner FEC sublayer

- The 4-bit blocks for DSP frame\_0 are constructed from two consecutive bits from output\_0 (to be mapped to X<sub>1</sub>) and two consecutive bits from output\_1 (to be mapped to X<sub>Q</sub>)

- The 4-bit blocks for the DSP frame\_1 are constructed from two consecutive bits from output\_2 (to be mapped to Y<sub>I</sub>) and two consecutive bits from output\_3 (to be mapped to Y<sub>Q</sub>)

IEEE P802.3dj Task Force, January 2024

## Pilot Sequences (PSs)

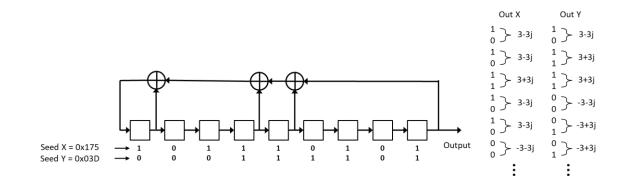

- The pilot sequence is a fixed PRBS9 sequence with different seed values for DSP frame\_0 and for DSP frame\_1

- The seeds are selected so that the pilot sequences are DC balanced.

- The generator is initialized using the seed at the start of every DSP frame, so that the same 96 PS symbols, [P0,...,P95] are inserted into every DSP frame PS field

- For each one of DSP frame\_0 and DSP frame\_1, the generator produces 192 bits PRBS[191:0] that are complemented by zeros to generate the 4-bit PS symbols.

- These 4–bit PS symbols are mapped to outer symbols of the 16QAM constellation, allowing robust framing to the 16QAM constellation

- The pilot sequence bits are used to synchronize to the each of the two DSP frames and to identify DSP frame\_0 and DSP frame\_1

- Note that the first symbol of both PSs is the same

IEEE P802.3dj Task Force, January 2024

ſΑ

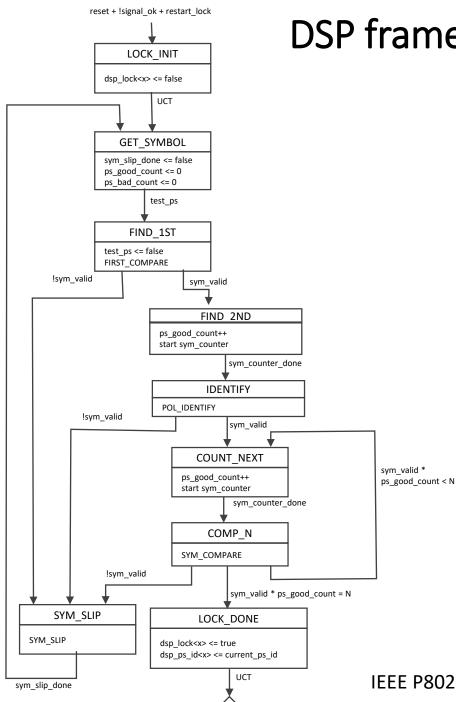

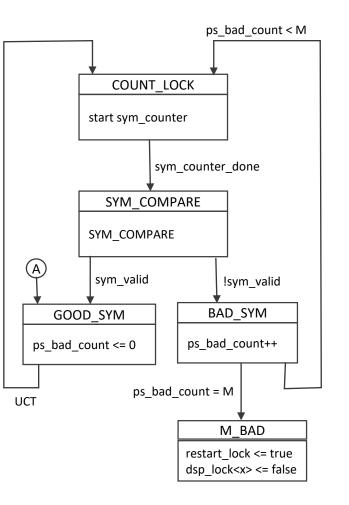

### DSP frame synchronization state diagrams

IEEE P802.3dj Task Force, January 2024

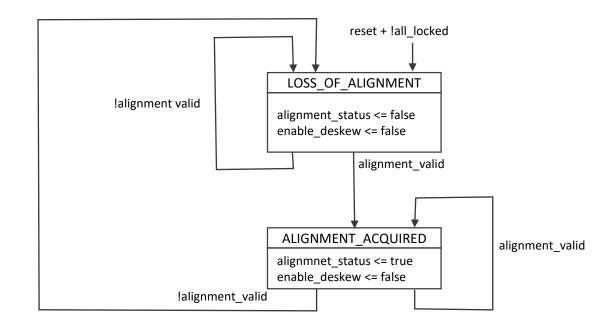

### Deskew state diagram

#### alignment\_valid

A Boolean variable that is set to true if the polarization symbol streams are aligned. Polarization symbol streams are considered to be aligned when dsp\_lock<x> is true for both x, each polarization symbol stream has a unique identifier, and the polarization symbol streams are deskewed. Otherwise, this variable is set to false.

#### all\_locked

A Boolean variable that is set to true when dsp\_lock<x> is true for both x and is set to false when dsp\_lock<x> is FALSE for either x.

## Summary

- State diagrams for 800GBASE-LR1 presented

- Propose to adopt the state diagrams as a baseline for 800GBASE-LR1 (802.3dj Clause 184)

- Exact values of N and M are TBD

- The plan is to bring a proposal next time