## Reference Die/Device Model and Parameters for 802.3dj COM Baseline

Mike Peng Li, Intel Richard Mellitz, Samtec Mike Dudek, Marvell Semiconductor Contributors Intel: Hsinho Wu, Masashi Shimanouchi, Ajay Balankutty, Jihwan Kim, Itamar Levin, Ariel Cohen Samtec: Adam Gregory, Brandon Gore

Jan, 2024

## Supporters

- Howard Heck, Intel

- Samuel Kocsis, Amphenol

- Tobey Li, MediaTek

- Upen Reddy Kareti, Cisco

- Bill Simms, Nvidia

- Srinivas Venkataraman, Meta

- Jim Weaver, Arista

# Background, Motivation, and Objective

- COM is the specification method for channel compliances for 802.3 and other related standards (e.g., OIF/CEI, FC, JESD204, etc.).

- Reference die/device model and parameters are critical elements of COM.

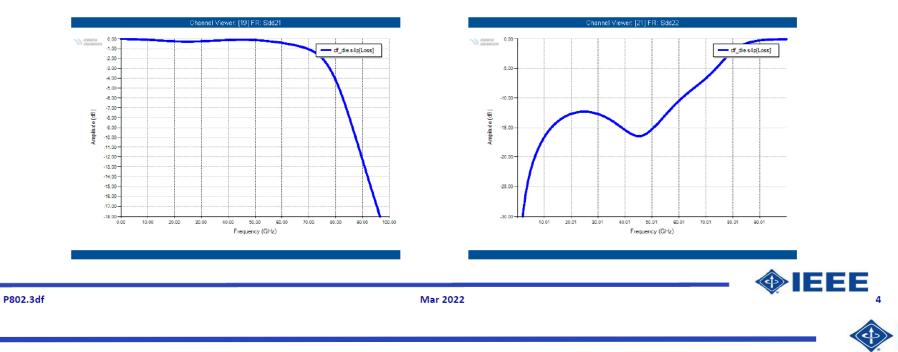

- 200G/L reference die/device model and parameters had been extracted from the Intel test chips [1], [2], and presented at 802.3df [3] in Mar, 2022.

- COM die/device model had been extended to scalable LC ladder, with three stage LC ladder, and related LC parameters from [3] for 200G/L since COM3.7 [4].

- All the channel and system analysis of 200G/L using COM3.7, 3.9, and 4.0+ are based on the die/device model and parameters defined in [3], [4].

- 200G/L reference die/device model and been accepted in July, 2023 meeting

- It is time to formally consider adopting the parameters defined in [3], [4], [5] after > 1.5 yr validation, evaluation, and analysis, to enable 802.3dj, and related OIF/CEI, FC, JESD204 specification developments.

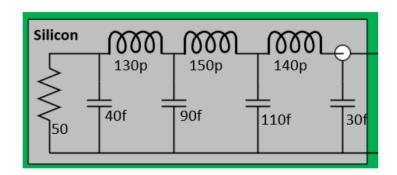

## Recap of 200G/L Die/Device Model and Parameters Extracted from Test Chips[1],[2],[3],[6] A Proposed Reference Die Model for 802.3df

EΕ

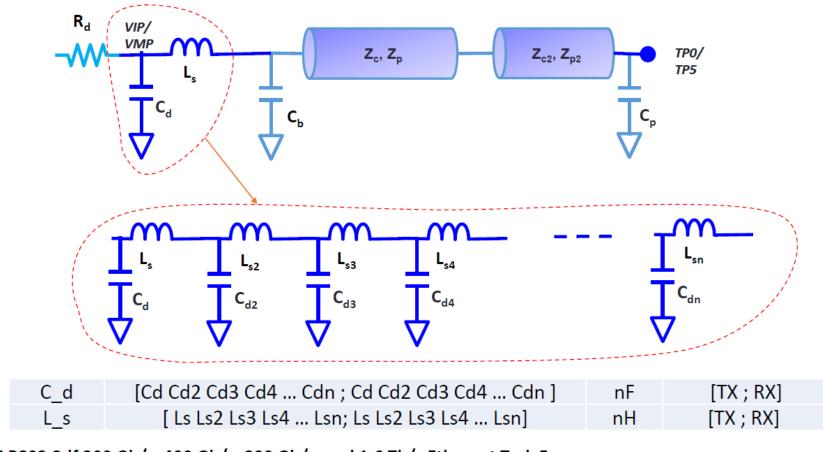

#### Recap of 200G/L Die/Device Model for Annex 93A/COM [4]

#### Replace Cd and Ls with a Ladder

IEEE P802.3df 200 Gb/s, 400 Gb/s, 800 Gb/s, and 1.6 Tb/s Ethernet Task Force

5

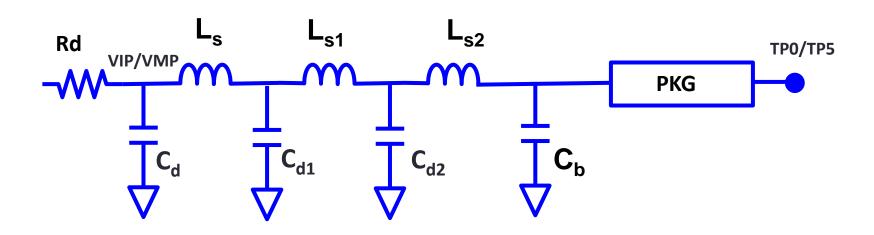

## Recap of Adopted 200G/L Reference Die/Device Model for Annex 93A/COM [5]

| C_d | [Cd Cd1 Cd2; Cd Cd1 Cd2 ] | nF | [TX ; RX] |

|-----|---------------------------|----|-----------|

| L_s | [ Ls Ls1 Ls2; Ls Ls1 Ls2] | nH | [TX ; RX] |

| C_b | [Cb;Cb]                   | nF | [TX ; RX] |

#### Recap of Adopted Updated Figure 93A-2 for Annex 93A/COM [5]

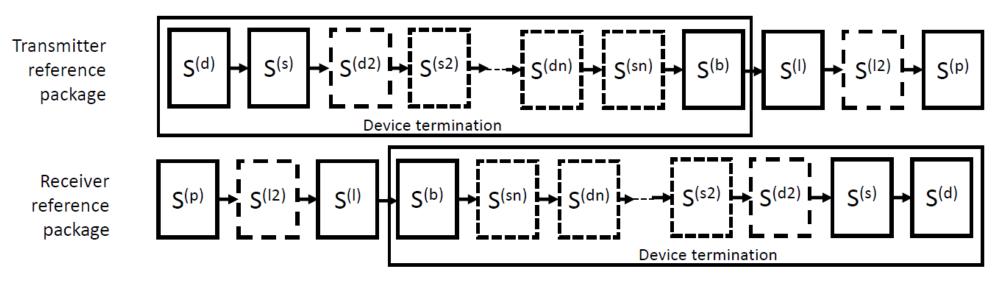

S<sup>(d)</sup> = device capacitance S-parameter

- S<sup>(s)</sup> = device series inductance S-parameter

- $S^{(d2)}$  = device capacitance 2 S-parameter

- S<sup>(s2)</sup> = device series inductance 2 S-parameter

- $S^{(dn)} = n^{th}$  device capacitance S-parameter

S<sup>(sn)</sup> = n<sup>th</sup> device series inductance S-parameter

S<sup>(b)</sup> = bump capacitance S-parameter

S<sup>(I)</sup> = package transmission line S-parameter

S<sup>(12)</sup> = package transmission line 2 S-parameter

S<sup>(p)</sup> = package capacitance S-parameter

Note: PMD calls out which blocks are included in the package model

Updated Figure 93A-2-Reference package Models

#### Proposed 200G/L Reference Die/Device Model Parameters for COM [5]

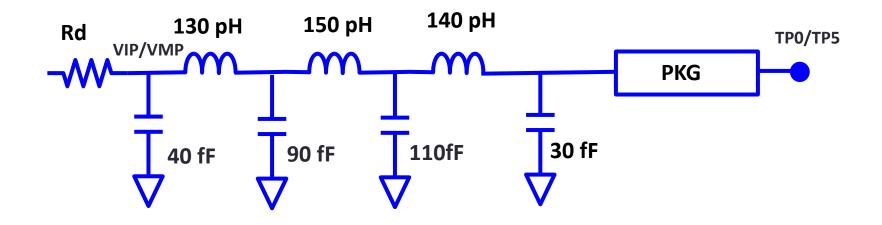

| C_d | [0.4e-4 0.9e-4 1.1e-4; 0.4e-4 0.9e-4 1.1e-4] | nF | [TX RX] |

|-----|----------------------------------------------|----|---------|

| L_s | [ .13 .15 .14; .13 .15 .14 ]                 | nH | [TX RX] |

| C_b | [.3e-4 .3e-4]                                | nF | [TX RX] |

### References

[1] J. Kim et al, "A 224Gb/s DAC-Based PAM-4 Transmitter with 8-Tap FFE in 10nm CMOS", ISSCC, 2021.

[2] A. Khairi "A 1.4 pJ/b 224 Gb/s- PAM4 SERDES Receiver with 31 dB Loss Compensation ", ISSCC, 2022.

- [3] M. Li et al, "Reference Die and Package Models for 802.3df Host", https://www.ieee802.org/3/df/public/22\_03/mli\_3df\_02a\_220316.pdf, 802.3df, 2022.

- [4] R. Mellitz et al, "Annex 93A Package/Die Load Proposal and COM 3.70 with Exploratory Features including Package/Die Load Ladder", <u>https://www.ieee802.org/3/df/public/22\_03/mellitz\_3df\_01b\_220316.pdf</u>, 802.3df, 2022.

[5] M. Li, R. Mellitz et al, "Reference Die/Device Model and Parameters for 802.3dj COM Baseline", <u>https://www.ieee802.org/3/dj/public/23\_07/lim\_3dj\_01\_2307.pdf</u>, 802.3dj, 2023.

[6] M. Cusmai et al., "A 224Gb/s sub-pJ/b PAM-4 and PAM-6 DAC-Based Transmitter in 3nm FinFET", ISSCC, 2024.

# **Thank You!**