# TERAHOP

Shortened test time for Block-Error RX Sensitivity (Comment #593)

IEEE 802.3dj July 2025

Michael He, Penny Xu, Xiangwei Zhang, Rang-chen (Ryan) Yu

TeraHop Pte. Ltd.

## Supporter

- Roberto Rodes, Coherent

- Karlheinz Muth, Broadcom

- Hai-feng Liu, HG-Genuine

- Peter Stassar, Huawei

- Guangcan Mi, Huawei

- Chris Cole, Coherent

- Ali Ghiasi, Ghiasi Quantum

- Gary Landry, TI

- Fabio Bottoni, Cisco

- Mike Dudek, Marvell

- Piers Dawe, Nvidia

- Frank Chang, Source photonics

- Matt Brown, Alphawave Semi

#### Contents

- Overview

- Block error FEC tail curves with different test time

- Proposal with shortened test time

- FEC tail curves with fiber dispersion

- Summary and Suggested Remedy

#### Overview

#### 180.2 Error ratio allocation

A complete PHY is expected to meet the frame loss ratio specifications in 174A.5.

With a compliant input signal, a PMD receiver is expected to meet the block error ratio of  $1.45 \times 10^{-11}$  (see 174A.5), measured at the PMA adjacent to the PMD using the method described in 174A.8, with BER<sub>added</sub> equal to  $6.4 \times 10^{-5}$

With a compliant input signal, a PHY receiver is expected to meet the block error ratio of  $1.45 \times 10^{-11}$  (see 174A.5), measured at the PCS using the method described in 174A.10, with  $BER_{added}$  equal to  $3.2 \times 10^{-5}$ .

Table 174A-1—Error ratio allocations for optical PHYs with no FEC sublayer or with an Inner FEC sublayer

| ISL                     | Frame loss ratio<br>for entire<br>PCS-to-PCS link | Codeword error<br>ratio for entire<br>PCS-to-PCS link | BER for entire<br>PCS-to-PCS link<br>(BER <sub>total</sub> ) | BER per ISL <sup>a</sup> |

|-------------------------|---------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|--------------------------|

| xAUI-n C2C <sup>b</sup> |                                                   |                                                       | 2.92 × 10 <sup>-4</sup>                                      | $0.08 \times 10^{-4}$    |

| xAUI-n C2M              |                                                   |                                                       |                                                              | 0.24 × 10 <sup>-4</sup>  |

| PMD-to-PMD              | 6 × 10 <sup>-11</sup>                             | $1.45 \times 10^{-11}$                                |                                                              | $2.28 \times 10^{-4}$    |

| xAUI-n C2M              |                                                   |                                                       |                                                              | 0.24 × 10 <sup>-4</sup>  |

| xAUI-n C2C <sup>b</sup> |                                                   |                                                       |                                                              | 0.08 × 10 <sup>-4</sup>  |

<sup>&</sup>lt;sup>a</sup> Measured at the PMA closest to the PMD or AUI component and after Inner FEC decoding, if present, except measured at the Inner FEC for 800GBASE-LR1.

#### 174A.8.1.3 PMA error histogram measurement

Using the count accumulated during a test, a set of test block error histograms is calculated.

$H_{\rm m}^{(i)}(k)$  is a set of p measured 17-bin histograms, one histogram for each lane i, defined as follows:

- $H_{\rm m}^{(i)}(k)$  where k < 16 is the is the probability of k test symbol errors in a test block for lane i.

- $H_{\rm m}^{(i)}(16)$  is the probability of more than 15 test symbol errors in a test block for lane i.

Histograms  $H_{\rm m}^{(i)}(k)$  are measured according the following method for each lane i:

- At the transmitting device generate a PRBS31 or PRBS31Q test pattern in the PMA.

- In the receiving PMA, identify errored bits from the physical link using the PRBS31 or PRBS31Q block error checker.

- Divide the stream into a series of test symbols and test blocks as defined in 174A.8.1.2.

- For each test block, count the number of test symbols with one or more bit errors and, based on the total number of test symbol errors in the test block, increment the appropriate bin counter.

- The total number of test blocks analyzed is determined according to Equation (174A-1). The value of test block total count i should be sufficiently large to reliably verify that the expected block error ratio is met, either by direct measurement or statistical projection. The projection should provide an accurate prediction of the value of  $H_m^{(i)}(k)$  that would be observed over longer-term testing or at least provide an upper bound on the value.

- Calculate the histogram bins  $H_{\rm m}^{(i)}(k)$  according to Equation (174A–2).

test\_block\_total\_count\_i = test\_block\_error\_bin\_i\_16p +

$$\sum_{k=0}^{15}$$

test\_block\_error\_count\_i\_k (174A-1)

$$H_m^{(i)}(k) = \frac{\text{test\_block\_error\_count\_}_{i\_k}}{\text{test block total count } i}$$

(174A-2)

<sup>&</sup>lt;sup>b</sup> If the PMD is a type defined in Clause 180, Clause 181, Clause 182, Clause 183, or Clause 185, and xAUI-n C2C is a type defined in Annex 120D (i.e., 50 Gb/s per lane) or Annex 120F (i.e., 100 Gb/s per lane), the xAUI-n C2C is expected to meet the BER allocations in this table.

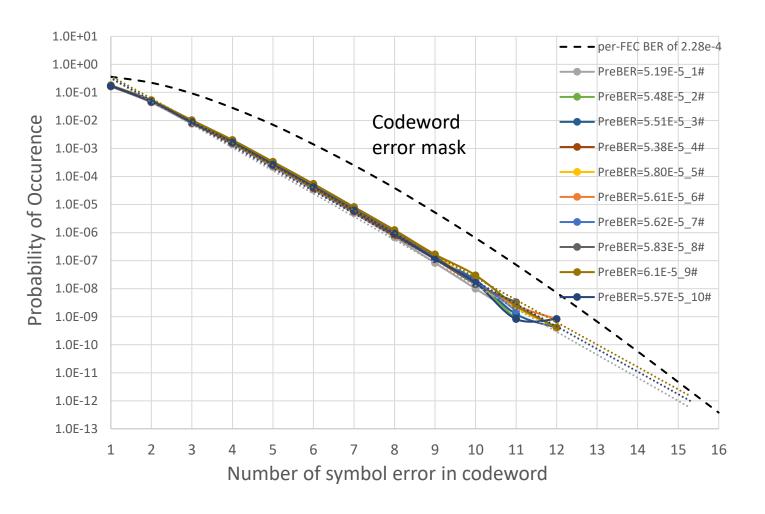

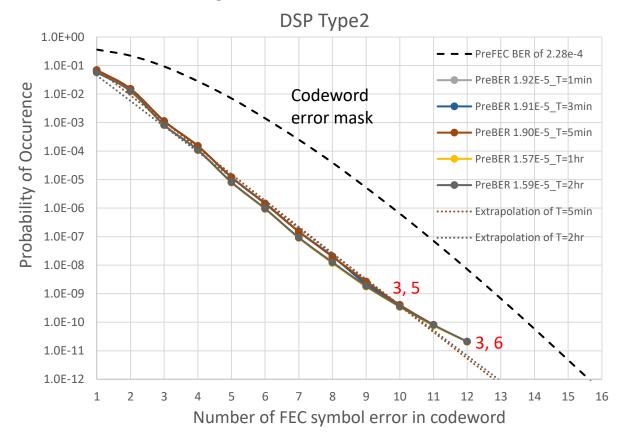

### FEC error histogram tests at 1 minute scale

- Test of FEC tail curves over 10 x 1min show good repeatability except the final bin 11, 12

- The error histogram is not sufficient large to plot a complement curve out to bin 16

| Errored Symbol<br>10 | Errored Symbol<br>11 | Errored Symbol<br>12 |

|----------------------|----------------------|----------------------|

| 24                   | 3                    | 0                    |

| 39                   | 2                    | 0                    |

| 50                   | 3                    | 1                    |

| 35                   | 6                    | 1                    |

| 37                   | 5                    | 1                    |

| 37                   | 6                    | 2                    |

| 44                   | 4                    | 0                    |

| 35                   | 8                    | 0                    |

| 73                   | 6                    | 1                    |

| 39                   | 2                    | 2                    |

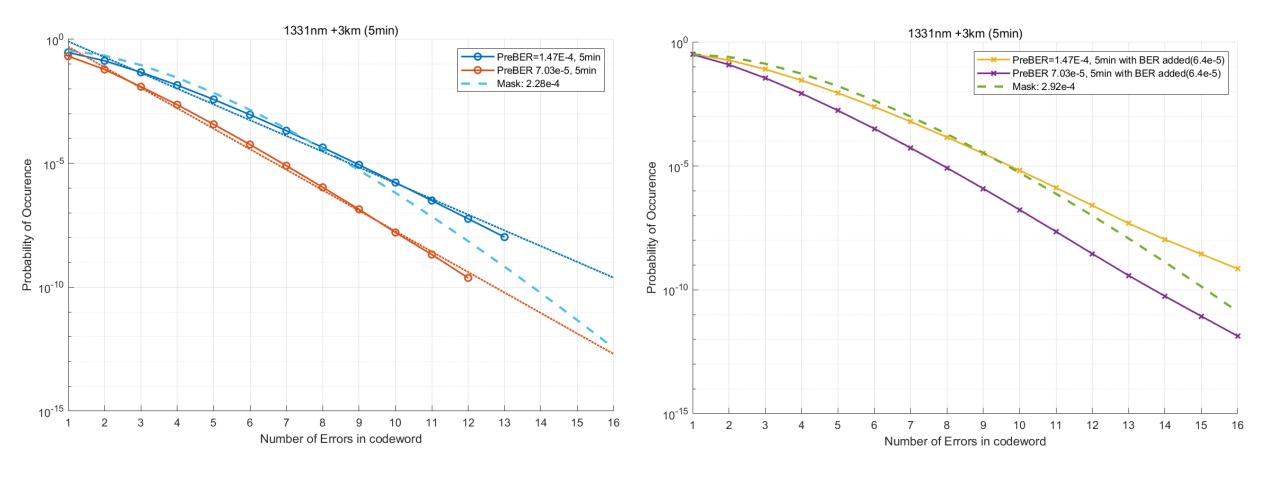

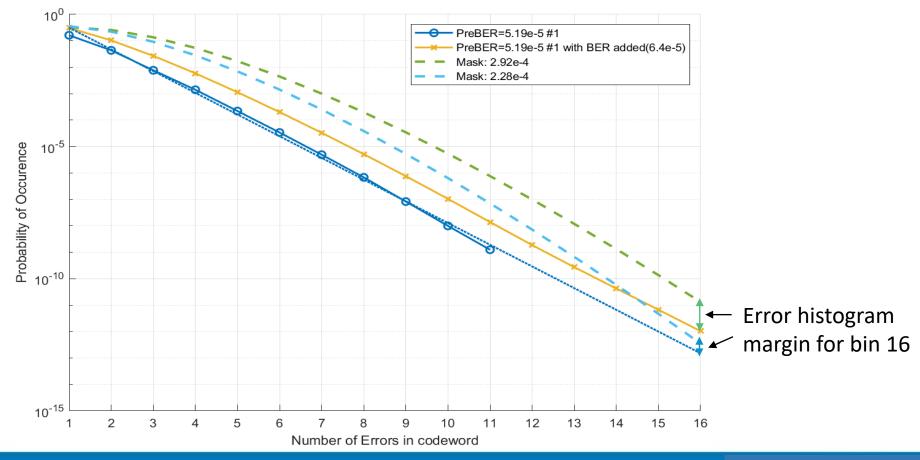

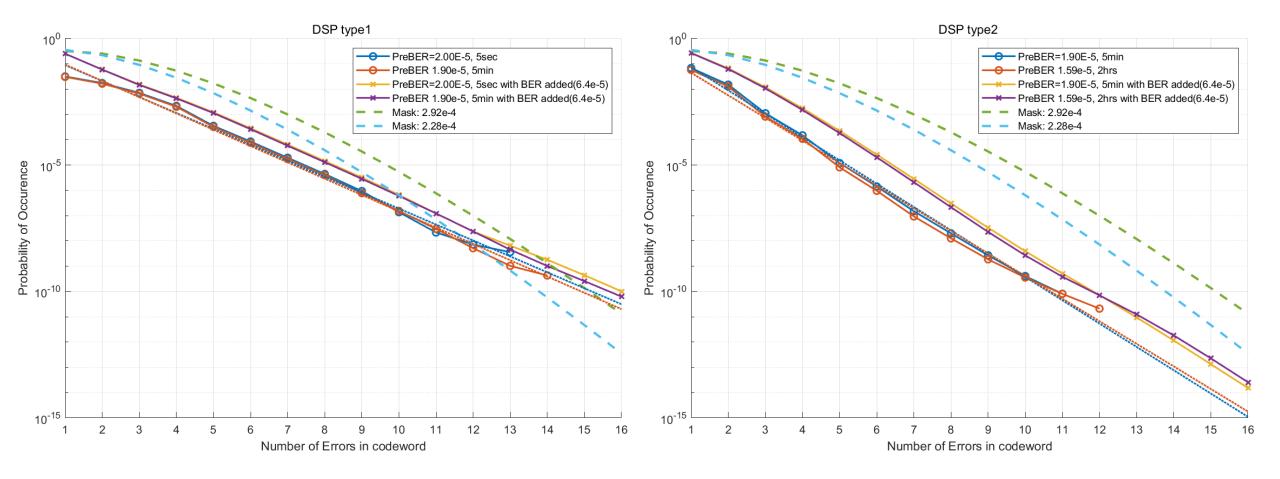

#### Compare with error histogram with BERadded

- Convolve the extrapolated histogram with the AUI error histograms (6.4e-5).

- Compare this convolved histogram to the block error histogram for 2.92e-4 random error ratio or the block error ratio derived from bin 16

- The convolved histogram curve looks a little more curvature, and the error histogram margin for bin 16 is a bit increased.

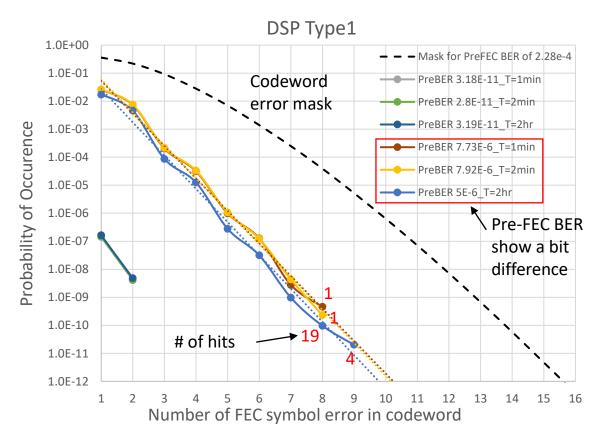

#### Comparison for test time of minutes vs hours

- At same/similar high Pre-FEC BER levels (lower input power), FEC tail grows longer at lower probability with longer test time

- At Low Pre-FEC/high input power level, FEC tail changes very little

- FEC-tail slope follows extrapolation curve well over short and long test time

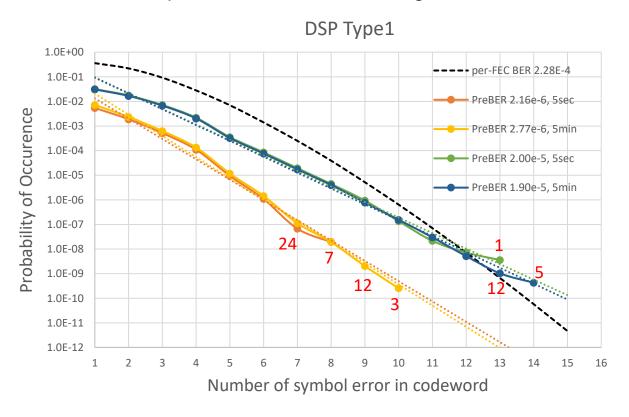

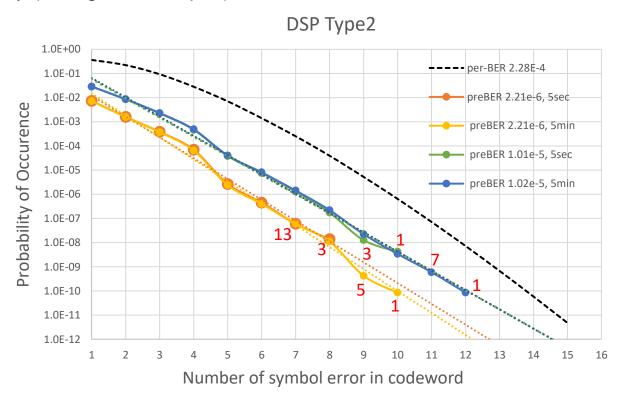

### Recommendation for shortening the test time

- FEC tail curve for test time of 5 sec. and 5 min. overlaps well

- The exponential fitting lines for FEC tail also overlaps well for 5 sec. and 5 min. test time

- 2 representative DSPs are tested for comparison, and conclusions are similar

- Recommendation:

- At pre-set input power to receiver, collect FEC error histogram data with order of seconds

- Extrapolate the measured histogram out to bin 16 linearly (on logY-linearX plot)

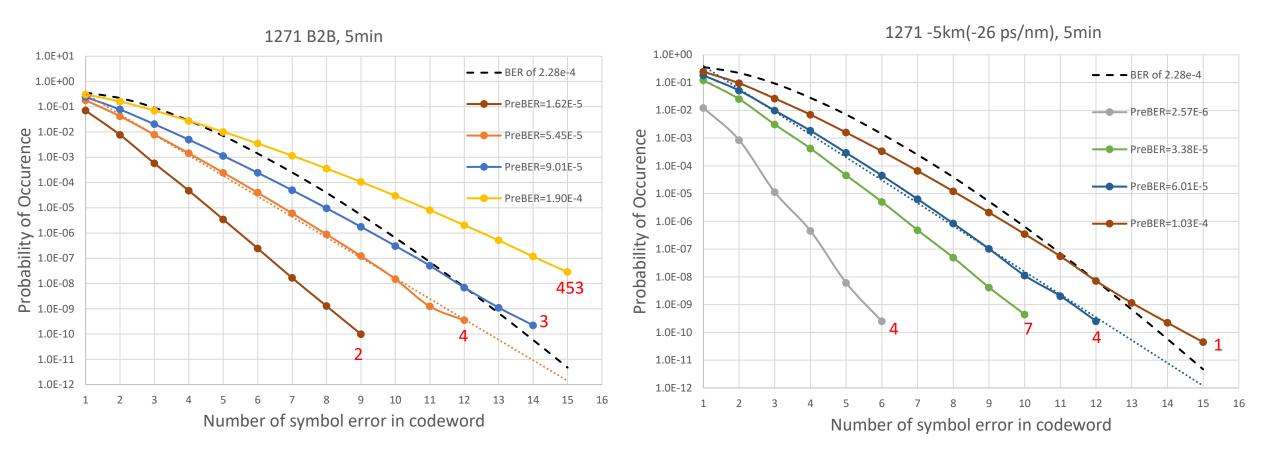

#### FEC tail curves with fiber transmission

Table 183-9—Optical channel characteristics

| Description                                  | 800GBASE-FR4 | 800GBASE-LR4 | Unit  |

|----------------------------------------------|--------------|--------------|-------|

| Operating distance (max)                     | 2            | 10           | km    |

| Channel insertion loss <sup>a, b</sup> (max) | 4            | 6.3          | dB    |

| Channel insertion loss (min)                 | 0            |              | dB    |

| Positive dispersion <sup>b</sup> (max)       | 6.02         | 2.8          | ps/nm |

| Negative dispersion <sup>b</sup> (min)       | -11.26       | -24.6        | ps/nm |

| DGD_max <sup>c</sup>                         | 2.3          | 4            | ps    |

| Optical return loss (min)                    | 25           | 22           | dB    |

|                         | @1331nm    | @1271nm   |

|-------------------------|------------|-----------|

| Positive DC fiber (3km) | +8.2 ps/nm | -         |

| Negative CD fiber (5km) | -          | -26 ps/nm |

These channel insertion loss values include cable, connectors, and splices.

Over the wavelength range 1264.5 nm to 1337.5 nm for 800GBASE-FR4, and 1294.53 nm to 1310.19 nm for 800GBASE-LR4. The dispersion specifications are based on the statistical link design methodology documented in ITU-T REC G.652, Appendix I.

<sup>&</sup>lt;sup>c</sup> Differential Group Delay (DGD) is the time difference at reception between the fractions of a pulse that were transmitted in the two principal states of polarization of an optical signal. DGD max is the maximum differential group delay that the system is required to tolerate.

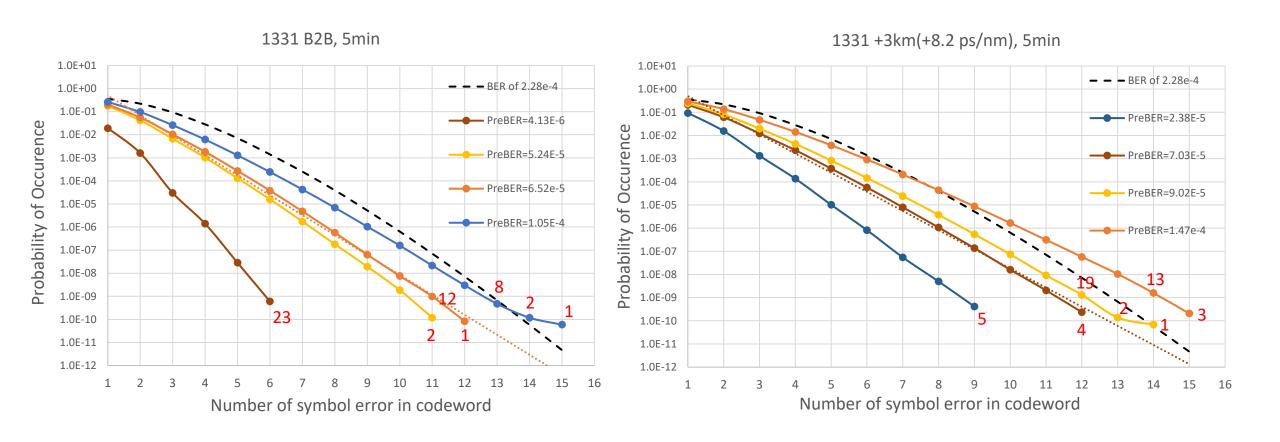

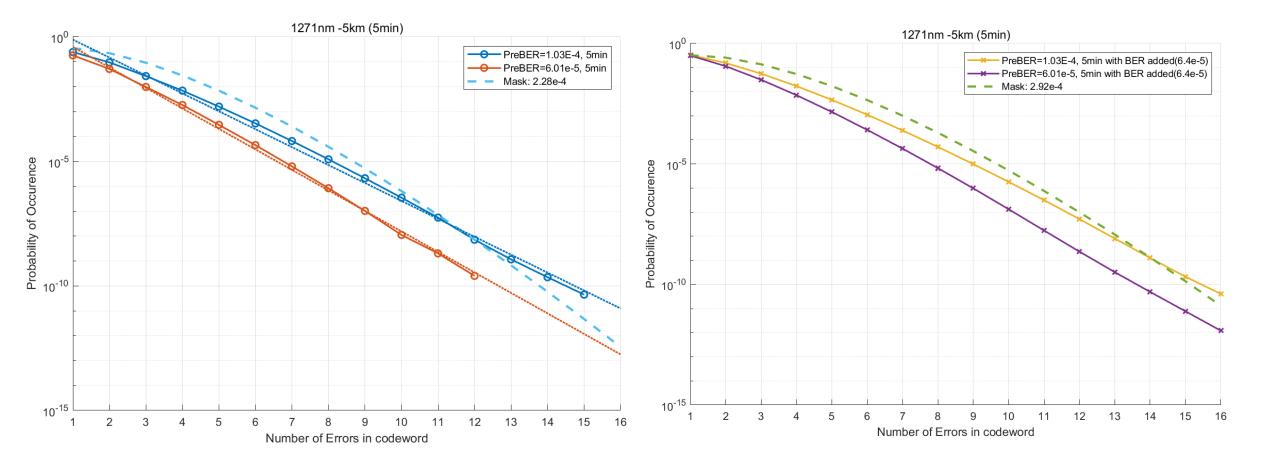

#### FEC tail curves with fiber transmission

No distortion or bending occur for the BLER curves with (negative dispersion) fiber transmission

#### FEC tail curves with fiber transmission

No distortion or bending occur for the BLER curves with (positive dispersion) fiber transmission

## Summary

- Test data show consistent FEC tail results with different test time with a given pre-FEC BER (or receiver input power)

- Over 5 seconds, 5 minutes, to 2 hours

- Over repeated tests

- Over 2 different DSPs

- BTB and over fiber dispersion max/min.

- Short test time (5 seconds) data with linear extrapolation (on logY-linearX plot) for FEC tail showing a good representation to determine receiver sensitivity or do the pass/fail criteria

## Suggested Remedy

**Option1:** Add an informative note in sub-clause 180.9.12 (also in the same place in 181.9.12, 182.9.12, 183.9.12). Can also be referred by other PMD/AUI if it is applicable).

#### 180.9.12 Receiver sensitivity

The receiver sensitivity  $(OMA_{outer})$  of each lane shall be within the limits given in Table 180–8 if measured using a test pattern for receiver sensitivity in Table 180–14. The conformance test signal at TP3 meets the requirements for a transmitter followed by an attenuator.

The TECQ of the conformance test signal is measured according to 180.9.5, except that the test fiber is not used. The measured value of TECQ is then used to calculate the limit for receiver sensitivity (OMA<sub>outer</sub>) as specified in Table 180-8.

#### Recommend text to be added:

"The receiver sensitivity can be assessed by measuring block error ratio specified in 180.2. Informatively, the block error histogram can be either measured directly or just measured partly for a short time (e.g. order of seconds) combined with extrapolation (on logY-linearX plot) to bin 16". The receiver sensitivity approximated by the extrapolated line for minimum input power achievable should not violate the error histogram mask for 2.92e-4 random BER, with BERadded equal to 6.4e-5."

**Option2:** Add an informative note in 174A.8.1.3 relating to the "statistical projection", or add an entire new informative annex 174B

#### 174A.8.1.3 PMA error histogram measurement

Using the count accumulated during a test, a set of test block error histograms is calculated.

$H_{\rm m}^{(i)}(k)$  is a set of p measured 17-bin histograms, one histogram for each lane i, defined as follows:

- $H_{\rm m}^{(i)}(k)$  where k < 16 is the is the probability of k test symbol errors in a test block for lane i.

- $H_{\rm m}^{(i)}(16)$  is the probability of more than 15 test symbol errors in a test block for lane i.

Histograms  $H_{\rm m}^{(i)}(k)$  are measured according the following method for each lane *i*:

- a) At the transmitting device generate a PRBS31 or PRBS31Q test pattern in the PMA.

- b) In the receiving PMA, identify errored bits from the physical link using the PRBS31 or PRBS31Q block error checker.

- c) Divide the stream into a series of test symbols and test blocks as defined in 174A.8.1.2.

- d) For each test block, count the number of test symbols with one or more bit errors and, based on the total number of test symbol errors in the test block, increment the appropriate bin counter.

- The total number of test blocks analyzed is determined according to Equation (174A-1). The value of test\_block\_total\_count\_i should be sufficiently large to reliably verify that the expected block error ratio is met, either by direct measurement or statistical projection. The projection should provide an accurate prediction of the value of  $H_m^{(i)}(k)$  that would be observed over longer-term testing or at least provide an upper bound on the value.

- f) Calculate the histogram bins  $H_{\rm m}^{(i)}(k)$  according to Equation (174A–2).

test\_block\_total\_count\_i = test\_block\_error\_bin\_i\_16p +

$$\sum_{k=0}^{15}$$

test\_block\_error\_count\_i\_k (174A-1)

$$H_m^{(i)}(k) = \frac{\text{test\_block\_error\_count\_}_{i\_k}}{\text{test\_block\_total\_count\_}_{i}}$$

(174A-2)

#### TERAHOP

# THANK YOU

## Compare with additional error histogram with BERadded (1)

# Compare with additional error histogram with BERadded (2)

# Compare with additional error histogram with BERadded (3)