# Considerations for C2M Link Budget

Leesa Noujeim and Hong Liu

IEEE 802.3dj Electrical Ad Hoc, Aug 22 2024 (r1)

- Review and update our Feb. 2022 contribution (26dB ILdd-die2die)

- Show an example implementation

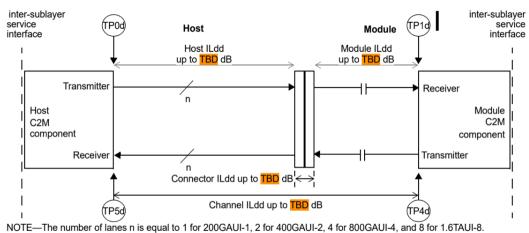

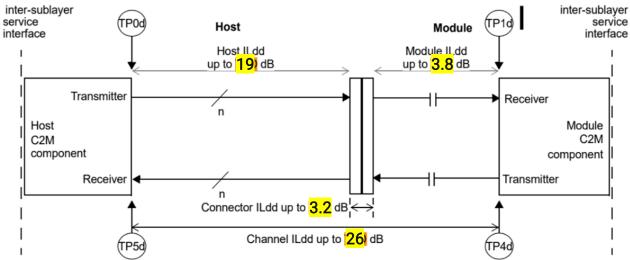

- Propose values for TBDs in D1.1 Fig 176E-2 (informative insertion loss budget)

Figure 176E-2—Components of a 200 Gb/s per lane AUI-C2M and insertion loss budget at 53.125 GHz

# Background

From July 2024 802.3 Plenary: <a href="https://www.ieee802.org/3/dj/public/24\_07/lusted\_3dj\_04\_2407.pdf">https://www.ieee802.org/3/dj/public/24\_07/lusted\_3dj\_04\_2407.pdf</a>

"Consensus seems to be forming around ILdd (die-die) = 33dB, based on offline discussions"

| Contribution                     | Ildd Recommendation                         |

|----------------------------------|---------------------------------------------|

| lusted_3dj_01a_2406<br>(slide 6) | ~33dB for PCB host<br>~29dB for cabled host |

| ghiasi_3dj_01_2407               | 30dB<br>32dB with extra care                |

This large ILdd will require a more capable reference receiver (eg MLSE, stronger ctle) than the more modest ILdd proposed in this contribution.

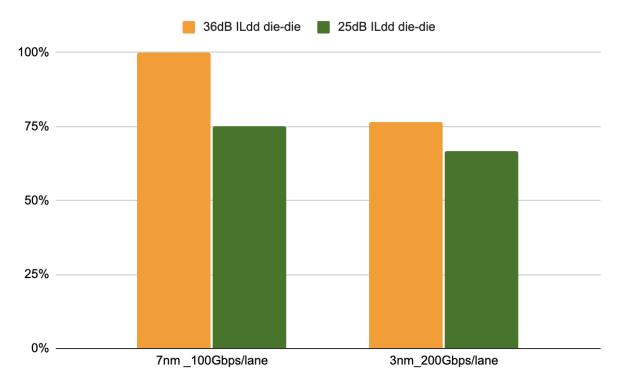

#### Motivation: SerDes Power Efficiency

Opportunity to improve SerDes power efficiency by ~15% for 200Gbps/lane AUIs => Lower system power, optical module power

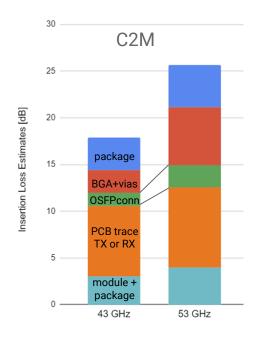

## Feb 2022 C2M link budget

53GHz budget ~26dB:

Package ~5dB

BGA+vias ~6dB

OSFP conn ~2.5dB

PCB trace ~8.5dB

Module+pkg ~4dB

Source: https://www.ieee802.org/3/df/public/22\_02/noujeim\_3df\_01\_220224.pdf

Update Aug 2024: redistribute package and BGA/via allocations; overall budget remains unchanged.

#### July 2024 Example Implementation

- High radix (100T) switch, 64 OSFP ports

- Longest package (~10dB at 53.125GHz) mates with shorter PCB

- Longest PCB (~8") mates with shorter package

- PCB loss 1.3dB/inch: includes generous margin for manufacturing and temperature effects

|             | Package<br>ILdd [dB] | BGA-via rolloff [dB] | PCB<br>Length ["] | PCB ILdd<br>[dB] | connector<br>+ vias [dB] | Module<br>ILdd [dB] | Die to Die<br>ILdd [dB] |

|-------------|----------------------|----------------------|-------------------|------------------|--------------------------|---------------------|-------------------------|

| Max Package | 10.0                 | 1.0                  | 6.0               | 7.8              | 2.75                     | 2.0                 | 23.55                   |

| Max PCB     | 5.0                  | 1.0                  | 8.0               | 10.4             | 2.75                     | 2.0                 | 21.15                   |

| Mid Pkg/PCB | 7.0                  | 1.0                  | 7.0               | 9.1              | 2.75                     | 2.0                 | 21.85                   |

## Reconcile Example Budget with Adopted MTF

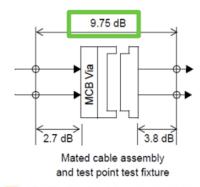

#### D1.1 Mated Test Fixture includes:

- 3.8 dB allocation for Host Compliance Board

- 3.25 dB for connector+MCB vias

This is *not* an endorsement of this MTF IL allocation (connector + MCB\_via seems too high)

NOTE (TBD)—2.7 dB MCB PCB ILdd includes the RF connector (up to the RF connector reference plane). The MCB via allowance is 0.8 dB.

Figure 179A–3—Host-Nominal to Host-Nominal, Cable assembly, and test fixture insertion loss at 53.125 GHz

#### Modifications for Adopted Mated Test Fixture

Adjust budget to reconcile with Mated Test Fixture D1.1 allocations:

|             | Package<br>ILdd [dB] | BGA-via<br>rolloff [dB] | PCB<br>Length ["] | PCB ILdd<br>[dB] | connector<br>+ vias [dB] | Module<br>ILdd [dB] | Die to Die<br>ILdd [dB] |

|-------------|----------------------|-------------------------|-------------------|------------------|--------------------------|---------------------|-------------------------|

| Max Package | 10.0                 | 1.0                     | 6.0               | 7.8              | 2.75                     | 2.0                 | 23.55                   |

| Max PCB     | 5.0                  | 1.0                     | 8.0               | 10.4             | 2.75                     | 2.0                 | 21.15                   |

| Mid Pkg/PCB | 7.0                  | 1.0                     | 7.0               | 9.1              | 2.75                     | 2.0                 | 21.85                   |

|             |                      |                         |                   |                  |                          | ·   |                         |

|-------------|----------------------|-------------------------|-------------------|------------------|--------------------------|-----|-------------------------|

|             | Package<br>ILdd [dB] | BGA-via<br>rolloff [dB] | PCB<br>Length ["] | PCB ILdd<br>[dB] | Connector<br>+ vias [dB] |     | Die to Die<br>ILdd [dB] |

| Max Package | 10.0                 | 1.0                     | 6.0               | 7.8              | 3.25                     | 3.8 | 25.85                   |

| Max PCB     | 5.0                  | 1.0                     | 8.0               | 10.4             | 3.25                     | 3.8 | 23.45                   |

| Mid Pkg/PCB | 7.0                  | 1.0                     | 7.0               | 9.1              | 3.25                     | 3.8 | 24.15                   |

#### Proposed Informative ILdd budget

NOTE—The number of lanes n is equal to 1 for 200GAUI-1, 2 for 400GAUI-2, 4 for 800GAUI-4, and 8 for 1.6TAUI-8.

Figure 176E–2—Components of a 200 Gb/s per lane AUI-C2M and insertion loss budget at 53.125 GHz