# Evaluating Claims in the ACT/TDD Comparison: Corrections, Clarifications, and Evidence

Contribution to 802.3dm Task Force September 25, 2025

TJ Houck – Infineon

Jay Cordaro – Analog Devices

Ragnar Jonsson – Infineon

Alireza Razavi – Infineon

Hossein Sedarat – Ethernovia

Dance Wu – Infineon

# **Contributors**

- David Shen Infineon

- Peter van Dyck Infineon

# **Introduction**

This presentation points out some of the errors in the presentation "ACT and TDD Comparison", by Claude Gauthier and Frank Wang

https://www.ieee802.org/3/dm/public/0925/Gauthier\_Wang\_3dm\_01\_09152025.pdf

Email reflector brought these items to attention: <a href="https://www.ieee802.org/3/ISAAC/email/msg00534.html">https://www.ieee802.org/3/ISAAC/email/msg00534.html</a>

We believe these errors should be clarified by the authors

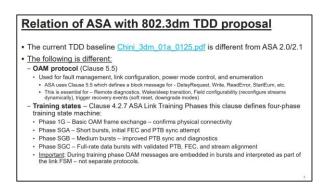

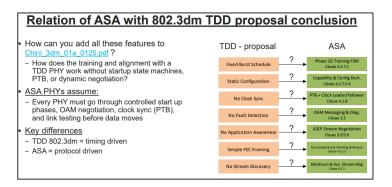

# **ASA-ML/MLE** ≠ **IEEE** TDD

- The slides in the <u>Gauthier\_Wang presentation</u> comparison use ASA-ML/MLE results and language in support of the IEEE TDD proposal.

- 2. ASA-ML and ASA-MLE are both TDD-style duplexing method but differ materially from the IEEE TDD under consideration.

- They are not interchangeable and are not guaranteed interoperable.

- 3. Please label ASA content explicitly and avoid using it as evidence for IEEE TDD unless the underlying specification and test conditions are made available for review. [See Slides 14–5, 27, 34.]

IEEE 802.3dm Task Force Evolution of 802.3dm

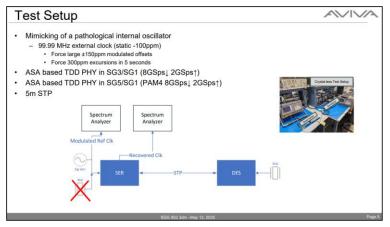

# Crystal-less operation, PoC & EMC.

- 1. ACT has demonstrated crystal-less operation with PoC and has passed EMC in like-for-like setups.

- Replacing a crystal with an external signal generator with 100ppm offset and then modulating with an unspecified additional ppm offset.

- · This is not a correct demonstration of crystal-less.

- The EMC slides do not present comparable TDD data (only ASA data).

- 3. Please provide evidence with TDD using similar test setups and limits, or clarify the comparison.

- 4. Comparing CISPR 25 "noise floors" across different receivers/setups is not valid. [Slides 14, 22–23.]

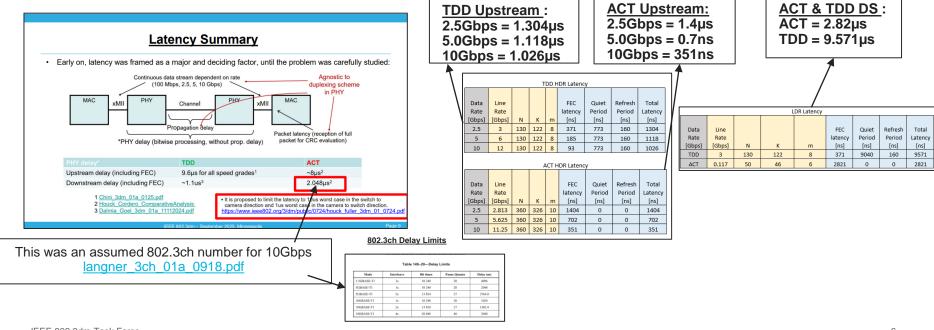

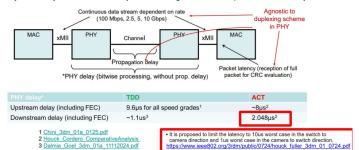

## Latency/link-delay accounting (uplink, buffers, IBGs)

- 1. The 2.048µsec referenced is from 802.3ch specification

- Please clarify how TDD can be faster latency than ACT with Quite Period and Refresh Period. See the ACT latency numbers for DS and US [Slides 20–21, 31.]

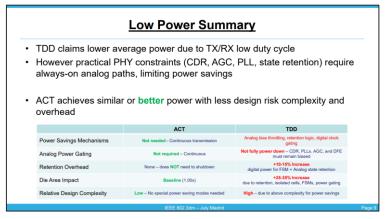

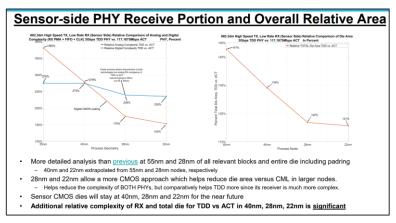

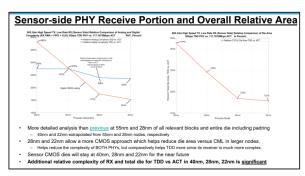

# Power, complexity, and die-size claims.

- Claims that a multi-Gbps TDD PHY can be smaller/simpler or lower-power than a 100Mbps architecture

- This Ignores equalization, linearity, and additional low-power state machinery required for TDD

- 2. ACT does not require EEE modes to hit low power.

- 3. TDD adds complexity for aggressive power modes which increases die area.

- 4. Please clarify these assertions [Slides 16–19, 23.]

# Bandwidth/ISI and low-frequency behavior

- TDD's higher downstream bandwidth drives slightly higher complex one could argue it is similar to ACT complexity

- 2. TDD Upstream rate (3Gbps 100Mbps) drives complexity higher compared to ACT 100Mbps

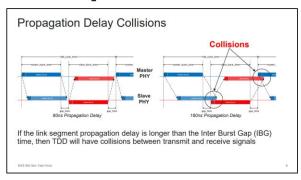

- 3. TDD is sensitive to longer propagation delays

- Raising collision and baseline-wander risks on long links. jonsson 3dm 01 06 26 25.pdf

- Please address these effects directly rather than assuming parity with ACT. [Slides 15, 24, 30.]

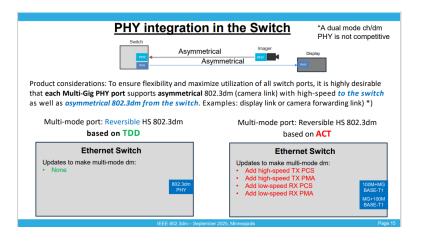

# "Reversibility" and other non-objective features

- 1. Reversibility and several other items cited are not part of the 802.3dm objectives.

- System implementations for reverse direction PHYs have not been discussed

- If authors intend to propose objective changes, please call them out explicitly and provide rationale.

- 3. Otherwise, these should be clarified from the comparison claims. [Slides 14, 26, 32–33.]

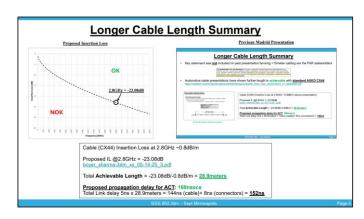

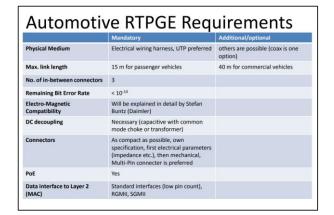

# Cable-length market data

- 1. Please expand beyond a single passenger-vehicle example (BMW X5/X6/X7) and address commercial/off-highway needs.

[Example: Car dimension and link length for camera]

- The use case listed is for a specific OEM.

| Carrière | Carrière

matheus\_ISAAC\_03\_1411202327\_v1.0b.pdf

- 2. Earlier industry inputs request up to ~40 m for certain use cases. [Slide 30.]

- 3. OICA 2023 vehicles sales **Passenger** = <u>67.13Million</u> / Commercial = <u>26.4Million</u> <a href="https://www.oica.net/category/production-statistics/2023-statistics/">https://www.oica.net/category/production-statistics/2023-statistics/</a>

Houck Cordaro Chimento 3dm 01a 0925.pdf

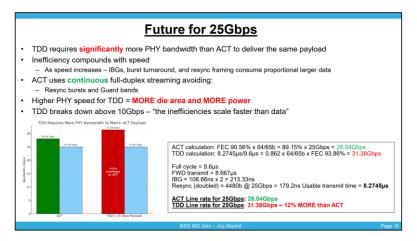

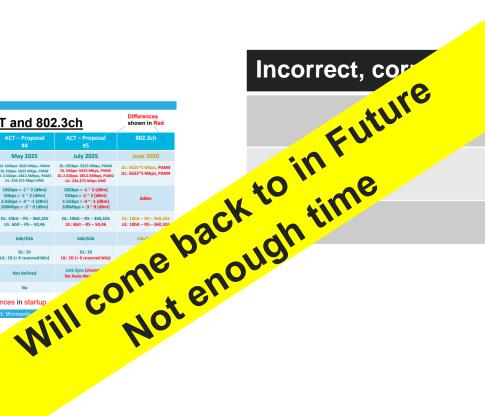

# 25Gbps

- 1. Please check the math, it is believed to have a miscalculation.

- 25 Gbps is not to extend the scope but to check forward scalability [Slide 31.]

- There was also interest for additional higher speed from co-author raised previously

- TDD's Timing/echo/IBG assumptions may need to evolve at higher rates.

|                                    | ACT or<br>802.3ch | ACT – Proposal                                                                                                                                                                                                   | ASA or<br>TDD | ASA or TDD – Proposal                                                                                                                                                                                                                                                |

|------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal-less                       | ACT               | Proven working solution for ACT SERDES also has a proven working solution in mass production  GMSLE Baseline Proposal for IEEE 802.3dm  Lo 3dm_01_050125.pdf   wu_3dm_01a_072925.pdf                             | ASA           | <b>Theorized</b> – several subjects left open still  This presentation is not a demonstration of crystal-less  operation  Ng 3dm 01 05122025.pdf                                                                                                                     |

| EMC – Radar<br>Pulse               | ACT               | Proven ACT silicon – Passed 600V/m – Unshielded/PoC/Crystal-<br>less and Proposed ACT specification<br>jonsson 3dm 01 07 15 24.pdf   GMSLE FDD PHY Simulation Results and PHY Complexity<br>wu 3dm 01 072925.pdf | ASA           | Tested with ASA <b>NOT</b> proposed TDD. <b>ASA</b> shows Radar 600V/m Unshielded – <b>No PoC or crystal-less results</b> Zerna 3dm 01 250729.pdf   Dalmia Ng EMI COAX 3dm 01 04172025.pdf  Ng Dalmia 3dm 03a 09152025.pdf                                           |

| Power consumption                  | ACT               | Best Power performance due to low complexity  Comparative Analysis for GMSLE/ACT, and TDD sedarat 3dm 02 202503.pdf - contains 8 presentation links                                                              | TDD           | Equal w/ power control or Higher w/ no power control  >3x the power of ACT w/ no power control  Requires power reduction circuitry that will cause die size increase to achieve near equal power to ACT  Chini 3dm 02b 0325.pdf   Houck Cordaro 3dm 01d 07292025.pdf |

| Size and complexity                | ACT               | Smallest die size shown in several presentations due to low complexity  Houck 3dm 01 0121 5.pdf   jonsson 3dm 02 06 26 25.pdf  Houck Cordaro 3dm 01d 07292025.pdf                                                | TDD           | Larger die size due to higher speed rates and TDD complexity Chini 3dm 02b 0325.pdf   Houck Cordaro 3dm 01d 07292025.pdf                                                                                                                                             |

| Longer Cable<br>Length             | ACT               | Capable of 20-30meters with standard coax Propagation Delay = 160nsecs – limited by insertion loss Link Propagation Delay in IEEE 802.3dm: System Implications and Trade offs                                    | TDD           | Capable of <b>No</b> more than <b>15meters – collisions possible</b> jonsson 3dm 01 06 26 25.pdf  Propagation Delay proposed = <b>84nsec</b> gorshe 3dm 01 250710.pdf                                                                                                |

| Future for 25Gbps                  | ACT               | Less complexity solution for high-speed, full duplex payload delivery  PAR Scope and Physical Layer Rates between 10 Gbps and 25 Gbps                                                                            | TDD           | Most complex path to 25Gbps – requires higher PHY rates,<br>strict timing, and burst synchronization<br>PAR Scope and Physical Layer Rates between 10 Gbps and 25 Gbps                                                                                               |

| Interoperability                   | -                 | PHY vendors can leverage 802.3ch PHYs                                                                                                                                                                            | -             | TDD – <b>ASA with changes and large compatibility issues</b> IEEE 802.3dm PHY evolution Comparative Analysis for GMSLE, ACT, and TDD approaches                                                                                                                      |

| Image and<br>Switch<br>Integration | ACT               | Lowest complexity                                                                                                                                                                                                | TDD           | More complex                                                                                                                                                                                                                                                         |

| PoC complexity                     | ACT               | 1 inductor Simulation Results and PHY Complexity   Designing Effective PoC Filters   Houck Cordaro 3dm 01d 07292025.pdf                                                                                          | TDD           | 2 inductors - no 1 inductor solutions with 15m w/ 4inlines  Chini Tazebay 3dm 01a 0924.pdf  jingcong dm 2024Sep v2.pdf   jonsson 3dm 02 06 26 25.pdf                                                                                                                 |

# Details of Inaccurate and Misleading Information

#### Comparison Table TDD - Proposal ACT - Proposal Proven working solution for TDD Not demonstrated. DME has high jitter w/o equalization. Crystal-less Na 3dm 01 05122025.pdf Proprietary SerDes are not DME based and use equalization **Duplexing** in Starte in TDD Starts in TDD! Startup (remains in TDD for higher SNR) (switches from TDD to ACT after startup) BEST Available Technology Inferior performance compared to TDD. High number of missing tests for Coax. Zerna 3dm 01 250729.pdf | Dalmia Ng EMI COAX 3dm 01 04172025.pdf **EMC** STP not shown DeSerializer side is complicated. Performance: Lower SNR Optimum for Ser and DeSer, Better SNR, Power, Performance, Area Dalmia 3dm 01 03102025.pdf | Chini 3dm 02b 0325.pdf | Chini 3dm 02a 0525.pdf Chini 3dm 02 07272025.pdf Power: mode like EEE is not available Lo\_3dm\_02a\_0125.pdf TDD is supported by imager vendors No evidence of ACT support by imager vendors Imager and Switch Integration Switch side needs Reversible Asymmetrical PHYs Much more complex to reverse high-speed direction matheus\_dm\_01e\_comparison\_20250727.pdf PHY vendors can leverage ASA-ML Interop between ACT and 802,3ch is not possible Interoperability (proven interop between 5 vendors) Autoneg, Link Sync, Modulation, FEC are different (see slide 14) ASA Press Releases and announcements Lowest complexity for 1 Gbps Uplink. 1 Gbps UL is non-linearly complex. Complete PHY Linear scaling to higher Downlink speeds redesign is necessary for each DL/UL speed combination. **Future for Higher Rates** matheus\_dm\_01e\_comparison\_20250727.pdf matheus\_dm\_01e\_comparison\_20250727.pdf No issue in both DL and UIL ACT fails its own requirements in DI Latency matheus\_dm\_01e\_comparison\_20250727.pdf houck fuller 3dm 01 0724.pdf

## Incorrect, corrections needed

**Incorrect**: Crystal-less operation has been demonstrated, see slide 3 wu 3dm 01a 072925.pdf

**Incorrect**: ACT uses half duplex in training, not TDD

**Incorrect**: EMC test results for ACT show excellent performance, passing all EMC tests with coax (see <a href="wu\_3dm\_01a\_072925.pdf">wu\_3dm\_01a\_072925.pdf</a>). No test results have been shared for the new TDD, only ASA-ML.

**Incorrect**: There is no evidence that SerDes has a higher SNR than ACT. Theoretically, TDD upstream operates at a higher baud rate than ACT so that ACT will have better SNR than TDD.

Incorrect: EEE is not needed to achieve low power with ACT.

Incorrect: The complexity of the ACT architecture is lower than TDD

Incorrect: This is ASA not TDD - 802.3dm is TDD

**Incorrect and Misleading**: Reversibility is not part of PAR or Objectives. The PHY can be reversible is a strong indication that it's not fully optimized for the target application

**Misleading**: Versions of ASA and TDD are not interoperable. See p15 of <a href="https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf">https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf</a> for ASA/TDD interoperability issues.

Incorrect: See slide for more information - slide 20

**Incorrect**: See calculations – the reference used is for 802.3ch as an example.

|                                                                              | Comparison Table                                                                                                                                                                   |                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              | TDD - Proposal                                                                                                                                                                     | ACT – Proposal                                                                                                                                                                                                        |

| Link Length                                                                  | Capable of longer lengths with standard coax Enough SNR margin. Prop delay can be increased if use case requires                                                                   | Longer link length with standard coax not possible due to lack of margin (see EMC implementation) Echo cancellation grows exponentially with longer length                                                            |

| PoC Complexity                                                               | 1 small inductor<br>jingcong, dm, 2024Sep, v2.pdf   Chini Tazebay, 3dm, 01a, 0924.pdf<br>Zema, 802.3dm, 01, 263097. PoC. complexity, system.pdf  <br>Chini, 3dm, 01e, 07272025.pdf | I larger inductor claimed – Larger footprint, Lower current rating,     Higher power loss, and Higher cost     Inductor presented at IEEE is not valid!     Houds, 36m, 02, 0121, 5,pd (Ohin, 36m, 01c, 07272025 pdf) |

| PHY-level Sync                                                               | Low complexity sensor <b>sync</b> without engaging higher protocols<br>Higher precision<br>see slide 19                                                                            | High complexity sync — requires higher layer protocols  Lower precision  see slide 19                                                                                                                                 |

| Number of discreet ICs to provide complete set of Ser and DeSer combinations | Smallest number of product SKUs<br>Lowest development costs<br>Easy change of HS direction<br>matheus_dm_01e_comparison_20250727.pdf                                               | Very high number of product SKUs (as evidenced by proprietary SerDes)                                                                                                                                                 |

## Incorrect, corrections needed

**Incorrect**: The TDD proposal resist to adopt the tougher limit line proposed for insertion loss proposed in ACT. This fact, by itself, is a sign that TDD cannot operate on longer cables.

**Incorrect**: TDD has larger bandwidth, more ISI, and is sensitivity to longer propagation delay as shown in collision presentation below

https://ieee802.org/3/dm/public/adhoc/062625/jonsson\_3dm\_01\_06\_26\_25.pdf

**Incorrect**: No discussion of **Slide 19** on TDD, higher bandwidth than ACT and low frequency baseline wander issues <a href="https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf">https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf</a>

**Slide 5** – 2 inductors – no 1 inductor solutions with 15m w/ 4inlines <a href="https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf">https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf</a>

**Incorrect**: This is not synchronization. GPIO Delay Compensation is jitter control and is not TSN

Misleading: This is a implementation decision

Proprietary SerDes SKUs is not provided for comparison

#### 802.3dm OVERALL PPA Analysis: TDD vs ACT Camera DS highspeed Not complex Camera US lowspeed RX Proven. 10 vendors have announced TDD products. Higher processing rate drives higher power, despite the counterintuitive If complicated as claimed by ACT proponents, how is this possible? expectation otherwise Excluded parts of the design (missing blocks) to score a draw w/ TDE FCILLIS loweneer Not complex TX Complexity ECU DS highspeed RX Low complexity 8b FEC Higher complexity 10b FEC, ADC/DFE/Filtering Complexity Similar to camera-side (<3mW) Not yet provided, likely much higher due to FEC increase **ECU RX Power Consumption** Crystal-less Camera Serialize Proven working solution for TDD demonstrate Not demonstrated, DMF has high litter w/o equalization Proprietary SerDes are not DME based and use equalization Latency (including FEC) **Energy efficiency modes** Enables predetermined EEE to save power if Camera capability and Requires continuous transmission, no practical EEE line rate aren't aligned to 2.5/5/10 More complicated design than baseline (superposition of simultaneous US/DS Summary: PPA (Power - Performance - Area) is the industry norm to compare technologies Complexity is captured in one or more of these three aspects TDD outshines ACT when properly analyzed under PPA methodology

## **Incorrect, corrections needed**

**Incorrect**: TDD downstream transmit power is higher than ACT, burning more power, and requiring more circuit complexity/area to maintain linearity

Incorrect and Misleading: This is ASA not 802.3dm TDD proposed PHY. Information on how ASA MLE is not TDD:

Evolution of 802.3dm: From GMSLE to ACT and Beyond

**Incorrect and Misleading**: This is not possible. Even if we assume that power consumption scales linearly with symbol rate (which is not true) and account for the off time of a TDD receiver, it would still burn more power because TDD needs equalization.

**Misleading**: FEC complexity is a tradeoff between burst protection and complexity. Simpler TDD FEC has less robustness to burst errors.

**Incorrect**: It is not possible that the power consumption of the DS and US receivers be similar, when DS receiver is ON much longer time than US

**Incorrect**: ACT will be better FEC does not determine latency

**Incorrect**: ACT power savings does not require EEE to achieve low power – please clarify.

**Incorrect**: ESD design does not depend on whether simultaneous signaling occurs. Both TDD and ACT require Tx and Rx to be connected to the same pins for single pair wire support.

## **Camera Side Complexity and Power Summary**

- TDD Camera Receiver <0.012mm2, <3mW</li>

- · Processing rate 175MS/s

- · Proven Architecture in Automotive Serdes

- ACT Camera Receiver 0.012mm2, 3mW (Missing Blocks)

- Processing rate 468MS/s

- DME typically used in HDX Burst Communication, not FDX

Missing blocks: HPF, RX Clk Recovery (CDR/Fwd Clk). Link sync and auto-negotiation circuits. 4X sampling clock and decimation circuit. Slicer calibration circuit.

\*ACT Reference: https://www.ieee802.org/3/dm/public/0125/Lo\_3dm\_02a\_0125.pdf \*TDD Reference: https://www.ieee802.org/3/dm/public/0725/Chini\_3dm\_02\_07272025.pdf

The receiver blocks are a very small portion of total PHY (i.e. consider ESDI) and the PHY itself is a small portion

of a camera solution. TDD receiver supports link sync, speed negotiation and clock recovery, the filters are

smaller by a large factor and silicer is tiny, leading to a smaller overall relative cost.

IEEE 802.3dm - July Madric

age 4

## Incorrect, corrections needed

**Misleading and Incorrect**: 3Gbps PHY can never be smaller than 100Mbps especially with low power modes described. This is constraint by Physics of high speed design

See **slide 12** – size comparison

https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 0 1b 07292025.pdf

**Incorrect and Misleading**: Size comparison – this presentation does not include the low power complexity

https://www.ieee802.org/3/dm/public/0125/Houck\_3dm\_01\_0121\_5 .pdf

**Misleading**: TDD includes low power circuitry for turning off PHY and other states and don't see that included

See **page 9** discussing die size increase for low power states <a href="https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 0">https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 0</a> <a href="https://www.ieee802.org/10/2002/mouch.com">https://www.ieee802.org/10/2002/mouch.com</a> <a href="https://www.ieee802.org/10/2002/mouch.com"

#### **ECU Side Complexity and Power Summary**

- · No echo canceller, No high order filter.

- TDD ECU Receiver- Similar architecture as in the camera at 2.5Gbps 0.012mm2, <3mW</li>

- Similar architecture for 5Gbps, potentially with more DFE taps.

- · Low complexity 8-bit FEC

- No additional circuit for link synchronization and speed negotiation

- ACT ECU Receiver Area is not provided- Multiple architectures suggested or simulated.

- For Camera DS highspeed TX Complexity, the ACT version is more complex and needs higher supply to accommodate superposition of US/DS TX signals

- For ECU US lowspeed TX Complexity, similarly more complex than TDD and needs higher supply for same reason

ADC+FFE+DFE receiver + High order TX filtering

- Digital or analog echo cancellation, optimized for asymmetric signaling

- 10bit-FEC, very large increase in complexity and power compared o incumbent 8-bit FEC and TDD.

- Additional circuits needed for link synchronization and speed negotiation.

- TDD uses similar low complexity SerDes receiver architecture on the ECU side, making it several times more cost

efficient than ACT and incumbent solutions. ACT complexity on the ECU side is a concern as the complex FEC

requirement makes it difficult to compete even with the incumbent solutions.

IEEE 802.3dm - July Madrid

Page 4

## Incorrect, corrections needed

**Incorrect**: Not a significant factor in power or complexity of design. Supply voltage, process node, transmitter design is an implementer's decision

**Incorrect and Misleading**: No higher order Tx filtering needed. ADC based architecture is not required for high-speed receiver.

It is implementation choice.

**Incorrect**: FEC size at ECU-side is only 200% greater, 469% longer burst protection FEC size is very small and power insignificant, should not be determining factor.

#### Slide 10:

https://www.ieee802.org/3/dm/public/0725/Houck\_Cordaro\_3dm\_01b\_07292025.pdf

#### **Energy Efficiency Modes** Fps Res Blanking Data rate Many camera video streams have rates which do not fill the 2.5. Resolution 5, or 10 Gbps 2048 x 1080 30 12 +10% 0.88 Gbps Mainstream use cases will result in highly in-efficient utilization 4096 x 2160 30 12 +10% 3.5 Gbps Power saving is highly desirable 5840 x 2160 30 12 +15% 5.2 Gbps On-demand EEE may be difficult for such scenario (to small idle times), but prescheduled EEE is of interest 7200 x 2160 30 12 6.7 Gbps (see chart from matheus ISAAC 02 01092024.pdf) **ACT Limitations** Additional energy saving mechanism ACT requires continuous transmission for staying Not practical to initiate low power mode in case the link capacity is not fully utilize Sufficient if predetermine **TDD Advantages** Imager vendor Inherent gaps in the transmission 29 participants System synchronized automatically Additional energy saving via EEE possible with adjustment

## Incorrect, corrections needed

**Incorrect**: Imagers continuously transmit having low power minimal circuitry is lower risk

**Incorrect**: System does not automatically synchronize because of TDD. This requires processing

**Incorrect**: TDD requires continuous updates to stay synchronized

**Misleading**: Link is optimized per speed – the links are not dynamically changing speed

**Incorrect**: TDD low power modes require power – the circuitry is not a light switch it can't be shut off without consequences

#### Slide 9

https://www.ieee802.org/3/dm/public/0725/Houck Cordaro 3dm 01b 07292025.pdf

### **Latency Summary**

Early on, latency was framed as a major and deciding factor, until the problem was carefully studied:

## Incorrect, corrections needed

**Misleading**: Not calling out all speed grade delays – this is for 10Gbps

2.048usec was used from 802.3ch specification

ACT latency with interleaving + FEC:

2.5Gbps = 1.404usec

5.0Gbps = 702ns/1.404usec | interleave = 1/2

10Gbps = 351ns/702ns/1.404us | interleave = 1/2/4

Missing: Links are not included in slide

| TDD HDR Latency        |                        |     |     |    |                        |                         |                           |                          |  |

|------------------------|------------------------|-----|-----|----|------------------------|-------------------------|---------------------------|--------------------------|--|

| Data<br>Rate<br>[Gbps] | Line<br>Rate<br>[Gbps] | N   | K   | m  | FEC<br>latency<br>[ns] | Quiet<br>Period<br>[ns] | Refresh<br>Period<br>[ns] | Total<br>Latency<br>[ns] |  |

| 2.5                    | 3                      | 130 | 122 | 8  | 371                    | 773                     | 160                       | 1304                     |  |

| 5                      | 6                      | 130 | 122 | 8  | 185                    | 773                     | 160                       | 1118                     |  |

| 10                     | 12                     | 130 | 122 | 8  | 93                     | 773                     | 160                       | 1026                     |  |

|                        | ACT HDR Latency        |     |     |    |                        |                         |                           |                          |  |

| Data<br>Rate<br>[Gbps] | Line<br>Rate<br>[Gbps] | N   | к   | m  | FEC<br>latency<br>[ns] | Quiet<br>Period<br>[ns] | Refresh<br>Period<br>[ns] | Total<br>Latency<br>[ns] |  |

| 2.5                    | 2.813                  | 360 | 326 | 10 | 1404                   | 0                       | 0                         | 1404                     |  |

| 5                      | 5.625                  | 360 | 326 | 10 | 702                    | 0                       | 0                         | 702                      |  |

| 10                     | 11.25                  | 360 | 326 | 10 | 351                    | 0                       | 0                         | 351                      |  |

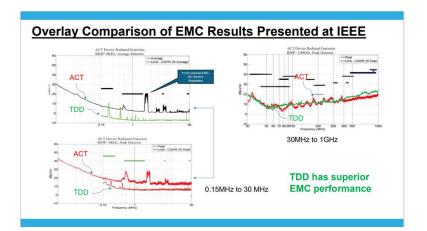

## **EMC CISPR Results – BIG PICTURE**

| Coax Emissions               | Complete set<br>Published                                                                         | >Half of results not published<br>(Most plots show less margin than TDD)                                                                  |

|------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Coax<br>Radiated<br>Immunity | 2 meter cable – Yes     7 meter cable – Yes     12 meter cable – Yes     Complete frequency range | 2 meter cable – Yes     7 meter cable – NO     12 meter cable – NO     Starting near 400MHz, end at 3.4GHz (critical frequencies missing) |

| Coax BCI                     | 15cm – Yes<br>45cm – Yes<br>75cm – Yes                                                            | 15cm - Not shown in the setup<br>45cm - Yes<br>75cm - ?                                                                                   |

| STP Emissions                | Complete set published                                                                            | NO results published                                                                                                                      |

| STP Radiated immunity        | Yes                                                                                               | NO results published                                                                                                                      |

| STP BCI                      | Yes                                                                                               | NO results published                                                                                                                      |

Summary of results published till July 2025. Non CISPR tests are addressed elsewhere.

IEEE 802.3dm - September 2025, Minneapolis

Page 1

## **Corrections and Clarification needed**

**Misleading**: What was timing, bandwidth, and frequencies for DL/UL tested?

Is this TDD or ASA?

If the above differs ASA is not TDD as specified <u>Evolution of</u> 802.3dm: From GMSLE to ACT and Beyond

Review **Slide 9** – TDD is Time driven ASA is Protocol driven

## Incorrect, corrections needed

Misleading: Is this TDD or ASA? Please specify exact timing

**Misleading**: ACT tested Crystal-less and PoC – TDD did not

Review Slide 3

https://www.ieee802.org/3/dm/public/0725/wu\_3dm\_01a\_07292 5.pdf

**Incorrect**: to compare the noise floor (where there are no peaks) between different CISPR25 measurements.

The noise floor depends on the equipment used in the test (LNA noise figure, spectrum analyzer type), independent of the modulation type.

**Misleading**: Radiated emissions is very dependent on board and cable type.

It is not valid to compare different test setups for relative performance.

#### **PoC Complexity**

- TDD does not have a low-speed backward channel occupying low frequency range and thus 1 inductor solution can be achieved

jingcong\_dm\_2024Sep\_v2.pdf

- 1µH inductor is suggested for TDD under 802.3dm MDI Return Loss and there are many good candidates available in the market.

Chipi 3dm 01c 07272025 pdf

- . TDD's 1 inductor solution has LOWER footprint, HIGHER current rating, LOWER power loss, and LOWER relative cost.

#### ACT Questions

- Houck\_3dm\_02\_0121\_5.pdf claimed that the inductor impedance for ACT should be larger than 1k ohm across 20MHz 3000MHz and then 1 inductor solution with 6.8µH, e.g., 1210POCB-682, was introduced as shown in the left figure.

- However, the impedance for 1210POCB-682 has been updated and NO alternative is provided for ACT.

- A mystery PoC inductor that has inductance > 10µH may be applicable for ACT no specific information has been presented.

## Incorrect, corrections needed

**Misleading**: Does the 1uH TDD 1 inductor solution work with EMC and 15 meters with 4 in-line cables?

Incorrect: Return Loss does not prove a valid solution

**Incorrect**: TDD requires impedance – no discussion – review impedance presentation again and comparison presentation on why this is critical

No discussion of **slide 19** on TDD, higher bandwidth than ACT and low frequency baseline wander issues

https://www.ieee802.org/3/dm/public/0725/Houck\_Cordaro\_3dm\_0\_1b\_07292025.pdf

Baseline wander issues for TDD (Low frequency)

https://ieee802.org/3/dm/public/adhoc/062625/jonsson\_3dm\_02\_06\_26\_25.pdf

Why Impedance Matters – review full presentation and explain why TDD does not require impedance when Low frequency content is present

https://www.ieee802.org/3/dm/public/0125/Houck\_3dm\_01\_0121\_5.pdf

Interoperability between ACT and 802.3ch

ACT - Proposal Released Sept 2024 Nov 2024 Jan 2025 DL: 5625\*S M, PAM4 DL: 5625\*S Mbps, Baud rate and UL: 104.625 M DL: 5625\*S Mbps, PAM4 DL SGbos: S625 Mbos. PAM2 PAM2,234.375/281.25M UL: 234.375 Mbps DME modulation UL: 234.375 Mbps DME STP DL: 0dBm DL: 0dBm DL: 0dBm Transmit UL: -6dBm UL: -6dBm UL: 0dBm 2 5Ghns = -4 ~ -1 (dRm) power DL: 10bit - RS -DL: 10bit RS - 360.326 DL: 10bit RS 360.326 DL: 10bit - RS - 360.326 FEC 360 326 UL: 5bit -RS - 2 FECs UL: 6bit - RS - 50.46 UL: 6bit - RS - 50,46 DL: 64b/65b DL: 64b/65b 64b/65b Line coding

ACT and 802.3ch have fundamental differences in startup.

III : 16h/17h

DL: 10

UL: 4

Not defined

DL: 10

UL: ? (16 reserved bits)

Not defined

UL: 10 (+ 6 reserved bits)

UL: 2 types DL: 10

UL: none/2

Not defined

OAM bits

synchronize

start of training EEE capability

eded

## **Comments**

**Misleading**: This is a implementation decision and not a part of PAR/objective

PHYs are fixed during production

Why would display and camera ports be changing in production? This is a physical link and PHY would be optimized per customer application

This is the whole advantage of 802.3dm over 802.3ch

**Incorrect**: This is a disadvantage for TDD when comparing optimized ACT product

TDD – 2 x FAST TX/RX PHYs capable of 12Gbps – More die size compared to ACT not cost competitive to ACT now

ACT 1 x FAST RX and 1 x FAST TX

**Misleading**: TDD has 1 additional FAST TX and FAST RX per PHY with this application

This is a large increase in die size will double the die size of an ACT optimized PHY

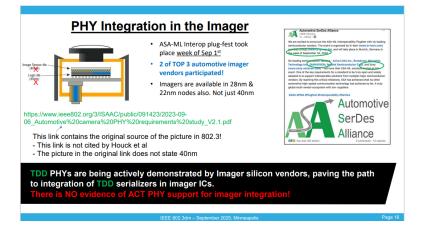

## Incorrect, corrections needed

**Misleading**: TDD is not ASA – why is information of another standard's plugfest shown in 802.3dm is this appropriate for IEEE?

Information on how ASA MLE is not TDD:

Evolution of 802.3dm: From GMSLE to ACT and Beyond

TDD = Timing Driven

ASA = Protocol Driven

**Incorrect**: ASA-ML has not been proposed to 802.3dm only ASA MLE

**Incorrect**: ASA ML/ASA MLE and TDD are not interoperable Does TDD PHY proposed in 802.3dm operate with ASA-ML parts?

**Slides 4, 5, 6, and 7** describe this relationship Evolution of 802.3dm: From GMSLE to ACT and Beyond

## **Crystal-less Summary**

- Clock recovery was passed by a motion to be an 802.3dm objective

- Crystal-less operation for TDD is demonstrated in Ng 3dm 01 05122025.pdf

#### ACT Limitations

- It has been demonstrated that DME signal accumulates data-dependent jitter

- Without equalization, the jitter is excessive for proper clock recovery

- Clause 98 Autoneg is not shown to work for ACT crystal-less operation

#### TDD Advantages

- During upstream burst, 3Gbps signal available for clock recovery circuit. This is >10x better than ACT signal.

- During guiet gaps, modern digital PLLs easily hold the learned frequency

- Incoming signal that is used for clock recovery has better jitter properties than ACT signal

- TDD startup is inherently ok for crystal-less operation

802 3dm – September 2025, Minneapolis

Page 17

## Incorrect, corrections needed

**Incorrect**: Differential Manchester Encoded (DME) modulation is a mature and robust method which has been used for decades in communications

**Incorrect**: Clause 98 is an optional part of the ACT proposal and has nothing to do with ACT crystal-less operation

**Incorrect**: Incoming signal does not have better jitter properties than a DME ACT signal with proper timing recovery.

## **Crystal-less and Autoneg** · 55% of survey participants from the automotive industry may use autoneg matheus ISAAC 02 01092024.pdf Nice to have, if "free Nice to have, even with cost adder **ACT Limitations** - Clause 98 Autoneg is not shown to work for crystal-less operation **TDD Advantages** - Has inherent ("free") autoneg for high-speed during startup (via capability exchange Crystalless operation is not affected by autoneg or startup

# Incorrect, correction needed Will come back to in Future Not enough time

#### Cable Length

#### P802.3dm adopted a 15m length objective

- · Shown to be adequate for all passenger cars, utility vans, and city/regional buses (matheus ionsson dalmia ISAAC 01 1411202327 v1.0.pdf. matheus ISAAC 03 1411202327 v1.0b.pdf)

- · The need for longer cable not substantiated

- Potential volume in other markets (industrial automation. aerospace) small with no impact into automotive market

#### **ACT Limitations**

- Cable length limitations known with incumbents video/6314704574112

- Link length cannot be better for ACT than for incumbents

- Smaller SNR margin than TDD limits the reach

#### TDD Advantages

- Sufficient SNR margin to cover longer cable reach with standard cables

- >20m achievable with common cable, more if needed

- Re-use of channel and component specification possible

- . >20m easily achievable with e.g. 90 ns delay limit

- → Length is II. limited and not delay limited

## Incorrect, corrections needed

Incorrect: SNR does not cover the Link Delay issues as described in the comparison presentation.

**Incorrect**: Collisions will occur – **Slide 5** comparison table under Long Cable Length

https://ieee802.org/3/dm/public/adhoc/062625/jonsson 3dm 01 06 26 25.pdf

**Incorrect**: Both references do not provide data disagreeing with 15meters

Only referenced for BMW X5, X6, X7 – Where is the market data for other vehicles? This only shows 11m's

Misleading: hogenmuller 01 0512.pdf requests 40 meters for commercial vehicles - which is reference on slide 4

https://www.ieee802.org/3/ISAAC/public/1123/matheus jonsson d almia ISAAC 01 1411202327 v1.0.pdf

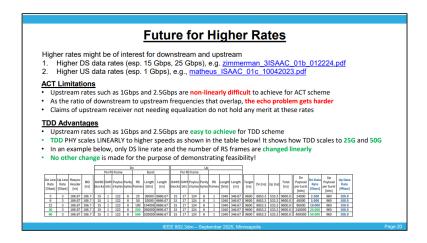

## **Future for Higher Rates**

Higher rates might be of interest for downstream and upstream

- 1. Higher DS data rates (esp. 15 Gbps, 25 Gbps), e.g. zimmerman 3ISAAC 01b 012224.pdf

- Higher US data rates (esp. 1 Gbps), e.g., matheus ISAAC 01c 10042023.pdf

#### **ACT Limitations**

- Upstream rates such as 1Gbps and 2.5Gbps are non-linearly difficult to achieve for ACT scheme

- As the ratio of downstream to upstream frequencies that overlap, the echo problem gets harder

- · Claims of upstream receiver not needing equalization do not hold any merit at these rates

#### TDD Advantages

- Upstream rates such as 1Gbps and 2.5Gbps are easy to achieve for TDD scheme

- TDD PHY scales LINEARLY to higher speeds as shown in the table below! It shows how TDD scales to 25G and 50G

- . In an example below, only DS line rate and the number of RS frames are changed linearly

- . No other change is made for the purpose of demonstrating feasibility!

|                           |   |                          |             | Dn |       |                   |   |              |                  | Uo      |    |       |                   |   |   |      |                |                |         |         |               |                                      |                           |                                      |                           |

|---------------------------|---|--------------------------|-------------|----|-------|-------------------|---|--------------|------------------|---------|----|-------|-------------------|---|---|------|----------------|----------------|---------|---------|---------------|--------------------------------------|---------------------------|--------------------------------------|---------------------------|

|                           |   |                          |             |    | Per R | \$ frame          |   |              | Burst            |         |    | Per R | \$ frame          |   |   |      |                |                |         |         |               |                                      |                           |                                      |                           |

| On Line<br>Rate<br>[Gbps] |   | Resync<br>Header<br>(ns) | IBG<br>(ns) |    |       | Payloa<br>d bytes |   | RS<br>frames | Length<br>(bits) |         |    |       | Payloa<br>d bytes |   |   |      | Length<br>[ns] | Target<br>(ns) | Dn [ns] | Up [ns] | Total<br>(ns) | Dn<br>Paytoad<br>per burst<br>[bits] | On Data<br>Rate<br>[Gbps] | Up<br>Payload<br>per burst<br>[bits] | Up Data<br>Rate<br>[Mbps] |

| 3                         | 3 | 186.67                   | 106.7       | 15 | 1     | 122               | 8 | 25           | 26000            | 8666.67 | 15 | 17    | 124               | 6 | 1 |      | 346.67         | 9600           | 8853.3  |         | 9600.0        | 24000                                | 2.500                     | 960                                  | 100.0                     |

| 6                         | 3 | 186.67                   | 106.7       | 15 | 1     | 122               | 8 | 50           | 52000            | 8666.67 | 15 | 17    | 124               | 6 | 1 | 1040 | 346.67         | 9600           | 8853.3  | 533.3   | 9600.0        | 48000                                | 5.000                     | 960                                  | 100.0                     |

| 12                        | 3 | 186.67                   | 106.7       | 15 | 1     | 122               | 8 | 100          | 104000           | 8666.67 | 15 | 17    | 124               | 6 | 1 | 1040 | 346.67         | 9600           | 8853.3  | 533.3   | 9600.0        | 96000                                | 10.000                    | 960                                  | 100.0                     |

| 30                        | 3 | 186.67                   | 106.7       | 15 | 1     | 122               | 8 | 250          | 260000           | 8666.67 | 15 | 17    | 124               | 6 | 1 | 1040 | 346.67         | 9600           | 8853.3  | 533.3   | 0.0000        | 240000                               | 25.000                    | 960                                  | 100.0                     |

| 60                        | 3 | 186.67                   | 106.7       | 15 | 1     | 122               | 8 | 500          | 520000           | 8666.67 | 15 | 17    | 124               | 6 | 1 | 1040 | 346.67         | 9600           | 8853.3  | 533.3   | 9600.0        | 480000                               | 50,000                    | 960                                  | 100.0                     |

IEEE 802 3dm - September 2025, Minneapolis

Page 20

## Incorrect, corrections needed

Incorrect: Ignored the IBGs

See presentation breakdown that describes this behavior **Page 16** <a href="https://www.ieee802.org/3/dm/public/0725/Houck\_Cordaro\_3dm\_0">https://www.ieee802.org/3/dm/public/0725/Houck\_Cordaro\_3dm\_0</a> <a href="https://www.ieee802.org/3/dm/public/0725/Houck\_Cordaro\_3dm\_0</a> <a

**Incorrect**: 30Gbps Downlink = 23.89Gbps payload

8.6667/9.6 = 0.90278

$0.90278 \times 64/65 \times 122/130 = 0.83231 \times 30$ Gbps = 25.03Gbps

Now with Overhead included = 30Gbps x 0.79644 = 23.89Gbps

25Gbps/0.79644 = 31.38Gbps total bandwidth

**Incorrect**: 1Gbps is currently not apart of the PAR/objectives

Misleading: Echo is hard for both TDD and ACT at 25Gbps

TDD will likely have to change IBG to allow more frequency content to settle – Meaning not compatible with 2.5/5.0/10Gbps timing

### **PHY-level Sync**

It is desirable to synchronize camera shutters in certain use cases (e.g. 360° images)

Legacy implementations use GPIOs from the SoC to sent vsynch signals using hardware.

Unsynchronized videos cause the need for a larger video buffer. 802.3 PHYs do not incorporate a special side channel for GPIOs

#### **ACT Limitations**

ACT higher layer protocol support is needed for synchronization

Requires IEEE 802.1AS TSN (about 80ns accuracy) to be adapted for asymmetric communication Requires changes from known implementations (both hardware and software)

#### TDD Advantages

Inherent precision time base in the PHY laver

+/- 5.3 ns accuracy for delay compensated GPIO for shutter synchronization

Leverages from known implementations (ASA-ML)

IEEE 802 3dm - September 2025, Minneapoli

Page 2

## Incorrect, corrections needed

Delay compensation is a feature that can be implemented in ACT. SERDES accomplishes delay compensation without TSN

This is an implementation decision and not a part of the 802.3dm PAR/objective.

This is not unique to TDD. It was copied from SERDES, which originally invented this feature.

ACT does not require hardware and software changes it has built in low latency behavior

**Incorrect**: TSN is not required for ACT.

**Incorrect**: ACT GPIOs are fast-acting, as stated last September (Hamburg), and were the reason ASA-MLE did not move forward. TDD is now proposed due to latency issues.

Review the entire presentation for the history of latency in 802.3dm: <a href="https://www.ieee802.org/3/dm/public/0924/Houck Fuller 3dm 03 0917">https://www.ieee802.org/3/dm/public/0924/Houck Fuller 3dm 03 0917</a>.pd

Where did the 5.3ns accuracy come from? No link or calculation or method explaining.

No reasoning behind why this is needed for customers and more importantly why the standard needs this

**TDD**

One efficient product when change of high-speed direction is easy to realize

S=Serializer D=DeSerializer

Five products when the change of highspeed direction is costly to realize

Product considerations:

Every part causes significant development effort.

The more parts needed, the more the time and the cost. Unlikely to have multi-vendor offers for each.

| # parts to cover all options | TDD    | ACT      |

|------------------------------|--------|----------|

| Single port                  | 1 (3)  | 2 (6)    |

| Dual port                    | 1 (6)  | 3 (21)   |

| Quad port                    | 1 (15) | 5 (126)  |

| Overall                      | 3 (24) | 10 (153) |

These number increase over proportionally when additionally optimizing for the three different speeds (in brackets)

ACT will lead to significantly more development effort.

## Incorrect, corrections needed

**Misleading**: This is a implementation decision

**Misleading**: All the ACT dies are far more competitive in price than the TDD PHY as mentioned in previous slide

**Misleading**: This is an implementation decision not an advantage

**Incorrect**: This is a disadvantage when comparing optimized product

TDD – 2 x FAST TX/RX PHYs capable of 12Gbps – More die size compared to ACT not cost competitive to ACT now

ACT 1 x FAST RX and 1 x FAST TX

### **Eco-System Summary**

- Conformance & interoperability PHY specification are only the first step for wide market adoption. A fully

established eco-system is required to successfully deploy a particular technology in automotive market.

- This eco-system comprises (among other)

- a physical layer specification,

- silicon availability (multi-vendor solution),

- test houses (conformance, interoperability, and EMC testing),

- testability (multiple test equipment vendors).

- channel & components (cable, connector, magnetic vendors) and EMC test specification

#### **ACT Limitations**

- No available eco-system to leverage from

- New channel and component specifications required

- Few communalities between proprietary SerDes and ACT (different Baud rate, different US modulation)

#### TDD Advantages

- Eco-system available

- Re-use of channel & component as well as EMC specification

- 6+ vendors with extensive experience

EEE 802.3dm – September 2025, Minneapolis

Page 23

## Incorrect, corrections needed

**Incorrect**: ASA has not been proposed to 802.3dm - no 802.3dm proposed TDD has a working PHY

**Misleading**: ASA and TDD are not interoperable – there has been no proposal on this

Does TDD PHY proposed in 802.3dm operate with ASA parts?

Slides 4, 5, 6, and 7 describe this relationship Evolution of 802.3dm: From GMSLE to ACT and Beyond

|                           | <u>Summary</u>                                                    |                                                                    |

|---------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

|                           | TDD                                                               | ACT                                                                |

| Crystal-less              | Demonstrated                                                      | Breaks auto-negotiation                                            |

| EMC                       | Proven robust                                                     | Incomplete disclosure suggests real issues                         |

| Power, Size, Complexity   | Suited to the application                                         | Higher DS latency, no on-demand EEE possible                       |

| Higher speed              | Lowest complexity (simple scaling)                                | Requires complete overhaul                                         |

| Cable Length              | Supports objective of >15meters with higher SNR margin            | Lower SNR margin                                                   |

| Interoperability          | Proven interop between 5 vendors for TDD-based ASA-ML             | No                                                                 |

| Integration               | Proven support from imager vendors                                | No evidence of support                                             |

| PHY-level SYNC            | Inherently built into TDD                                         | Not Defined                                                        |

| Ecosystem                 | Exists to leverage from                                           | Years behind                                                       |

| Number of Implementations | Optimal for creating variants of chips needed to serve the market | Unreasonably large number of chips needed to servable applications |

## **Incorrect, corrections needed**

**Incorrect and Misleading**: Requires clarification to table with possible corrections discussed above

# Thank You