LLID: Logical Link Identifier LGID: Logical Group Identifier

## 64.3.3 Discovery Processing

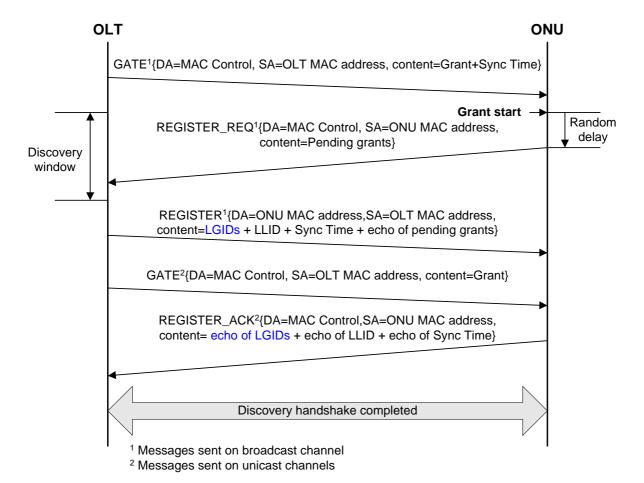

Discovery is the process whereby newly connected or off-line ONUs are provided access to the PON. The process is driven by the OLT, which periodically makes available Discovery Time Windows during which offline ONU's are given the opportunity to make themselves known to the OLT. The periodicity of these windows is unspecified and left up to the implementer. The OLT signifies that a discovery period is occurring by broadcasting a discovery gate message, which includes the starting time and length of the discovery window. Off-line ONUs, upon receiving this message, wait for the period to begin and then transmit a Register Reg message to the OLT. Discovery windows are unique in that they are the only times where multiple ONUs can access the PON simultaneously, and transmission overlap can occur. In order to reduce transmission overlaps, a contention algorithm is used by all ONUs. Measures are taken to reduce the probability for overlaps by artificially simulating a random distribution of distances from the OLT. Each ONU shall wait a random amount of time before transmitting the Register\_Req message that is shorter than the length of the discovery time window. It should be noted that multiple valid Register Reg messages can be received by the OLT during a single discovery time period. Included in the Register\_Req message is the ONU's MAC address and number of maximum pending grants. Upon receipt of a valid Register\_Req message, the OLT registers the ONU, allocating and assigning new port identities (LLIDs), and bonding corresponding MACs to the LLIDs. Additionally, the OLT assigns new group identifies (LGIDs), for grouping or separating some ports from other port groups. These LGIDs can be related to the VLAN group identifiers (VIDs) or multicast address/addresses, and can be applied for link segregation or multicasting.

. . .

Figure 64-14 - Discovery Handshake Message Exchange

## 65. Extensions of the Reconciliation Sublayer (RS) for Point to Point Emulation

. . .

## 65.1.3 Functional specifications

The variables below provide a mapping between MODE, <u>LGID</u> and LLID variables and multiple MACs. While the usage of this mapping is less interesting in the ONU, it is critical in the OLT. This mapping is used to replace transmitted preambles with MODE, <u>LGID</u> and LLID fields as well as to steer received packets to the appropriate MAC.

### **65.1.3.1 Variables**

enable

Value: Boolean

This variable shall be TRUE for an ONU MAC. For an OLT MAC, this variable is defined as below:

TRUE when management has assigned a value to mode, <u>logical group id</u> and logical\_link\_id. Indicates the MAC is enabled to receive frames.

FALSE when the MAC is not in use.

mode

Value: 1 bit

This variable shall be 0 for an ONU MAC and may be 0 or 1 for an OLT MAC.

When the LLID is used to emulate a single copy broadcast or multicast channel, this variable will be set to 1. When emulating a unicast channel, this variable will be set to 0.

logical\_group\_id

Value: 3 bit

This variable shall be assigned a value to indicate this MAC is grouped with this value.

logical\_link\_id

Value: 45-12 bits

This variable shall be set to the broadcast value of 0x<sup>2</sup>FFF for the unregistered ONU MAC. Enabled OLT MACs may use any value for this variable. Registered ONU MACs may use any value other than 0x<sup>2</sup>FFF for this variable.

### 65.1.3.2 Transmit

. . .

| Offset | Field      | Preamble/SFD | Modified preamble/SFD                                                         |

|--------|------------|--------------|-------------------------------------------------------------------------------|

| 1      | -          | 0x55         | same                                                                          |

| 2      | -          | 0x55         | same                                                                          |

| 3      | SPD        | 0x55         | 0xd5                                                                          |

| 4      | -          | 0x55         | Same                                                                          |

| 5      | -          | 0x55         | Same                                                                          |

| 6      | LLID[15:8] | 0x55         | <mode, group="" id[14:12],="" logical="" logical_link_id[1411:8]="">a</mode,> |

| 7      | LLID[7:0]  | 0x55         | <li><logical_link_id[7:0]><sup>b</sup></logical_link_id[7:0]></li>            |

| 8      | CRC8       | 0xd5         | The 8 bit CRC calculated over offset 3 through 7                              |

<sup>&</sup>lt;sup>a</sup>mode maps to TXD[7], logical\_link\_id[14] maps to TXD[6], logical\_link\_id[8] maps to TXD[0]

. . .

## 65.1.3.2.2 LLID

The LLID field is two octets in length and replaces the last two octets of preamble. The LLID field is a concatenation of the mode, <u>logical group id</u> and logical\_link\_id variables for the associated MAC.

. . .

# 65.1.3.3 Receive function

. . .

Table 65-2 shows the mapping of the modified preamble/SFD to RXD.

Table 65-2 - Preamble/SFD replacement mapping

| Signal | Bit va | Bit values of octets received through GMII <sup>a</sup> |   |                |   |   |                                 |                                 |                 |                 |  |

|--------|--------|---------------------------------------------------------|---|----------------|---|---|---------------------------------|---------------------------------|-----------------|-----------------|--|

| RXD0   | Х      | 1 <sup>b</sup>                                          | 1 | 1 <sup>c</sup> | 1 | 1 | logical_link_id[8] <sup>d</sup> | logical_link_id[0] <sup>e</sup> | X7 <sup>f</sup> | D0 <sup>g</sup> |  |

| RXD1   | Х      | 0                                                       | 0 | 0              | 0 | 0 | logical_link_id[9]              | logical_link_id[1]              | X6              | D1              |  |

| RXD2   | Х      | 1                                                       | 1 | 1              | 1 | 1 | logical_link_id[10]             | logical_link_id[2]              | X5              | D2              |  |

| RXD3   | Х      | 0                                                       | 0 | 0              | 0 | 0 | logical_link_id[11]             | logical_link_id[3]              | X4              | D3              |  |

| RXD4   | Х      | 1                                                       | 1 | 1              | 1 | 1 | logical_link_id[12]             | logical_link_id[4]              | Х3              | D4              |  |

|        |        |                                                         |   |                |   |   | logical_group_id[0]             |                                 |                 |                 |  |

| RXD5   | Х      | 0                                                       | 0 | 0              | 0 | 0 | logical_link_id[13]             | logical_link_id[5]              | X2              | D5              |  |

|        |        |                                                         |   |                |   |   | logical_group_id[1]             |                                 |                 |                 |  |

<sup>&</sup>lt;sup>b</sup>logical\_link\_id[7] maps to TXD[7], logical\_link\_id[0] maps to TXD[0]

| RXD6  | Х | 1 | 1 | 1 | 1 | 1 | logical_link_id[14] | logical_link_id[6] | X1 | D6 |

|-------|---|---|---|---|---|---|---------------------|--------------------|----|----|

| RXD7  | Χ | 0 | 0 | 1 | 0 | 0 | mode                | logical_link_id[7] | X0 | D7 |

| RX_DV | 0 | 1 | 1 | 1 | 1 | 1 | 1                   | 1                  | 1  | 1  |

<sup>&</sup>lt;sup>a</sup>Leftmost octet is the first received

. . .

#### 65.1.2.4.2 LLID

The third and fourth octets following the SPD contain the mode, <u>logical\_group\_id</u> and logical\_link\_id values. These values are acted upon differently for OLTs and ONUs.

If the device is an OLT then the following comparison is made:

- a) the received mode bit and logical\_group\_id is are ignored

- b) if the received logical\_link\_id value matches 0x7FFF and an enabled MAC exists with a logical\_link\_id variable with the same value then the comparison is considered a match to that MAC.

- c) if the received logical\_link\_id value is any value other than 0x7FFF and an enabled MAC exists with a mode variable with a value of 0 and a logical\_link\_id variable with a value matching the received logical link id value then the comparision is considered a match to that MAC.

If the device is an ONU then the following comparison is made:

- a) if the received mode bit is 0, the received logical group id value matches one of the logical group id variables, and the received logical\_link\_id value matches the logical\_link\_id variable then the comparison is considered a match;

- b) if the received mode bit is 1, the received logical group id value matches one of the logical group id variables, and the received logical\_link\_id value doesn't match the logical\_link\_id variable, or the received logical\_link\_id matches 0x7FFF, then the comparison is considered a match.

. . .

<sup>&</sup>lt;sup>b</sup>This octet may be missing per 1000BASE-X PCS transmit state diagram (see CROSS REF Figure 36-5)

<sup>&</sup>lt;sup>c</sup>SPD field

<sup>&</sup>lt;sup>d</sup>First octet of LLID field

esecond octet of LLID field

<sup>&</sup>lt;sup>f</sup>CRC8 field

<sup>&</sup>lt;sup>9</sup>D0 through D7 is the first octet of the PDU (first octet of the Destination Address)