Proposed Changes to IEEE Std 802.3, Sub-clauses 25.4.5 and 25.4.7, to address the need for reduced Open Circuit Inductance in Ethernet Magnetics

Nathan Tracy, <u>ntracy@te.com</u> Erich Eminhizer, <u>erich.eminhizer@te.com</u>

August 2011

#### Overview

The Open Circuit Inductance (OCL) requirement was also revised to account for the increased DC bias current due to PoE+ currents and cable imbalance. The revision allowed for lower inductance transformers to be used and based the performance of the transmitter on signal characteristics (droop) rather than on the inductance alone (350µH at 8mA bias per TP-PMD (ANSI INCITS 263-1995 R2005)).

Baseline Wander tests using 100BASE-TX PHYs and low OCL transmitters were conducted to ensure interoperability for modern PHYs. The droop specification was accepted as part of the IEEE Std 802.3at amendment, applying specifically to PoE+Transmitters.

# **Overview of Proposed Change**

Proposal is to adopt the alternative droop test, as defined in Sub-Clause 25.4.5 for Type 2 transmitters, for all 100BASE-TX transmitters. Transmitters will be required to meet either the droop measurement or the 350uH Open Circuit Inductance requirement specified in 9.1.7 of TP-PMD.

The proposed changes offer the following advantages:

- Increases design flexibility by removing over-specified inductance requirement for BASE-T Ethernet systems

- Cost avoidance through the use of advanced manufacturing techniques and new industry standard processes

- Allows for implementation of new materials and designs providing:

- Improved DPPM (Defective Parts Per Million)

- Improved performance consistency

- Potential to simplify PHY design

- Improved EMI performance

NOTE: all referenced paragraph numbers in this document are from draft specification IEEE P802.3REVTM/2.0 July 2011

# Impact on 100BASE-TX

For 100BASE-TX, the original requirement of 350µH at 8mA bias was included to mitigate baseline wander (BLW), which could cause incorrect decoding of signals given long runs of steady state signal (+1 or -1).

As early as 1997, PHY vendors began implementing BLW compensation circuitry in their PHY transceivers.

PHY vendors have conducted tests and confirmed that PHYs released after 2003 equipped with transformers having an OCL of 120µH will interoperate and achieve a BER of 10<sup>-8</sup> or better while transmitting data with BLW. These results were obtained with different cable lengths, up to 100+ meters.

- (Source: <u>http://ieee802.org/3/at/public/2008/09/schindler 1 0809.pdf</u>.)

## Impact on 1000BASE-T

1000BASE-T is already designed to accommodate low OCL transmitters.

To pass the droop test in 1000BASE-T, minimum inductance is calculated based on the time constant of the decaying waveform. Therefore, to meet the 73% droop in 500ns:  $e^{-500ns/t} = .73 \implies t = 1.6\mu s = L/R = L/50 \implies L = 80\mu H$

#### **Industry Standards**

- The following standards are affected:

- IEEE Std 802.3<sup>™</sup>-2008

- − IEEE Std 802.3at<sup>TM</sup>-2009 (Amendment to IEEE Std 802.3<sup>TM</sup>-2008)

- IEEE P802.3REV<sup>TM</sup>/2.0 July 2011

- Section affected:

- Section 25: Physical Medium Dependent (PMD) sublayer and baseband medium, type 100BASE-TX

The proposed amendment removes the contingency that the transmitter be a Type 2 (PoE+) PSE or PD to apply the time constant requirement of sub-clause 25.4.5.1. The option remains to meet the legacy requirement of 350µH for all transmitters.

Specifically, the change is as follows:

- 1. Change sub clause 25.4.5:

- A receiver in a Type 2 Endpoint PSE or Type 2 PD (see Clause 33) shall meet the

- -requirements of 25.4.7. A transmitter in a Type 2 Endpoint PSE or Type 2 PD

- delivering or accepting more than 13.0 W average power Transmitters shall meet either the Open Circuit Inductance (OCL) requirement in 9.1.7 of TP-PMD, or meet the requirements of 25.4.5.1.

Additional changes modify the existing language to remove the Type 2 dependency.

- 2. Delete the word 'Type 2' in title for Figure 25-1 and 25-2 in section 25.4.5.1 Equivalent system time constant.

- 3. Change sub-clause 25.4.7:

#### 25.4.7 Addition to 10.1, "Receiver"

Differential voltage signals generated by a remote transmitter that meets the specifications of Clause 25; passed through a link specified in 25.4.8; and received at the MDI of a 100BASE-TX PMD in a Type 2 Endpoint PSE or a Type 2 PD shall be translated into one of the PMD\_UNITDATA.indicate messages with a bit error ratio less than 10–9 after link reset completion.

Bias current is defined for Type 1 and non-PoE transmitters:

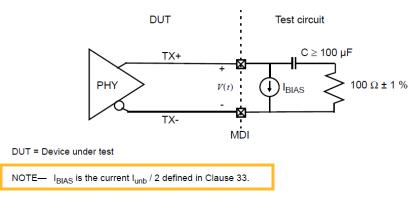

4. Change the Note for Figure 25-1 in section 25.4.5.1

NOTE-For transmitters in a Type 1 or Type 2 PSE or PD, IBIAS is the current lunb / 2 defined in Clause 33. For transmitters not in a Type 1 or Type 2 PSE or PD, IBIAS is not required.

Figure 25–1—Type 2 system time constant test circuit

(Figure shown is from IEEE Std 802.3at-2009)

The bias current applied during the time constant measurement is based on DC cable imbalance.

- For Type 2 PSE/PDs, I<sub>BIAS</sub> remains I<sub>UNB</sub> / 2 as determined in the existing IEEE Std 802.3at amendment. I<sub>UNB</sub> is based on worst-case pair imbalance at peak current loads (3% \* I<sub>PEAK</sub>), approximately 10.3mA.

- Type 1 PSE/PDs will also use  $I_{UNB}$  / 2, with  $I_{UNB}$  as specified in Table 33-11 (3% \*  $I_{CABLE}$ )

- Non-PoE transmitters have no added bias current due to DC cable imbalance.

| Item | Parameter                                            | Symbol            | Unit | Min   | Max                         | PSE<br>Type | Additional information                                                                                                                                     |

|------|------------------------------------------------------|-------------------|------|-------|-----------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | Turn on rise time                                    | T <sub>Rise</sub> | μs   | 15.0  |                             | 1, 2        | From 10 % to 90 % of<br>the voltage difference at<br>the PI in POWER_ON<br>state from the beginning<br>of POWER_UP.                                        |

| 15   | Tum off time                                         | Toff              | s    |       | 0.500                       | 1, 2        | See 33.2.7.8.                                                                                                                                              |

| 16   | Turn off voltage                                     | V <sub>Off</sub>  | v    |       | 2.80                        | 1, 2        | See 33.2.7.9.                                                                                                                                              |

| 17   | DC MPS current                                       | I <sub>Hold</sub> | А    | 0.005 | 0.010                       | 1, 2        | See 33.2.9.1.2.                                                                                                                                            |

| 18   | PD Maintain Power<br>Signature dropout time<br>limit | T <sub>MPDO</sub> | s    | 0.300 | 0.400                       | 1, 2        | See 33.2.9.                                                                                                                                                |

| 19   | PD Maintain Power<br>Signature time for              | T <sub>MPS</sub>  | s    | 0.060 |                             | 1, 2        | See 33.2.9.                                                                                                                                                |

|      | vanony                                               |                   |      |       |                             |             |                                                                                                                                                            |

| 20   | Current unbalance                                    | I <sub>unb</sub>  | A    |       | 3 % ×<br>I <sub>Cable</sub> | 1           | See 33.2.7.11, 33.4.8.<br>NOTE—For practical<br>implementations, it is<br>recommended that<br>Type 1 PSEs support<br>Type 2 I <sub>unb</sub> requirements. |

|      |                                                      |                   |      |       | 3 % ×<br>I <sub>Peak</sub>  | 2           |                                                                                                                                                            |

#### Table 33–11—PSE output PI electrical requirements for all PD classes, unless otherwise specified *(continued)*

(Table shown is from IEEE Std 802.3at-2009)

#### Conclusion

The alternative droop requirement has been fully implemented in the IEEE Std 802.3at standard and should be extended to cover all BASE-T systems.

This change will allow for the next generation of highly automated magnetic solutions to be evaluated and implemented on all BASE-T Ethernet products

This change will benefit the entire Ethernet industry by allowing for advances in magnetic solutions that will ultimately improve system performance, DPPM, and mitigate escalating cost of labor rate and material increases

For off line discussions on this proposed change, please contact Nathan Tracy, <u>ntracy@te.com</u> and Erich Eminhizer, <u>erich.eminhizer@te.com</u>